Práctica 8. Introducción al VHDL sintetizable. Herramientas de

Anuncio

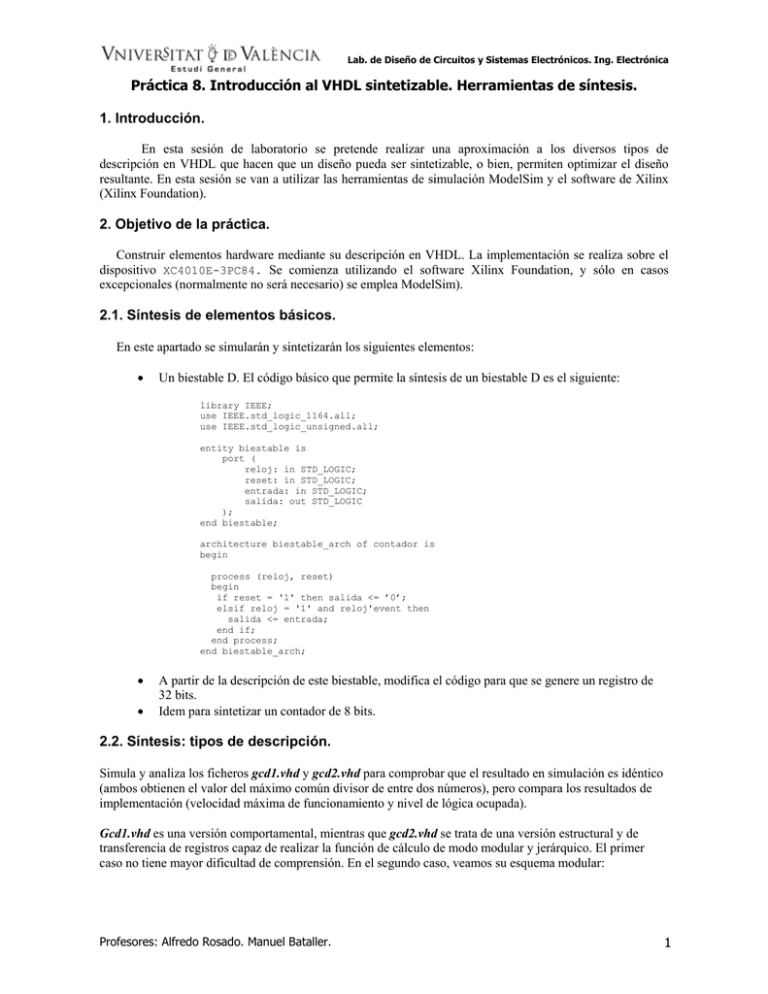

Lab. de Diseño de Circuitos y Sistemas Electrónicos. Ing. Electrónica Práctica 8. Introducción al VHDL sintetizable. Herramientas de síntesis. 1. Introducción. En esta sesión de laboratorio se pretende realizar una aproximación a los diversos tipos de descripción en VHDL que hacen que un diseño pueda ser sintetizable, o bien, permiten optimizar el diseño resultante. En esta sesión se van a utilizar las herramientas de simulación ModelSim y el software de Xilinx (Xilinx Foundation). 2. Objetivo de la práctica. Construir elementos hardware mediante su descripción en VHDL. La implementación se realiza sobre el dispositivo XC4010E-3PC84. Se comienza utilizando el software Xilinx Foundation, y sólo en casos excepcionales (normalmente no será necesario) se emplea ModelSim). 2.1. Síntesis de elementos básicos. En este apartado se simularán y sintetizarán los siguientes elementos: • Un biestable D. El código básico que permite la síntesis de un biestable D es el siguiente: library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity biestable is port ( reloj: in STD_LOGIC; reset: in STD_LOGIC; entrada: in STD_LOGIC; salida: out STD_LOGIC ); end biestable; architecture biestable_arch of contador is begin process (reloj, reset) begin if reset = '1' then salida <= ’0’; elsif reloj = '1' and reloj'event then salida <= entrada; end if; end process; end biestable_arch; • • A partir de la descripción de este biestable, modifica el código para que se genere un registro de 32 bits. Idem para sintetizar un contador de 8 bits. 2.2. Síntesis: tipos de descripción. Simula y analiza los ficheros gcd1.vhd y gcd2.vhd para comprobar que el resultado en simulación es idéntico (ambos obtienen el valor del máximo común divisor de entre dos números), pero compara los resultados de implementación (velocidad máxima de funcionamiento y nivel de lógica ocupada). Gcd1.vhd es una versión comportamental, mientras que gcd2.vhd se trata de una versión estructural y de transferencia de registros capaz de realizar la función de cálculo de modo modular y jerárquico. El primer caso no tiene mayor dificultad de comprensión. En el segundo caso, veamos su esquema modular: Profesores: Alfredo Rosado. Manuel Bataller. 1 Lab. de Diseño de Circuitos y Sistemas Electrónicos. Ing. Electrónica Analiza y explica detenidamente el funcionamiento del sistema y simula su comportamiento explicando con un ejemplo concreto la evolución de los estados hasta producir un resultado válido. 3. Documentación a entregar. Entrega de los ficheros con cada uno de los módulos VHDL del apartado 2.1 y simulación y explicación del apartado 2.2 (tanto de gcd1 como gcd2). Profesores: Alfredo Rosado. Manuel Bataller. 2