( ( BC AC AB C)BA(AB XY )YX(XY + +

Anuncio

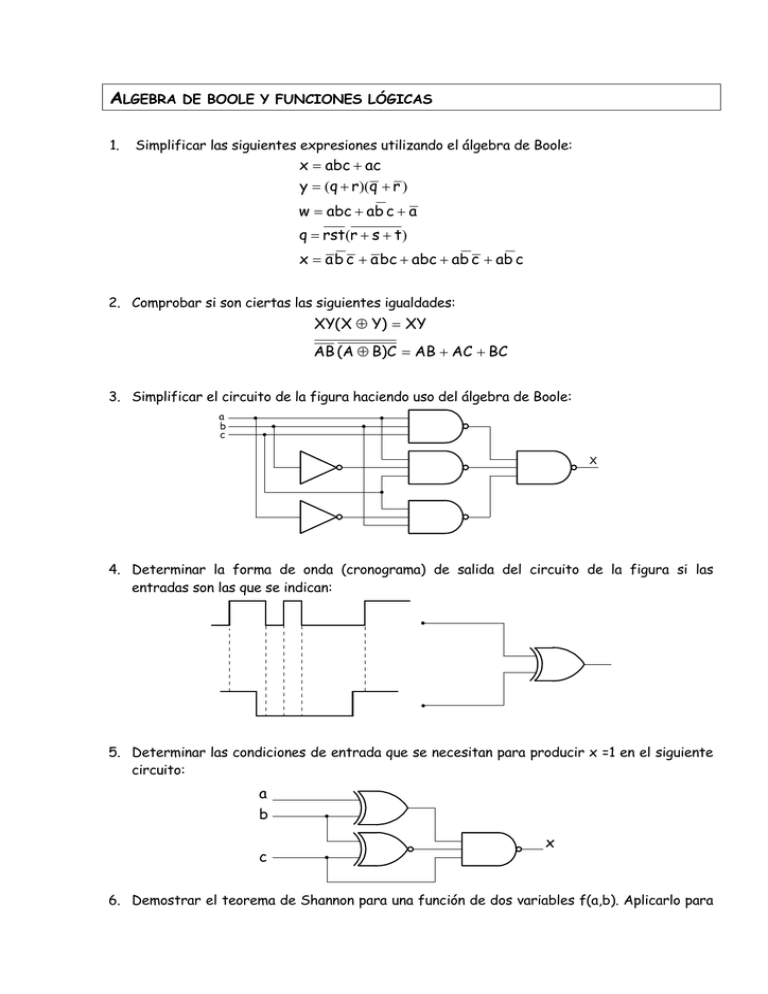

ALGEBRA

1.

DE BOOLE Y FUNCIONES LÓGICAS

Simplificar las siguientes expresiones utilizando el álgebra de Boole:

x = abc + ac

y = (q + r)(q + r )

w = abc + ab c + a

q = rst(r + s + t)

x = a b c + a bc + abc + ab c + ab c

2. Comprobar si son ciertas las siguientes igualdades:

XY(X ⊕ Y) = XY

AB (A ⊕ B)C = AB + AC + BC

3. Simplificar el circuito de la figura haciendo uso del álgebra de Boole:

a

b

c

X

4. Determinar la forma de onda (cronograma) de salida del circuito de la figura si las

entradas son las que se indican:

5. Determinar las condiciones de entrada que se necesitan para producir x =1 en el siguiente

circuito:

a

b

c

x

6. Demostrar el teorema de Shannon para una función de dos variables f(a,b). Aplicarlo para

Informática Básica

Circuitos Combinacionales

obtener la función f( a, b, c) = a b c + abc + a bc en forma de producto de sumas.

7. Simplifica las expresiones algebraicas siguientes:

Algebraicamente: f = y z + x y + x z + yz

Mediante Karnaugh: f = (A + B)(A + B + C )(B + C + D)(A + B + C + D)

8. Se define la operación ‘ # ‘ sobre dos variables lógicas a y b de la forma:

a # b = a ⋅b + a ⋅b

Si c = a # b, determinar cuál de las siguientes identidades es válida:

1)

a=b#c

2)

(a # b) c = 1

9. Utilizando los axiomas y postulados de álgebra de Boole comprobar si son ciertas las

siguientes igualdades:

1. −

a + a ( a b + b c) = a + b + c

2. −

a b + b c + a c = ab + a c

3. −

ab + a c + b c d = ab + a c

10. Mediantes las técnicas del álgebra de Boole, simplificar las siguientes expresiones:

(

) ( )

F (a, b, c, d) = [ab(c + bd) + ab]cd

F1 (a, b, c) = ab + a b + c + b b + c

2

F3 (a, b, c) = abc + a b c + a bc + a b c

F4 (a, b, c) = ab + ac + a b c

11. Utilizando tablas de Karnaugh encontrar la expresión mínima en forma de suma de

productos y de producto de sumas para cada una de las siguientes expresiones:

F1 = def + d ef + d e f

F2 = a b(c d + c d) + ab(c d + c d) + ab c d

F3 = (a b + ab )(cd + cd )

F4 = a b + ab + c d + cd

F5 = ∑ (1,2,6,7,8,10,12,13,15)

4

2

Informática Básica

Circuitos Combinacionales

12. Obtener la expresión mínima en forma de producto de sumas y de suma de productos de

las siguientes funciones:

F = ∑ (0,3,7 ,10,11,12,13,14,26,27 )

5

G = ∏ (1,2,4,8,15,23,27 ,29,30)

5

13. Sea F =

∑ (0,3,4,6,7) . Implementar un circuito que la genere con el mínimo número de

3

puertas lógicas:

a)AND, OR, NOT.

b)NAND.

c)NOR.

14. Diseñar un circuito que proporcione en su salida un nivel alto cuando el equivalente decimal

de la combinación binaria de 4 bits introducida en sus entradas sea múltiplo de 2 ó 3

(considerese el 0 como múltiplo), utilizando el mínimo número de puertas:

De cualquier tipo.

NAND de 3 entradas como máximo

NOR de 3 entradas como máximo

NAND y NOR de 2 entradas.

15. Sea la función lógica de 4 variables:

F = a d + bd + abc d + a bcd + a bcd + acd + bd + a bc d .

Simplificarla e implementarla empleando el menor número posible de puertas NAND.

16. Dado el circuito que se muestra en la figura, se pide:

Obtener la expresión S=f(x,y,z).

Indicar un esquema más optimizado, empleando puertas AND/OR/NOT

Si solo podemos emplear puertas NAND o NOR, indicar cuál de ambas soluciones

empleará menor número de puertas.

Si el tiempo de retraso de una puerta genérica es de 100ns, ¿Cuál es el tiempo de

respuesta del circuito original y del optimizado?

3

Informática Básica

X

Y

Circuitos Combinacionales

Z

S

17. Una empresa fabrica tres modelos de artículos. A su vez, cada uno de ellos se fabrica en

dos tamaños (P:pequeño y G:grande), y en dos colores (B:blanco y N:negro).

Para identificar numéricamente un artículo dado, se le ha dotado de una etiqueta

identificativa compuesta por cuatro dígitos binarios, según el siguiente esquema:

<Nº de articulo (1,2,3), Tamaño (P:0, G:1), Color (B:0, N:1)>.

Ejemplo: Articulo 2 (2->10), Grande (G->1), Blanco (B->0) -> Etiqueta 1010.

Los artículos deben ser almacenados en 4 cajas distintas, con arreglo a la siguiente

distribución:

Caja nº0: Articulos del nº1, grandes, de cualquier color.

Caja nº1: Artículos nº 1, 2 ó 3, pequeños y blancos.

Caja nº2: Artículos nº 2 y 3, grandes y negros.

Caja nº3: Los que no están incluidos en las cajas anteriores.

Diseñar un circuito combinacional, empleando el mínimo número de puertas NAND e

inversores, que tomando como entradas el código identificativo de un artículo proporcione

en sus salidas el número de caja codificada en binario donde éste debe ser almacenado.

Si el retardo de propagación de una puerta es de 20 ns, ¿Cuál es el tiempo máximo de

respuesta del circuito obtenido?

18. Comprobar mediante las propiedades del álgebra de Boole si las puertas OR-EXCLUSIVA

y NOR-EXCLUSIVA son asociativas.

19. El Circuito Iintegrado 7451 que contiene dos estructuras AOI

como la representada en la figura. ¿Podríamos implementar una

función cualquiera utilizando solamente circuitos integrados de

este tipo? En caso negativo, justifica la respuesta. En caso

afirmativo construye una puerta AND, una puerta OR y un

4

Informática Básica

Circuitos Combinacionales

inversor.

20. Dada la función:

F = a b(c + d ) + ab(a + b)c + d a + a bc(b + d ) + a + c + d

•

•

•

Simplificarla y obtener la expresión mínima que nos permitiría implementarla:

a) Con puertas básicas.

b) Con Puertas NAND de 3 entradas como máximo.

c) Con puertas NOR

Implementarla exclusivamente con multiplexores de 4 entradas de información e

inversores.

Implementarla con dos decodificadores de 3 a 8 líneas dotados de entrada de

habilitación.

21. Comprobar mediante las propiedades del álgebra de Boole si son ciertas las siguientes

igualdades:

a⊕b⊕c⊕d =a⊕b⊕c⊕d

ab ⊕ bc ⊕ ac = a b + a c + b c

ab ⊕ bc ⊕ ac = ab + ac + bc

22. Obtén la función de salida del circuito de la figura. Indica su expresión simplificada

utilizando el álgebra de Boole.

5

Informática Básica

Circuitos Combinacionales

CIRCUITOS COMBINACIONALES

23. El circuito de la figura representa un multiplicador binario para números de dos bits (x1x0

e y1y0). Diseñar dicho multiplicador.

x1

x0

y1

y0

Circuito

Multiplicador

Z0

z1 Z1

Z

z0 2

Z3

24. Una máquina copiadora está dotada de 4 interruptores de control (S1, S2, S3, S4) situads

en diferentes puntos a lo largo del camino que recorre el papel. Cada interruptor está

normalmente abierto y, cuando el papel pasa sobre él, el interruptor se cierra. Es

imposible que los interruptores S1 y S4 se cierren al mismo tiempo. Diseñar un circuito

lógico mínimo que indique a su salida que dos o más interruptores están cerrados

simultáneamente. Utilícense únicamente puertas NAND.

25. Cuatro tanques de gran capacidad de una planta química contienen diferentes líquidos

sometidos a calentamiento. Se utilizan sensores de nivel de líquido para detectar si el

nivel de los tanques A y B excede de un nivel predeterminado. Los sensores de

temperatura de los tanques C y D detectan cuando la temperatura estos tanques

desciende de un nivel prescrito. Las salidas de los sensores de nivel de líquido se ponen a

0 cuando el nivel es satisfactorio y a 1 en caso contrario. Asimismo, las salidas de los

sensores de temperatura se ponen a 0 con temperatura adecuada y a 1 si es demasiado

baja. Diseñar un circuito lógico mínimo que detecte si el nivel del tanque A ó B es

demasiado alto al mismo tiempo que la temperatura en tanque C o en el D es demasiado

baja. Utilícense únicamente puertas NOR.

26. Se dispone de un motor eléctrico que se emplea para mover el brazo de un robot. Para

saber cual es la posición en que se encuentra dicho brazo con respecto al eje horizontal,

se ha dispuesto un elemento sensor que envía los siguientes códigos al circuito de control:

de

de

de

de

de

de

0º a 30º

30º a 60º

60º a 90º

90º a 120º

120º a 150º

150º a 180º

0000

1110

1010

0001

1001

0011

de 180º a 210º

de 210º a 240º

de 240º a 270º

de 270º a 300º

de 300º a 330º

de 330º a 360º

1011

0111

1000

1101

1100

0100

Diseñar un circuito mínimo que en función de la información proporcionada por el sensor

indique en qué cuadrante de la circunferencia se encuentra el brazo. Implementese

solamente con puertas NAND de dos entradas.

27.

Dados dos números de dos bits A=a0a1 y B=b0b1 deben compararse por medio de una

función de cuatro variables f(a0,a1,b0,b1). La función f debe tener el valor 1 siempre que

6

Informática Básica

Circuitos Combinacionales

V(A)≤V(B), en donde V(x)=x020+x121 para cualquier número de dos bits. Considérese que

las variables A y B son tales que |V(A)-V(B)|≤2. Se pide:

Diseñar un circuito lógico mínimo que realiza esta función.

Implementarlo con puertas NOR de dos entradas.

28.

Diseñar un circuito combinacional lo más simplificado posible que obtenga en sus salidas

el complemento a 9 del dígito BCD colocado en sus entradas.

29.

Sintetizar una función f(a,b,c,d,e) que tome el valor lógico 1 cuando el número de

variables que está en estado 1 es superior al que se encuentra en estado 0. Nunca puede

haber más de tres variables en estado 1 simultáneamente. Determinar:

La expresión mínima de la función f.

Realizar la expresión del apartado a con puertas NAND de tres entradas máximo.

¿Se podría implementar la función con un multiplexor de 3 entradas de selección?

30.

Diseñar un circuito combinacional para abrir una puerta, de tal forma que solo debe

abrirse cuando el equivalente decimal del número binario de 5 bits introducido mediante

los microinterruptores que se encuentran ubicados en un panel de control sea primo.

Considerar el 0 como primo.

31.

Un proceso químico posee cuatro indicadores de temperatura en un punto P, cuyas

salidas T1, T2, T3 y T4 adoptan dos niveles de tensión bien diferenciados según la

temperatura sea menor, o mayor-igual que t1, t2, t3 y t4 respectivamente (siendo

t1<t2<t3<t4).Se asigna el valor 0 al nivel de tensión correspondiente a una temperatura

inferior a"t" y el valor 1 al nivel correspondiente a una temperatura superior o igual a

"t". Se desea generar una señal que adopte un nivel de tensión 1 si la temperatura está

comprendida entre t1 y t2 ó entre t3 y t4, y el nivel lógico 0 en caso contrario. Se pide:

Las expresiones algebraicas mínimas de producto de sumas y de sumas de productos.

Realizar la función f con un decodificador y

T1

con puertas NAND.

T2

P

f

T3

T4

32.

Se desea diseñar el operador de funciones

lógicas de un computador que trata datos de

indicadores

7

Informática Básica

Circuitos Combinacionales

dos bits. Las operaciones lógicas que se desea dotar a este computador son la AND y la

OR. Diséñese dicho operador teniendo en cuenta que a sus entradas llegan datos a

través de 4 líneas a1a0 b1b0 y además, una señal AND/OR generada por la unidad de

control que permite escoger la operación a realizar. Se requiere realizar la

implementación de dicho circuito utilizando puertas NAND y NOR de 2 entradas.

33. Diseñar un circuito que tenga por entrada un código Johnson de 5 bits y proporcione a

su salida el número equivalente en BCD Aiken.

8

Informática Básica

Circuitos Combinacionales

CIRCUITOS COMBINACIONALES (II)

34.

Diseñar mediante un decodificador de 4 a 16 líneas un circuito capaz de realizar la suma

de 2 números de dos bits, con salida de suma y acarreo.

35.

Diseñar un convertidor de código que acepte números binarios con signo, codificados en

signo magnitud de 5 bits y proporcione una salida codificada en complemento a 2.

36.

Diseñar un circuito combinacional que convierta el código BCD Aiken o BCD exceso 3 a

código BCD natural. El código de entrada se seleccionará mediante una variable de

entrada E/S .

37.

Se desea diseñar un circuito que haga funcionar la alarma de un coche cada vez que los

asientos del conductor y/o su acompañante estén ocupados pero éstos no se hayan

abrochado los cinturones de seguridad cuando arranca el automóvil. La presencia del

conductor y de su acompañante son generadas por sensores de presión colocados en los

asientos, mientras que la señal de encendido viene directamente del contacto. Diseñar

dicho circuito empleando únicamente puertas NAND.

38.

Un código BCD exceso 3 se transmite a un receptor lejano. Se desea dotar al receptor

de un circuito detector de errores que sea capaz de examinar el código recibido e

indicar si es válido. Diseñar dicho circuito haciendo uso de puertas NOR de dos

entradas.

39.

El circuito de la figura representa un detector de magnitud relativa, que toma dos

números binarios de tres bits x1x2x3 e y1y2y3, y determina si son iguales y, si no lo son,

cuál de ellos es el mayor. Las tres salidas se definen como sigue:

M=1 sólo si los dos números de entrada son iguales.

N=1 sólo si x1x2x3 es mayor que y1y2y3.

P=1 sólo si y1y2y3 es mayor que x1x2x3.

Diseñar el circuito lógico de dicho comparador.

Sugerencia: Utilícense dos tablas de Karnaugh de 5 variables (aunque la solución que

se obtendrá no será mínima).

x1

x2

x3

y1

y2

y3

40.

Detector de

Magnitud Relativa

M

N

P

En un laboratorio de química se trabaja con 4 productos A, B, C y D. Cada uno de ellos

pueden encontrarse en uno de los dos recipientes de almacenamiento de que se dispone.

De vez en cuando es conveniente cambiar uno o más productos de un recipiente a otro, la

9

Informática Básica

Circuitos Combinacionales

naturaleza de los productos es tal que es peligroso guardar B y C juntos a menos que A

esté en el mismo recipiente. También es peligroso almacenar C y D juntos a menos que A

esté presente.

Escribir una expresión para una variable lógica Z que tendrá valor Z=1 para cada

situación peligrosa de almacenamiento. Implementar dicha función mediante un

multiplexor.

41.

Para automatizar el riego de un campo de fútbol se han instalado bajo el césped 3

sensores de humedad que detectan cuando ésta desciende por debajo del nivel

preestablecido. Además se dispone de 2 interruptores mediante los que se puede

configura la puesta en marcha del sistema de riego según las siguientes normas:

Si sólo un interruptor está activado se conectará el sistema de riego cuando hayan 1 ó

2 sensores activos.

Si ningún interruptor está activo se conectará el sistema de riego cuando hayan 2 ó 3

sensores activos.

Si los dos interruptores están activados se conectará el sistema cuando sólo haya un

sensor activo.

Diseñar un sistema mínimo que indique cuando el sistema de riego debe activarse.

Impleméntalo utilizando únicamente puertas NOR.

42.

Diseñar un circuito que conectado adecuadamente al

de la figura, sea capaz de detectar la obtención de

un resultado incorrecto (overflow) en la salida de un

sumador/restador para números de tres bits en C2

complemento a dos.

B2 B1 B0

A2 A1 A0

Sumador/Restador

S/R

S2 S1 S0

43.

En una planta química se dispone de dos depósitos (Ay B) que se deben mantener bajo

unas condiciones determinadas de presión y temperatura. Para obtener dichas

condiciones se ha instalado un dispositivo regulador que actúa simultáneamente sobre

ambos depósitos. Cada depósito dispone de un sensor de temperatura (TA y TB) y uno

de presión (PA y PB) cuyas salidas no se activan (toman el valor 0) cuando las

condiciones son correctas. Diseñar un circuito lógico que tomando la información

proporcionada por los sensores le indique al dispositivo regulador las actuaciones

necesarias según el siguiente criterio:

Siempre que PA o PB estén activados y no lo estén TA o TB actuará sobre la presión.

Siempre que PA y PB estén activos se actuará sobre la presión.

Siempre que TA y TB estén activos se actuará sobre la temperatura.

Siempre que TA o TB estén activos y no lo estén PA y PB se actuará sobre la

temperatura.

Implementar dicho circuito utilizando exclusivamente multiplexores de cuatro

entradas de información e inversores.

10

Informática Básica

Circuitos Combinacionales

Dispositivo

Regulador

Depósito A

TA

P

T

Depósito B

PA

TB

PB

Circuito Lógico

44.

Diseñar un circuito combinacional que operando sobre palabras de tres bits realice,

según indiquen unas entradas de control, las operaciones de desplazamiento a la

derecha, desplazamiento a la izquierda, transferencia y complemento a uno.

Implementar el diseño mediante:

a) Decodificadores.

b) Única y exclusivamente puertas NAND de 3 entradas.

45.

La iluminación de una discoteca está constituida por la combinación de luces de tres

colores (rojo, azul y verde) y por un dispositivo de rayo láser. El sistema dispone de

interruptor general E de forma que sólo si E=1 el sistema funciona. Las tres luces están

controladas por cuatro interruptores D, C, B, A , de forma que :

La luz roja se encenderá siempre que esté activado el interruptor A ó si está activado

B y no lo está C.

La luz azul se encenderá cuando B no esté activado o cuando estándolo D no lo está A.

La luz verde se enciende si no está activado C, o si no lo está A y lo está B, o si está

D.

El rayo láser se pone en funcionamiento cuando hay un número impar de luces

encendidas.

Se pide:

a) Tabla de verdad que indique el funcionamiento del sistema.

b) Implementar la función verde exclusivamente con puertas NAND de dos entradas.

c) Implementar la función roja empleando únicamente multiplexores de cuatro

entradas de información con entrada de habilitación activa por nivel alto.

d) Implementar la función azul con decodificadores de tres entradas que disponen

además de otras dos de habilitación E1 y E2 (el dispositivo sólo funciona cuando

E1=E2=1). Pueden emplearse también las puertas necesarias.

e) Implementar el rayo láser utilizando únicamente semisumadores. Hacer un esquema

de bloques que corresponda al funcionamiento de todo el sistema

46.

Se desea diseñar un sistema que leyendo la información contenida en la banda magnética

de las tarjetas de identificación que poseen los alumnos les indique que aula tienen

asignada. La información a manejar es la siguiente:

carrera en la que están matriculados ( I.I., I.T.I.G. e I.T.I.S.)

11

Informática Básica

Circuitos Combinacionales

grupo al que pertenecen (A, B, C, D)

si es repetidor o no lo es.

Sabiendo que hay siete aulas, diseñar el sistema que a partir de dicha información

proporcione en sus salidas el aula correspondiente al alumno, según el siguiente

criterio:

Aula A1: carrera ITIG, grupo A, repetidores o no.

Aula A2: carreras II e ITIS, grupos A o B, no repetidores.

Aula A3: carrera ITIG, grupo C, repetidores o no y carrera II, grupo D,

repetidores.

Aula B0: carrera II, grupo D, no repetidores.

Aula B1: carrera ITIG, grupo D, repetidores.

Aula B2: todos los de la carrera ITIG no incluidos en las anteriores.

Aula B3: todos los demás.

Teniendo en cuenta que el sistema diseñado debe ser mínimo, obtener:

Las expresiones algebraicas en forma de suma de productos y producto de sumas.

La implementación de dicho sistema mediante multiplexores de tres entradas de

selección.

47.

En el circuito de la figura, a,b,c y d son interruptores cuya posición de activado se indica

con un ‘1’. Las salidas del primer bloque realizan las siguientes funciones:

F1=1 si no hay dos interruptores seguidos activados.

F2=1 si hay dos o más interruptores activados.

F3=1 si alguno de los interruptores extremos está activado.

F3

a

b

F2

Bloque

c

1

F1

d

Bloque

2

M

N

Las salidas del segundo bloque codifican en binario el número de lámparas encendidas

que hay en la entrada.

Diseñar el primer bloque utilizando únicamente NAND de 3 entradas e inversores.

Diseñar el segundo bloque utilizando únicamente NOR de 2 entradas.

Escribir las expresiones de M y N en su forma canónica de producto de sumas.

Implementar las funciones M y N empleando bloques como el de la figura y el menor

número posible de puertas lógicas.

E

0

1

1

1

1

C1

X

0

0

1

1

C0

X

0

1

0

1

S

1

A0

A1

A2

A3

A3 A2 A1 A0 E

C1

C0

S

12

Informática Básica

Circuitos Combinacionales

48.

Se desea diseñar una Unidad Aritmético-Lógica de n bits capaz de ejecutar

operaciones distintas sobre números expresados en complemento a 2. Para ello se ha

pensado utilizar operadores elementales de un bit y conectarlos entre si para obtener el

resultado deseado (n bits). Las operaciones que se quieren incluir son: Suma, Resta,

AND, OR, NOT y Transferencia. Plantear la solución mediante dos operadores, uno que

agrupe las operaciones aritméticas y el otro las restantes. Empléese para ello

exclusivamente puertas NAND, inversores y multiplexores de dos canales. Expresar en

una tabla las operaciones que realiza esta ALU en función de los valores que tomen las

entradas de control. Añadir la circuitería necesaria para incorporar una salida (Z) que se

active cuando el resultado de la operación efectuada sea cero.

49.

Utilizando todos los multiplexores de dos entradas de selección necesarios, implementar

la función f(x1,x2,x3,x4,x5) que se caracteriza por valer ‘1’ si y sólo si se cumple:

x1 + x2+ 2x3 + 2x4 + 3x5 ≥ 4

donde xi = {0,1} para i = 1, 2, 3, 4, 5 y las operaciones adición y multiplicación indicadas

son aritméticas.

10 l/s

80 l/s

50.

Un depósito de agua dispone de cuatro conductos

de entrada y otros tantos de salida. Cada uno de

los cuales controlado por una electroválvula que

20 l/s

40 l/s

permite o interrumpe el paso del agua. En la figura

se indica el caudal (en l/s) que puede circular por

cada uno de los conductos. Con el objetivo de que

no descienda el nivel del agua almacenada en el

60 l/s

10 l/s

depósito se desea diseñar un sistema electrónico

30 l/s

50 l/s

que tomando la información del estado de las

válvulas de salida (1=válvula abierta, 0=válvula cerrada) determine las pautas de

actuación sobre las válvulas de entrada. Teniendo en cuenta que nunca se abrirán tres o

más válvulas de salida a la vez:

a) Obténgase la tabla de verdad que representa el funcionamiento del sistema.

b) Simplificar por Karnaugh (de la forma más óptima) las funciones lógicas necesarias.

Supongamos que sólo dispusiéramos de puertas AND y NOR. Partiendo de las

expresiones deducidas en el apartado anterior, determinar cuáles serían las más

apropiadas para implementar cada función, si el objetivo fuera obtener circuitos con el

menor nivel de puertas posible y obtener las expresiones algebraicas de los circuitos

que deberíamos construir e indicar de qué nivel serían.

51.

Disponemos de un bloque combinacional que realiza la función lógica P, siendo:

P(X, Y) = X # Y = XY + X

Se pide:

Demostrar que esta función lógica no es conmutativa.

Demostrar que la función lógica P es un operador completo o universal (podemos

implementar cualquier circuito combinacional).

13

6

Informática Básica

52.

Circuitos Combinacionales

Obtener la expresión canónica, en forma de suma de productos, de la función lógica Z(A,

B, C) que realiza el circuito de la figura, y a partir de ella, el circuito más simple

realizado con puertas lógicas conocidas.

A

X

Y

P

X

Y

P

0

X

Y

P

X

Y

P

X

Y

P

Z

B

0

C

53.

Una de las codificaciones utilizadas en las cintas de papel perforado emplea los códigos

indicados en la siguiente tabla (los códigos están representados en octal). Se desea

analizar una cinta que contiene exclusivamente caracteres como los de esta tabla.

Diseñar un circuito mínimo que tomando como entradas estos códigos indique en su

salida si el carácter encontrado corresponde a una vocal, a una consonante o a un signo

de puntuación.

A

C

B

D

E

F

30

16

23

22

20

26

G

I

H

J

K

L

13

14

05

32

36

11

M

O

N

P

Q

R

07

03

06

15

35

12

S 24

U 34

T 01

V 17

W 31

X 27

Y 25

[Espacio] 00

Z 21

. 04

, 02

; 10

a) Implementar el circuito solamente con puertas NAND de 3 entradas como

máximo

b) Implementar el circuito con multiplexores de 3 entradas de selección.

14