Código VHDL. - Escuela Colombiana de Ingeniería

Anuncio

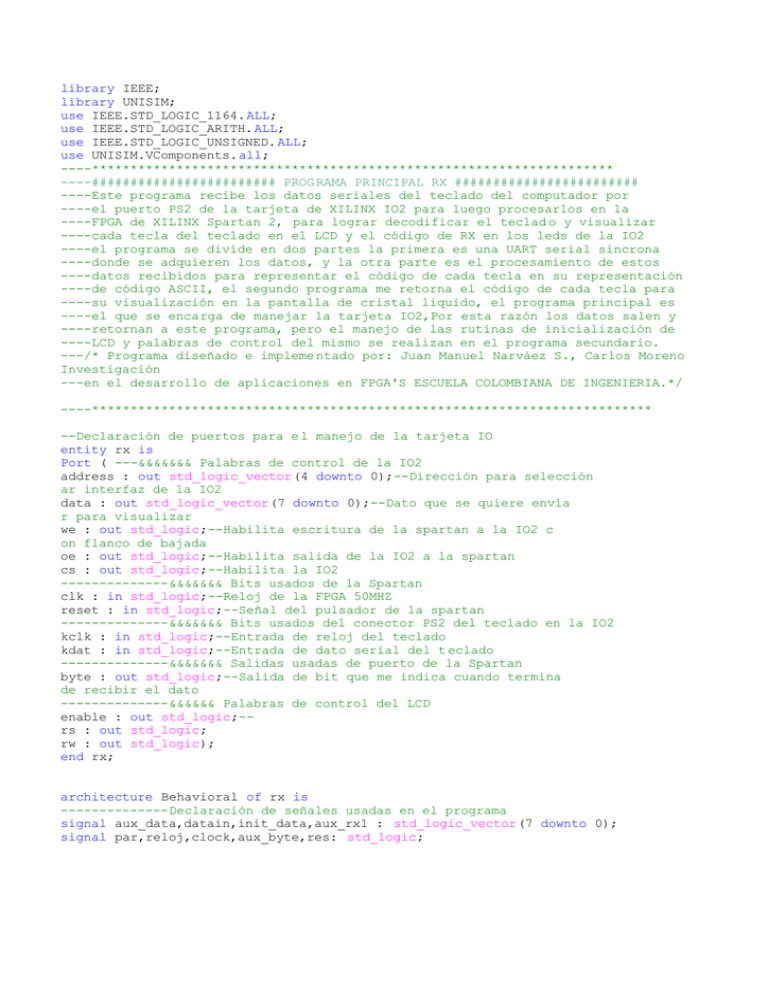

library IEEE; library UNISIM; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH. ALL; use IEEE.STD_LOGIC_UNSIGNED. ALL; use UNISIM.VComponents.all; ----******************************************************************** ----######################## PROG RAMA PRINCIPAL RX ######################## ----Este programa recibe los datos seriales del teclado del computador por ----el puerto PS2 de la tarjeta de XILINX IO2 para luego procesarlos en la ----FPGA de XILINX Spartan 2, para lograr decodificar el teclad o y visualizar ----cada tecla del teclado en el LCD y el código de RX en los leds de la IO2 ----el programa se divide en dos partes la primera es una UART serial sincrona ----donde se adquieren los datos, y la otra parte es el procesamiento de estos ----datos recibidos para representar el código de cada tecla en su representación ----de código ASCII, el segundo programa me retorna el código de cada tecla para ----su visualización en la pantalla de cristal liquido, el programa principal es ----el que se encarga de manejar la tarjeta IO2,Por esta razón los datos salen y ----retornan a este programa, pero el manejo de las rutinas de inicialización de ----LCD y palabras de control del mismo se realizan en el programa secundario. ---/* Programa diseñado e impleme ntado por: Juan Manuel Narváez S., Carlos Moreno Investigación ---en el desarrollo de aplicaciones en FPGA'S ESCUELA COLOMBIANA DE INGENIERIA.*/ ----************************************************************************* --Declaración de puertos para e l manejo de la tarjeta IO entity rx is Port ( ---&&&&&&& Palabras de control de la IO2 address : out std_logic_vector(4 downto 0);--Dirección para selección ar interfaz de la IO2 data : out std_logic_vector(7 downto 0);--Dato que se quiere envía r para visualizar we : out std_logic;--Habilita escritura de la spartan a la IO2 c on flanco de bajada oe : out std_logic;--Habilita salida de la IO2 a la spartan cs : out std_logic;--Habilita la IO2 --------------&&&&&&& Bits usados de la Spartan clk : in std_logic;--Reloj de la FPGA 50MHZ reset : in std_logic;--Señal del pulsador de la spartan --------------&&&&&&& Bits usados del conector PS2 del teclado en la IO2 kclk : in std_logic;--Entrada de reloj del teclado kdat : in std_logic;--Entrada de dato serial del t eclado --------------&&&&&&& Salidas usadas de puerto de la Spartan byte : out std_logic;--Salida de bit que me indica cuando termina de recibir el dato --------------&&&&&& Palabras de control del LCD enable : out std_logic;-rs : out std_logic; rw : out std_logic); end rx; architecture Behavioral of rx is --------------Declaración de señales usadas en el programa signal aux_data,datain,init_data,aux_rx1 : std_logic_vector(7 downto 0); signal par,reloj,clock,aux_byte,res: std_logic; signal signal signal signal signal signal count : std_logic_vector(3 downto 0); aux3 : std_logic_vector(2 downto 0); aux_output : std_logic_vector(9 downto 0); aux_counter : integer range 0 to 15; counter2 : integer range 0 to 103789; aux_rx : std_logic_vector(1 downto 0); --------------Declaracion de componentes component lcd is --/// Bloque que maneja las palabras de control del LCD y ---------//convierte datos a ASCII Port ( rx : std_logic_vector(1 downto 0); data_in : in std_logic_vector(7 downto 0); clock : in std_logic; fin : in std_logic; rs : out std_logic; enable : out std_logic; rw : out std_logic; data :out std_logic_vector(7 downto 0)); end component lcd; begin ---Asignaciones cs<='1';--Selecciona la tarjeta IO2 we<=clock or kdat;--Escribe de la IO2 a la FPGA con flanco de bajada del CLK oe<='0';----Desabilita pulsadores y swich de la IO2 solo visualiza address<="00100";----Habilita leds para visualización del dato RX byte<=aux_byte;-----Indica cuando termina RX data<=datain;-------Asigna el dato Rx por el teclado para visualizar en leds aux_rx1<="000000"&aux_rx; aux_counter<=conv_integer(count); ----Asigna el contador de binario a entero ---Conexiones de puerto --****** BUFFERS DE ENTRADA Siempre se deben usar para comunicación respad3: IBUFG PORT MAP (I=>reset,O=>res);---pulsador para reset siempre usa buffer respad: IBUF PORT MAP (I=>kclk,O=>reloj);----Reloj del teclado respad2: IBUFG PORT MAP (I=>clk,O=>clock);---Reloj de la Spartan --Conexion de palabras de control del LCD lcd2 : lcd port map (aux_rx,aux_data,clock,aux_byte,rs,enable,rw,datain); --Rx del teclado --******Recepciòn de datos comunicación sincroná, El dato llega sincronizado -- con flanco de reloj, y en formato bit de start(0), dato 8 bits, paridad par -- bit de stop (1), cuando el reloj esta en fl anco de bajada se recibe el dato, -- haciendo un conteo para saber el bit que es, start, dato, paridad o stop --además se hace conteo porque el teclado envía el dato tres veces recibe: process(reloj) begin if (res='0') then -- manejo de reset, res='0' hay recepción de dato if falling_edge(reloj)then case count is when "0000" =>-- bit de start if (kdat='0') then count<="0001"; aux_byte<='0'; end if; when "1010" => count<="0000";-- bit de stop, y reset del contador aux_byte<='1'; aux_rx<=aux_rx+"01";--conteo de datos recibidos if(aux_rx = "10")then aux_rx<="00"; end if; when others => aux_data(aux_counter-1)<=kdat;--deserialización del dato . count<=count+"0001"; end case; end if; else -- reset res = '1', dato y contadores en cero. aux_data<="00000000"; aux_byte<='0'; count<="0000"; end if; end process recibe; end Behavioral; --======================================================================== --########################## SEGUNDO PROGRAMA LCD ########################## --PRIMER SUBPROGRAMA MANEJO DE L CD Y CONVERCION DE CODIGO DE TECLADO A ASCII --======================================================================== library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH. ALL; use IEEE.STD_LOGIC_UNSIGNED. ALL; ----********************Este p rograma inicializa el LCD recibe ----el dato RX lo convierte del código de la tecla del teclado lo --- convierte a código ASCII y envía las palabras de control para visualizar y --- hacer funciones del LCD ----******************** ----Declaración de puerto entity lcd is Port ( rx : std_logic_vector(1 downto 0);---Contador de datos recibidos data_in : in std_logic_vector(7 downto 0);--Dato recibido Teclado clock : in std_logic;--Reloj de la FPGA fin : in std_logic;----Bit de termino de RX -----------Palabras de control del LCD rs : out std_logic; enable : out std_logic; rw : out std_logic; data :out std_logic_vector(7 downto 0)); end lcd; architecture Behavioral of lcd is ----------Declaracion de señales signal aux_data,other_data,shif: std_logic_vector(7 downto 0); signal bandera,aux4,aux_e,aux_rs,aux_e1,aux_rs1 : std_logic; signal bandera2 : std_logic:='0'; signal signal signal signal signal aux3 : std_logic_vector(2 downto 0); count_s : std_logic_vector(3 downto 0); aux2 : std_logic_vector(25 downto 0); aux_output : std_logic_vector(9 downto 0); flag_caps : std_logic_vector(1 downto 0);---Bandera Para mayúsculas -----------Declaración de componentes --/*Reloj dividido en frecuencia * 25 component counter is port( clock : in std_logic; output : out std_logic_vector(25 downto 0)); end component counter; begin ------Conexiones ang : counter port map(clock,aux2); rs<= '0' when bandera = '0' else aux_rs1 when bandera2='1' else aux_rs; rw<= '0'; data<=aux_output(7 downto 0) when bandera = '0' else shif when bandera2 ='1' else other_data; aux4<=aux2(23); aux_e1<=aux2(15); enable<=aux4 when bandera = '0' else aux_e1 when bandera2='1'else aux_e; -----Asigna las palabras según las palabras de control del LCD para que pueda ---------ejecutar -----Funciones especiales como corrimientos o asignar letras mayúsculas c_iniciar:---/**Contador para proceso de inicialización process(aux4) begin if(falling_edge(aux4))then aux3<=aux3+"001"; end if; end process c_iniciar; inicial:----/******Inicialización del lCD process(aux3) begin if(bandera='0')then if(aux3 = "000")then aux_output<="0000001000"; bandera<='0'; elsif(aux3 = "001")then aux_output<="0000111110"; bandera<='0'; elsif(aux3 = "010")then aux_output<="0000001111"; bandera<='0'; elsif(aux3 = "011")then aux_output<="0000000001"; bandera<='1'; end if; end if; end process inicial; visualiza: process(rx) begin if(data_in=x"5a")then ---******Funciones especiales bandera2<='1'; elsif(data_in=x"06" and rx="10")then aux_e<='1'; ---Corrimiento a la derecha con F1 aux_rs<='0'; elsif(data_in=x"05" and rx="10")then aux_e<='1'; ---Corrimiento a la izquierda con F2 aux_rs<='0'; elsif(data_in=x"66" and rx="10") then aux_e<='1'; ---Borra un espacio Back aux_rs<='0'; elsif (data_in=x"14" and rx="10") then aux_e<='1'; ---Borra todo el LCD Clear display aux_rs<='0'; elsif (rx = "10") then aux_e<='1'; aux_rs<='1'; elsif(rx = "00") then aux_e<='0'; aux_rs<='1'; end if; end process visualiza; count: process(aux2(23)) begin if(rising_edge(aux2(23)))then count_s<=count_s+"0001"; end if; end process count; ------Tabla de conversión de datos Rx a ASCII o función especial with data_in select other_data <=x"41" when x"1c",--a x"42" when x"32",--b x"43" when x"21",--c x"44" when x"23",--d x"45" when x"24",--e x"46" when x"2b",--f x"47" when x"34",--g x"48" when x"33",--h x"49" when x"43",--i x"4a" when x"3b",--j x"4b" when x"42",--k x"4c" when x"4b",--l x"4d" when x"3a",--m x"4e" when x"31",--n x"4f" when x"44",--o x"50" when x"4d",--p x"51" when x"15",--q x"52" when x"2d",--r x"53" when x"1b",--s x"54" when x"2c",--t x"55" when x"3c",--u x"56" when x"2a",--v x"57" when x"1d",--w x"58" when x"22",--x x"59" when x"35",--y x"5a" when x"1a",--z x"31" when x"69",--1 x"32" when x"72",--2 x"33" when x"7a",--3 x"34" when x"6b",--4 x"35" when x"73",--5 x"36" when x"74",--6 x"37" when x"8c",--7 x"38" when x"75",--8 x"39" when x"7d",--9 x"30" when x"70",--0 x"2b" when x"59",--+ x"5e" when x"54",--` x"2a" when x"62",--´ x"ee" when x"4c",--ñ x"2c" when x"41",--, x"2e" when x"49",--. x"2d" when x"4a",--x"20" when x"29",--espace x"01" when x"14",--clear x"10" when x"66",--back x"18" when x"05",--shif left x"1c" when x"06",--shif rigth x"26" when others; end Behavioral; --======================================================================== --########################## TERCER PROGRAMA COUNTER ########################## -TERCER SUBPROGRAMA CONTADOR PARA DIVIDIR LA FRECUENCIA DE RELOJ --======================================================================== library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED. ALL; entity counter is Port ( clock : std_logic; output : out std_logic_vector(25 downto 0)); end counter; architecture Behavioral of counter is signal aux : std_logic_vector(25 downto 0); begin output<=aux; process(clock) begin if(falling_edge(clock))then aux<=aux+"00000000000000000000000001"; end if; end process; end Behavioral; Nombre de archivo: rx_teclado Directorio: C:\Documents and Settings\USUARIO\Mis documentos\Juan manuel\proyecto_vision\Articulos Nuestros\Word Plantilla: C:\Documents and Settings\USUARIO\Reciente\Datos de programa\Microsoft\Plantillas\Normal.dot Título: library IEEE; Asunto: Autor: MS OFFICE Palabras clave: Comentarios: Fecha de creación: 29/01/2004 8:27 Cambio número: 1 Guardado el: 29/01/2004 9:21 Guardado por: MS OFFICE Tiempo de edición: 54 minutos Impreso el: 29/01/2004 9:21 Última impresión completa Número de páginas: 6 Número de palabras: 1.673 (aprox.) Número de caracteres: 9.205 (aprox.)