CAPÍTULO II

Anuncio

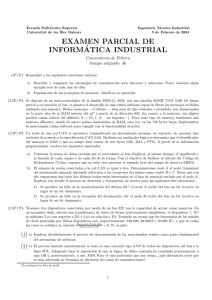

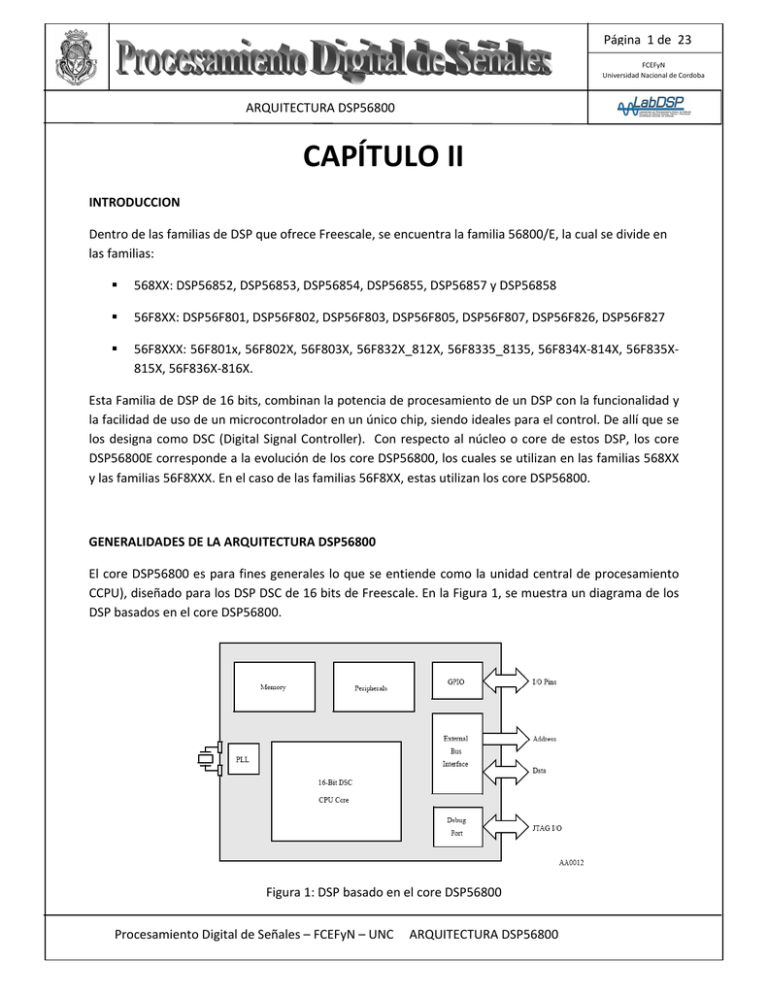

Página 1 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 CAPÍTULO II INTRODUCCION Dentro de las familias de DSP que ofrece Freescale, se encuentra la familia 56800/E, la cual se divide en las familias: 568XX: DSP56852, DSP56853, DSP56854, DSP56855, DSP56857 y DSP56858 56F8XX: DSP56F801, DSP56F802, DSP56F803, DSP56F805, DSP56F807, DSP56F826, DSP56F827 56F8XXX: 56F801x, 56F802X, 56F803X, 56F832X_812X, 56F8335_8135, 56F834X‐814X, 56F835X‐ 815X, 56F836X‐816X. Esta Familia de DSP de 16 bits, combinan la potencia de procesamiento de un DSP con la funcionalidad y la facilidad de uso de un microcontrolador en un único chip, siendo ideales para el control. De allí que se los designa como DSC (Digital Signal Controller). Con respecto al núcleo o core de estos DSP, los core DSP56800E corresponde a la evolución de los core DSP56800, los cuales se utilizan en las familias 568XX y las familias 56F8XXX. En el caso de las familias 56F8XX, estas utilizan los core DSP56800. GENERALIDADES DE LA ARQUITECTURA DSP56800 El core DSP56800 es para fines generales lo que se entiende como la unidad central de procesamiento CCPU), diseñado para los DSP DSC de 16 bits de Freescale. En la Figura 1, se muestra un diagrama de los DSP basados en el core DSP56800. Figura 1: DSP basado en el core DSP56800 Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 2 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 La familia DSP56800 cuenta con una variedad posibilidades de periféricos (ver Figura 1) tales como puertos serie, temporizadores para fines generales, temporizadores en tiempo real y watchdog, distintas configuraciones de memoria (RAM, FLASH, o ambos), puertos entrada – salida para fines generales (GPIO) puertos. Posee On‐Chip Emulation (OnCE™), un sistema que permite a través de un puerto de depuración Joint Test Action Group (JTAG), realizar en tiempo real emulaciones y comprobar el funcionamiento de la programación realizada en el DSP. Otras características del DSP56800 se resumen a continuación: Capacidad de procesamiento de hasta 35 millones de instrucciones por segundo (MIPS) a 70 MHz. Requiere sólo 2.7‐3.6 V de alimentación. Unidad lógica aritmética (ALU) para operaciones de 16 bits. Unidad de generación de direcciones de 16 bits (AGU). Un ciclo de instrucción de 16 bits x 16 bits en paralelo para realizar multiplicación y acumulación. Dos acumuladores de 36 – bits incluidos como extensión de bits. Instrucción simple de 16 bits para realizar “barrel shifter” . Conjunto de Instrucciones en paralelo para un único modo de direccionamiento. Bucles o lazos DO y REP a través de hardware. Dos pines, para la realización o solicitud de interrupciones externas. Tres buses internos de 16 bits de datos. Tres buses internos de de 16 bits de direcciones. Conjunto de instrucciones que soporta tareas de DSP y funciones de control. Eficiente compilador de C y soporte de variables locales. Programación de subrutinas e interrupciones en forma ilimitada. Sistema On‐Chip Emulation. Posibilidad de trabajo en Low‐power y Stop mode. La familia DSP56800 cuenta con un potente conjunto de instrucciones que permiten como por ejemplo realizar diferentes modos de manipulación de bits, operaciones aritméticas con accesos diferentes a Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 3 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 memoria en forma paralela. Otra característica es la posibilidad de manejar diferentes tipos de interrupciones a las cuales se les puede programar el orden de prioridad y el nivel de jerarquía de la misma. El diseño de la arquitectura es en función de tratar de estructurar bloques funcionales independientes que hagan parte del procesamiento de una instrucción, de tal forma que la arquitectura pueda en un ciclo de máquina estar ejecutando en paralelo 5 instrucciones (pipeline). Con esto esta arquitectura puede tener un desempeño de 35MIPS a un reloj de máquina de 75Mhz. Como ejemplo esta arquitectura puede en un ciclo de máquina realizar: Instruction fetch de la siguiente instrucción (Program Controler) Multiplicación de dos argumentos de 16bit 16 x 16 (ALU PDF) Acumulación en registro de 36 bit (ALU) Dos accesos a memoria de datos (AGU, Xab1,Xab2) Actualización de 2 registros de direccionamiento (AGU modo de direccionamiento auto indexado). Actualización de los registros de timer (Program Controler). PERIFERICOS Y ELEMENTOS DEL DSP56800 El DSP56800 está compuesto de unidades funcionales que operan en paralelo para aumentar el rendimiento del DSP. El controlador de programa, AGU, y los datos de cada ALU contienen sus propios registros y lógica de control, por lo que pueden funcionar de manera independiente o en paralelo. Del mismo modo, cada unidad funcional posee interfaces con otras unidades, con la memoria en el core y con la memoria externa a través de los buses de datos y de dirección. La arquitectura del core es segmentada para aprovechar el paralelo de las unidades y reducir significativamente el tiempo de ejecución de cada instrucción. En la Figura 2, se muestra un diagrama en bloques de la arquitectura del core DSP56800. Los principales componentes del núcleo son los siguientes: ALU AGU Control de Programa y unidad de hardware para lazos (HLU) Bus y unida de manipulación de bit (BMU) Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 4 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 OnCE debug port Buses de dirección Buses de Datos Como se nombró anteriormente, alrededor del DSP56800, se cuenta con una serie de periféricos que hacen a las funcionalidades como DSC y que están presenten en las familias de DSP basados en este core. En la Figura 3, se muestra un esquema ejemplo, de los periféricos presentes alrededor del core DSP56800. A continuación se listan los periféricos presentes en los DSP basados en el core DSP56800: Program FLASH and RAM modules Bootstrap FLASH for program RAM parts Data FLASH and RAM modules Phase‐locked loop (PLL) module General purpose Quad Timers Computer operating properly (COP) module Serial Communication Interfaces (SCIs) Synchronous serial interface module (SSI) Serial peripheral interface (SPI) Quadrature Decoders Controller Area Network (CAN) Modules Multiple channels Pulse Width Modulation (PWM) Modules External Memory Interface (EMI) Multiple channels Analog‐to‐Digital Converters (ADC) Programmable general‐purpose I/O (dedicated & shared) JTAG/OnCE port for debugging Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 5 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Figura 2: Diagrama en bloques del core DSP56800. Figura 3: Ejemplo de periféricos alrededor del core DSP56800 de un DSP56F807. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 6 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Tenga en cuenta la Figura 2, la cual ilustra dos métodos para conectar o comunicar los periféricos con el core DSP56800: el primero de ellos es a través del Freescale‐standard IP‐BUSinterfase y el segundo a través del periférico Peripheral Global Data Bus (PGDB). El método de interfaz utilizado para comunicarse con periféricos depende de la especificidad del DSP o dispositivo que se utilice. Los últimos productos DSP han optado por la interfase IP‐BUS. Estas diferencias respecto de los periféricos y de los modos de comunicación con el core DSP56800, pueden consultarse en los manuales de usuarios de cada dispositivo DSP. DATA ARITHMETIC LOGIC UNIT (ALU) La unidad lógica aritmética (ALU) realiza todas las operaciones aritméticas y operaciones lógicas en los datos u operandos en el core. La ALU compone los siguientes elementos: Tres registros de entrada de 16‐bits (x0, y0, y Y1) Dos registros acumuladores de 36‐bits (A y B) o Dos registros de 16‐bits (A0 y B0) o Dos registros de 16‐bits (A1 y B1) o Dos registros de extensión de 4‐bits (A2 y B2) Un acumulador de shifter (AS) Un limitador de datos Un 16‐bit barrel shifter Una unidad en paralelo MAC (en un único ciclo, no segmentado o pipelined). Con la ALU es posible multiplicar, multiplicar y acumular (con signo positivo o negativo de acumulación), sumar, restar, realizar desplazamiento y operaciones lógicas en un ciclo de instrucción. Las operaciones aritméticas se efectúan utilizando aritmética de punto fijo o aritmética entera. Sin embargo es posible también trabajar por medio del compilador, en aritmética sin signo y multi‐precisión. Los operandos de la ALU pueden ser 16, 32, o 36 bits y puede individualmente proceder de los registros de entrada, locaciones de memoria, datos inmediatos o de los acumuladores. Los resultados de la ALU se almacenan en uno de los acumuladores. Por otro lado, algunos instrucciones aritméticas de 16 bits resultan en uno de los tres datos de entrada de los registros de la ALU registros o directamente en la memoria. Las operaciones aritméticas y las operaciones de desplazamiento pueden tener resultados de 16‐bits o de 36 bits. Operaciones lógicas de se realizan en 16 bits, siendo los resultados de 16 bits. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 7 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Los valores de los registros de datos del ALU, se pueden transferir (leer o escribir) a través del “core global data bus” (CGDB) en operandos de 16 bits. El valor del registro X0 también puede ser escrito a través del bus (XDB2) como un operando de 16 bits. A continuación se resume un listado de las operaciones aritméticas que se pueden desarrollar en un ciclo de instrucción: Multiplicación con y sin redondeo. Multiplicación negativa con y sin redondeo Multiplicación y acumulación con y sin redondeo Multiplicación y acumulación con producto negativo con y sin redondeo Adición y substracción Comparaciones Incrementos y decrementos Operaciones Logicas (AND, OR, y EOR) Complemento a uno Complemento a dos (negación) Aritmética y lógica “shifts” Rotaciones Multi‐bit shifts on 16‐bit values Redondeo Valor absolute División iterativa Normalización iterativa Conditional register moves (Tcc) Saturación (limitación) En la Figura 4, se muestra el digrama en bloques correspondiente al ALU de las familias DSP56800. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 8 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Figura 4: Digrama de bloques del ALU de las familias DSP56800 Como se comento anteriormente, los argumentos que maneja la ALU pueden ser de 16, 32 o 36 bit y pueden provenir de sus registros de propósito general, acumuladores, posiciones de memoria, datos inmediatos. De manera reciproca la salida de operaciones aritméticas puede almacenarse típicamente en los acumuladores (32 o 36 bit), pero también resultados en 16 bit pueden almacenarse en sus registros (X0, Y0,Y1) o directo a posiciones de memoria (mediante el bus general de dato del CGDB). Las operaciones de multiplicación y acumulación que realiza la unidad MAC esta diseñada para guardar su resultado en los acumuladores extendidos de 36 bit (A,B), de esta manera mientras se ejecuta esta Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 9 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 operación paralelamente se actualizan los registros fuentes (X0, Y1,Y0) desde los buses internos (CGDB y XDB2). La carga de los registros internos desde y hacia la memoria del sistema se realiza a través del bus de datos interno CGDP (16 bit), pero adicionalmente el registro XO puede recibir información de la interfaz de bus de datos unidireccional XDB2. Esta particularidad de la arquitectura permite que algunas instrucciones en paralelo hagan el acceso a datos a dos posiciones de memoria (load), orientadas a las operaciones de multiplicación y acumulación (instrucción de Assembler mac). La sintaxis de esta operación emblemática de la arquitectura se muestra a continuación: Ejemplo 1: mac X0, Y0, A x(r0) + , X0 x(r3) + , x1 Los pasos en la ejecución de la intrusión de máquina mac involucran: 1. ALU hace la multiplicación de los registros fuente X0,Y0 (16x16). 2. Este valor es sumando al contenido del registro acumulador A (36 bit). 3. La ALU lee el nuevo valor para X0 utilizando la interfaz de datos XDB2. Equivalentemente se actualiza el valor de Y0 utilizando la interfaz de bus de datos CGDB. Para esto la AGU utilizando las direcciones de memoria de los registros ro, r3, y hace la interfaz con el bus de direcciones en el proceso de lectura de memoria. 4. Paralelamente a la funcionalidad de la ALU la AGU pos incrementa los valores de los registros ro y r3 para apuntar a las siguientes posiciones de memoria a accesar, asociada a la siguiente instrucción a ejecutar. Estos pasos ocurren en un ciclo de instrucción. Unidades de la ALU MAC/LU: Corresponde a la unidad central de la ALU. La unidad MAC implementa todas las operaciones aritméticas (sumas, rest6as, multiplicaciones t divisiones), y la unidad LU todas las operaciones lógicas. La Unidad MAC toma argumentos y retorna su resultado en formato de 36 bit estructurado como EXT:MSP:LSP (Extension: Most Significant Product: Least Significant Product). EXT es un registro de 4 bit de extensión, MSP corresponde a los registros A1 o B1 y LSP corresponde a los registros A0 o A1. La operación típica de la unidad MAC toma sus dos registros fuentes argumentos de 16 bit los multiplica utilizando codificación entera o fraccional y suma dicho resultado en 32 bit al contenido de un acumulador (A, B) de 36 bit, de esta manera los 4 bit adicionales permiten mayor precisión (EXT). Las operaciones lógicas de la porción LU manipulan datos de 16 bit, que en el caso de los acumuladores afectan la porción MSP. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 10 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Accumulator Shifter: Toma el acumulador de 36 bit, modifica su contenido, y lo envía como entrada a la unidad MAC que lo opera como entrada. Las operaciones de esta unidad incluyen: shift hacia los bits más o menos significativos. Data Limiter and MAC Output Limiter Units: La unidad Data Limiter convierte de manera consistente los valores en 36 bits provenientes en los acumuladores, a 16 bit (instrucciones tipo move acumulador, registro de 16bit/ posición de memoria) y maneja los overflow producto de resultados fuera del rango de representatividad. La unidad MAC Output Limiter, maneja todo los datos a la salida de la unidad MAC. La estrategia empleada por estas unidades para tratar los overflow aritméticos, básicamente es aproximar el número más grande en magnitud que puede ser representado con el mismo signo (clamp, clip). En esto consiste la Saturación, la cual es empleada tanto con aritmética entera como fraccional. Sin esta técnica se pierde la representación de la información tal como se ilustra en el ejemplo de la Figura 5. Figura 5: Ejemplo de la operación Data Limiter (Saturación positiva) en la transferencia a posiciones de memoria de 16 bit (DSP56800 Family Manual. 3‐26). Continúa. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 11 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Figura 5: Ejemplo de la operación Data Limiter (Saturación positiva)en la transferencia a posiciones de memoria de 16 bit (DSP56800 Family Manual. 3‐26). Continuación. El SA bit (bit 4, de saturación) en el DSP´s Operation Mode Register (OMR) habilita la unidad MAC Output Limiter. Si el bit es habilitado, satura la salida de la MAC a 32 bit. En la Figura 6, se muestra un ejemplo en donde se habilita este modo. Figura 6: Ejemplo de la operación del MAC Output Limiter en la generación de resultados en codificación de 32 bit. ._ Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 12 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 ADDRESS GENERATION UNIT (AGU) La dirección unidad de generación (AGU) es una unidad independiente que realiza todos los cálculos y modos de direccionamiento que soporta la familia DSP56800. La AGU opera en paralelo con otros recursos para chip de manera de minimizar el tiempo de operación de esta familia de DSP. La AGU cuenta con dos módulos ALU, un modulo destinado al calculo aritmético de direcciones complejas y otro de direccionamiento simple por medio del incremento o decremento de direcciones. De esta manera la AGU permite el direccionamiento de dos direcciones de 16 bits en cada ciclo de instrucción: uno para cualquier dirección de memoria a través del bus (XAB1) o del bus (PAB) y otro para cualquier dirección de memoria a través del bus (XAB2). Se puede acceder a 65536 lugares por medio de los buses XAB1 o XAB2 y 65536 lugares por medio del bus PAB, con un total de 131072 direcciones de 16 bits de ancho de palabra. Esto es posible ya que la AGU esta conectada físicamente a todos los buses de dirección del sistema (XAB1, XAB2, PAB) (ver Figura 7). Figura 7: Esquema simplificado de comunicación entre las unidades mediante los buses internos de la familia DSP56800, lo que permite el acceso independiente a direcciones de dato y programa. Dado que esta unidad es independiente a la MAC/LU, esta paralelamente puede ser accesos y actualización de sus registros de direcciones (índice o base). Ejemplo 1. Los registros que maneja la AGU son: Registros de direcciones R0, R1, R2, R3. Actúan como punteros a posiciones de memoria (modo de direccionamiento indirecto por registro). Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 13 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Registro índice N. Este registro actúa como registro índice a un espacio de memoria contigua apuntado por uno de los registros de direcciones (modo de direccionamiento indexado). Registros de configuración de la AGU, M01. Este determina si se utiliza aritmética lineal o modular con modulo n (permite el acceso a arreglos circulares), para la aritmética de direcciones. El SP, apunta al espacio de direcciones asignado para el manejo del stack. Dos ALU hay presentes en la AGU para la aritmética de direcciones, la unidad aritmética (Modulo Aritmetic Unit) y la unidad de incremento‐decremento (ver Figura 8). Esta unidad puede hacer acceso simultáneo a dos posiciones de memoria de datos y proveer estos a la unidad MAC/LU en un ciclo de instrucción. El primer operando se direcciona por el bus XAB1 y llega por el bus de datos CGDB y el segundo se direcciona por el bus XAB2 y llega por la interfaz de datos XDB2. (ver Figura 8 ). La limitación es que la dirección que va al bus XAB2 tiene que pertenecer al espacio de memoria de dato interno (on‐chip) del core. Alternativamente esta unidad puede direccionar memoria de programa a través del bus PAB y memoria de datos a través del bus XAB1. En general esta unidad en un ciclo de instrucción puede generar 2 direcciones de 16 bit y dos actualizaciones de sus registros internos para el siguiente acceso. En general la interfaz de bus de datos CGDB permite leer y escribir todos los registros internos de la AGU. Figura 8: Estructura de las unidades constituyentes de la AGU y sus interfaces con los buses internos del core de la familia DSP56800. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 14 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 El registro M01 determina el tipo de aritmética de direccionamiento que da como salida el Modulo Aritmetic Unit de esta manera esta puede hacer aritmética lineal o modulo n (n<16), el tamaño de n también se determina en los bit que caracterizan el registro M01. La aritmética de modulo n, se implementa para el acceso a buffer circulares, que puede ser útil en el manejo de ciertas estructuras de datos y algoritmos de acceso. Como por ejemplo la implementación de buffer donde llegan señales a tasa constante para ser procesadas. En la Figura 9 se ilustra el concepto de buffer circular. Figura9: Buffer Circular para 5 locaciones. La Unidad de incremento decremento solo actúa sobre el registro R3 y con aritmética lineal de direccionamiento. Todas estas características de la ALU permiten implementar hasta 14 modos de direccionamiento, dentro de los cuales se encuentra: Direccionamiento indirecto, sin actualización Direccionamiento indirecto con post‐incremento Direccionamiento indirecto con post‐decremento Direccionamiento indirecto con post‐actualización de un registro. Direccionamiento indirecto con un índice de 16‐bit de offset. Direccionamiento indirecto con un índice de 6‐bit de offset. Direccionamiento indirecto con índice de un registro Direccionamiento de datos inmediatos Direccionamiento de datos cortos inmediatos Direccionamiento absoluto Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 15 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Direccionamiento absoluto de dirección corta Direccionamiento periférico de dirección corta Direccionamiento por registro directo Direccionamiento implícito El conjunto de instrucciones del DSP568010, contienen las instrucciones que permiten abordar todos los modos de direccionamiento antes mencionados. La manera de cómo especifica los operandos en estas instrucciones depende, como es de esperar, de los tipos direccionamiento a realizar (ej: un valor inmediato, que se encuentra en un registro o en la memoria). Los modos de abordar los direccionamientos se agrupan en cuatro categorías: Registro directo ‐ operaciones directa de direccionamiento entre los registros del core. Dirección indirecta de registro ‐ utiliza una dirección de registro la cual se accede a través de un puntero al lugar de referencia en la memoria. Inmediato ‐ El operando es el que figura como un valor en sí mismo de la instrucción (un número). Absoluta ‐ Utiliza una dirección que figura en la instrucción de un lugar de referencia en la memoria, como un operando. A través del lenguaje ensamblador es posible forzar los operandos en las instrucciones para lograr un modo de direccionamiento específico, tal como se muestra en la Tabla 1. Tabla 1: Forzado de operandos en los modos de direccionamiento Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 16 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Otras posibilidades del forzado de operadores se dan para las instrucciones de “jump” o “branch” y cuya nomenclatura se muestran en la Tabla 2. Tabla 2: Forzado de operadores para instrucciones Jump y Branch. CONTROLADOR DE PROGRAMA Y UNIDAD DE LAZOS POR HARDWARE El controlador de programa realiza básicamente las siguientes tareas: Instrucción prefetch Instrucción de descodificación Control de bucle por Hardware Proceso de Interrupción (excepciones) La ejecución de Instrucción se lleva a cabo en otras unidades básicas, tales como el ALU, AGU, o la unidad de manipulación de bits. El controlador de programa consiste en lo siguiente: “ A program counter unit” “Instruction latch and decoder” “Hardware looping control logic” “Interrupt control logic” “Status and control registers” Su característica distintiva de otras arquitecturas es que esta unidad provee soporte a nivel de hardware (Hardware Looping Control Logic) para los procesos de tipo recursivos de alto nivel (propios de los algoritmos de procesamiento digital de señales), manifestándose a nivel de hardware en la existencia de unidades espéciales y registros como LC (loop count register), LA (loop addres register), SR (Status Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 17 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 register, el cual almacena el estado del proceso utilizado en las instrucciones de salto condicional), y a nivel de lenguaje de máquina en instrucciones especiales DO y REP, que permiten compilar y ejecutar de manera más eficientes este tipo de procesos recursivos. Esta unidad provee el soporte para el manejo de interrupciones a través de la sistema provista en el core (Interrupt Control Logic). Específicamente se tiene la posibilidad de realizar 2 interrupciones externas (special‐purpose external interrupts) y siete canales de interrupción. Es posible además, definir las prioridades de las diferentes fuentes de interrupción (enmascarables) según estos canales. La configuración de las interrupciones enmascarables, se realizan a través de los registros de configuración SR (bit I0, I1) y IPR. En la Figura 10, se muestra el diagrama en bloques de los elementos que conforman el Controlador de Programa de la familia DSP56800. Figura 10: Elementos y unidades de la Unidad de Control de Progama de la familia DSP56800 Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 18 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Como puede observarse en la Figura 10, esta unidad posee en general 4 registros: LC (loop count register), LA (loop addres register), SR (Status register) OMR (Opereting mode register): este registro determina el modo de operación de la arquitectura y el mapa de memoria de su espacio de direccionamiento de 128Kx 16 palabras (instrucciones y datos), al igual que parte del estado de ejecución de proceso (bit NL). PC ( Program Counter) HWS (Hardware Stack): este es un buffer de dos palabras de 16 bit que implementa un stack por hardware de profundidad dos, que almacena la dirección de la primera dirección de programa asociada a la primera instrucción de un ciclo recursivo, caracterizado a nivel de asemmbler por la instrucción DO. BUSES Y UNIDAD DE MANIPULACION DE BIT La arquitectura interna del core de la familia DSP56800, esta constituido por barios buses independientes que facilitan la transferencia paralela e independiente entre la memoria de datos y la memoria de programa. Buses de Direcciones Se tiene dos buses unidireccionales independientes de direcciones para datos (XAB1 y XAB2), los cuales permiten accesar en un ciclo de máquina dos argumentos desde memoria de datos. La restricción es que el bus XAB2 sólo puede accesar a la memoria interna de datos. También se tiene un bus de direcciones unidireccionales de programa PAB. Buses de Datos Los buses son básicamente: CGDB (Core Global Data Bus): Este bus es el bus principal que permite la transferencia entre la ALU y la memoria de datos (información direccionada por XAB1). PDB (Program Data Bus): Transferencia de memoria de memoria de programa (Instruction Fetch). Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 19 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 XDB2 (External Data Bus 2): Es utilizado cuando existen transferencia simultánea de dos posiciones de memoria de datos. PGDB (Peripheral Data BUS): Transferencia de información desde o hacia los dispositivos periféricos. La unida de Bus es una unidad de conmutación que permite la conexión física entre los buses, lo que permite transferencias entre posiciones de memoria de datos (CGDB) y dispositivos de I/O (PGDB), o entre posiciones de memoria de programa y datos. En la Figura 11 se muestra el diagrama en bloques de la arquitectura de la familia DSP56800, en donde se resalta los buses y la interconexión de los diferentes sistemas del core. FIGURA 11: Ejemplo de una diagrama en bloques de un DSP basado en el core DSP56800 y sus correspondientes buses. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 20 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 ON‐CHIP EMULATION (ONCE) El On‐Chip Emulation (ONCE) permite al usuario interactuar en un entorno de depuración con el DSP56800 y sus periféricos. Sus capacidades incluyen el examen de los registros, registros de memoria, la fijación de interrupciones en el programa o memoria de datos, la realización de saltos de instrucción, etc. A través de los pines del puerto JTAG permiten al usuario el acceso al DSP o DSC, haciendo el mantenimiento de depuración sin sacrificar el control o recursos a la hora de realizar una tarea por parte del DSP o DSC. ARQUITECTURA DE MEMORIA La particularidad de ser esta una arquitectura Hardvare implica que esta tiene dos espacios de direcciones diferentes, de datos (direccionado por los buses XAB1, XAB2) y de programa (direccionado por el bus PAB) ambos de 64K direcciones (216). En el espacio de memoria de programa las primeras 128 posiciones están reservadas para la tabla de interrupciones, y existe una posición definida para cada rutina de interrupción de los dispositivos de I/O. En el caso de la memoria de datos, en ella se encuentran el “Memory Mapped” de los registros de transferencia de los I/O, los cuales típicamente utilizan el rango de direcciones entre la $FFC0‐$FFFF. En la Figura 12 se muestra el mapa de memoria correspondiente a la familia DSP56800. Figura 12: Mapa de memoria de la arquitectura de la familia DSP56800 BLOQUES EXTERNOS AL DSP56800 Tal como se enunció anteriormente y se mostró en la Figuras 1,2,3 y 11, la familia DSP56800 cuenta con una serie de bloques externos al núcleo o core, los cuales consisten en periféricos y bloques de memoria. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 21 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Estos y otros bloques se describen con más detalle en los manuales de usuario del DSP o DSC, basados en esta familia. A continuación se realiza una pequeña descripción de los elementos externos relevantes al núcleo o core. Memoria de datos: La memoria de datos (RAM, FLASH, o ambas cosas) se pueden añadir en torno a un núcleo en un chip. El direccionamiento se realiza a través de los buses XAB1 y XAB2, mientras que la transferencia de datos se produce a través de los buses en la CGDB y XDB2. De esta manera es posible realizar una lectura o escritura de datos, o dos lecturas de datos durante un ciclo de instrucción. Cabe aclarar que la porción de memoria de datos destinada a los registros de los periféricos, no puede ser utilizada, como memoria de datos. En ese caso la memoria de datos puede ampliarse fuera del DSP o DSC hasta 65.536 lugares. Memoria de programa: La memoria de programa (RAM, ROM, o ambas cosas) se pueden añadir en torno a un núcleo en un chip. Le direccionamiento se realiza a través del bus PAB y las transferencias de datos se produce a través del bus PDB. Como se explico en el mapa de memoria de la familia DSP 56800, los primeros 128 lugares de la la memoria del programa están disponibles para vectores de interrupción, aunque no es necesario utilizar todos los recursos correspondiente a esos 128 lugares. A diferencia de lo que sucede con la memoria de datos, algunos de estos lugares es posible ser utilizados por el programa del usuario si el mismo tiene la prudencia y el conocimiento correspondiente del mapa de memoria. La memoria de programa también puede ampliarse fuera del DSP o DSC hasta 65.536 lugares. IP‐BUS Bridge: Los dispositivos periféricos de los DSP o DSC basados en el núcleo DSP56800 utilizan el Freescale estándar IP‐BUS interfaz. Estos dispositivos contienen un puente IP‐BUS, permitiendo a los periféricos acceder al core o núcleo a través del bus de datos CGDB y el bus de direcciones XAB1 bus de direcciones. Phase Lock Loop (PLL): El PLL permite al DSP o DSC chip sincronizar, el uso de un reloj externo diferente con el régimen de reloj interno del core. Este PLL permite el pleno funcionamiento de velocidad del DSP o DSC, usando un reloj externo que presente una velocidad diferente. El PLL permite la multiplicación de frecuencias y reduce la potencia global del sistema mediante la reducción de la frecuencia en la entrada del reloj de referencia. MODELO DE PROGRAMACIÓN DEL DSP56800 A la hora de realizar la programación de un DSP o DSC basado en familia DSP56800, es útil recordar los registros del núcleo y su correspondiente modelo de programación los cuales se muestra en la Figura 13. Hay que tener en cuenta que estos no son la totalidad de registros a tener en cuenta a la hora de realizar la programación. El resto de los registros corresponden a los registros de los dispositivos periféricos y otras funciones que no están vinculados en el núcleo. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 22 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Figura 13: Registros utilizados en el modelo de programación del DSP56800 BIBIOGRAFIA DSP56800 Family Manual. 16‐Bit Digital Signal Controllers. DSP56800FM Rev. 3.1 11/2005. Freescale. INFORMACION ADICIONAL Información adicional del DSP56800 se encuentra en la referencia BIBLIGRAFIA mencionada cuyos tópicos principales son: Capitulo 6 (Instruction Set): Información de los tipos de instrucciones, formatos, sintaxis, argumentos, tiempos de ejecución (Instruction Pipeline), etc. Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800 Página 23 de 23 FCEFyN Universidad Nacional de Cordoba ARQUITECTURA DSP56800 Capitulo 7 (Interrupts and the Processing States): Estados de operación del DSP o DSC, procesamiento interno de eventos externos interrupciones, descripción de las etapas en dicho proceso, modificaciones en el flujo del proceso (PC), almacenamiento del estado del proceso. Tipos de interrupciones externas(IRQ) – internas (Timers). Procesamiento Digital de Señales – FCEFyN – UNC ARQUITECTURA DSP56800