CAPITULO VII TECNICAS DE CONTROL DE ERROR

Anuncio

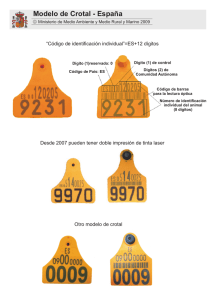

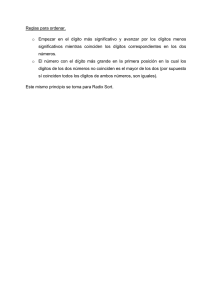

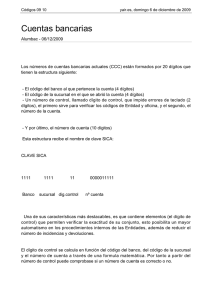

CAPITULO VII TECNICAS DE CONTROL DE ERROR 7.1. INTRODUCCION Durante la transmisión de información digital a través de un sistema o canal se producen errores prácticamente inevitables debido a la presencia de ruido y a otros factores tales como la interferencia intersímbolo, la intermodulación y los ecos. Es por ello necesario establecer maneras, si nó para evitar los errores, por lo menos para poder reconocer su presencia y si es posible corregirlos. El proceso de control de error es de gran importancia pues debido a la baja redundancia de los datos digitales, un grupo de números o símbolos alfanuméricos erróneo puede parecerse a otro significando algo muy diferente. El concepto de redundancia lo podemos entender mejor mediante un sencillo ejemplo: el conjunto [00, 01, 10, 11] de palabras o mensajes binarios no es redundante porque todas las palabras posibles de dos dígitos binarios están contenidas en el conjunto; un error de transmisión en cualquiera de las palabras la convierte en otra palabra válida del conjunto y no habría manera de detectar el error. La redundancia es de capital importancia en el control de error pues, como lo estableció Shannon, no es posible transmitir sin error si los códigos utilizados tienen cero redundancia. El primer método de control de error que se utilizó fue el denominado “ecoplex”. En este método el transmisor envía un carácter, el cual es recibido en el receptor y retransmitido como un eco hacia el transmisor, de aquí el nombre de ecoplex. En el transmisor se examina el carácter eco recibido para ver si difiere del carácter original; si es diferente simplemente se corrige el error y se transmite de nuevo. Como un error de transmisión puede ocurrir en cualquiera dirección, es posible que un carácter erróneo en una dirección se convierta en el carácter correcto al regresar como eco y viceversa. Este método fue muy popular en los sistemas de teletipo, aunque todavía se utiliza en algunos sistemas de transmisión asincrónica. En los sistemas de comunicación actuales el control de error se efectúa mediante la aplicación de códigos especiales que agregan redundancia; estos códigos son de la clase de “códigos de canal” para diferenciarlos de los códigos de línea, vistos en el Capítulo . Esta redundancia agregada permite detectar y/o corregir los errores ocurridos durante la transmisión de los bloques de datos. En este capítulo vamos a describir en forma algorítmica algunos de los códigos más utilizados para la detección y/o corrección de errores. La teoría de los códigos es una materia muy compleja y altamente matemática y un estudio más detallado de estos códigos está fuera de los alcances de este libro. 7.2. DETECCION Y CORRECCION DE ERROR Cuando se recibe un bloque de dígitos binarios es necesario asegurarse de que no contiene errores de transmisión. Si se detecta que el bloque está en error, se tiene dos opciones: una es corregir el error en el sitio y la otra solicitar la retransmisión del bloque. Esta situación ha producido las dos técnicas de control de error comúnmente utilizadas: la 422 VII. TECNICAS DE CONTROL DE ERROR “Corrección Directa de Error (Forward Error Correction, FEC)” y la “Solicitud de Repetición Automática (Automatic Repeat Request, ARQ)”. En la técnica FEC se utilizan códigos para detectar y corregir los errores en el receptor; mientras que en la técnica ARQ los códigos solamente detectan la presencia de errores en los datos recibidos y se solicita en alguna forma la repetición de los bloques que vienen en error. La técnica ARQ es la que se utiliza comúnmente en los protocolos de comunicación, vistos en los Capítulos IV y V. Cualquiera que sea la estrategia de control de error, FEC o ARQ, la secuencia transmitida debe ser codificada, es decir, se le debe agregar una cierta redundancia. Esta codificación se efectúa en los CODEC y se localiza en la forma mostrada en la Fig. 7.1. FUENTE CODEC Tx/Rx CANAL Tx/Rx CODEC DESTINO Fig. 7.1. Control de Error (FEC o ARQ). El diseñador de sistemas de control de error se enfrenta entonces a dos problemas fundamentales: (a) Cómo sintetizar un código con la redundancia deseada o las características FEC o ARQ requeridas y, por supuesto, cómo diseñar e instrumentar el codificador y el descodificador (el CODEC) en una forma eficiente y sencilla. (b) Cómo hacer que el código total (incluidos los dígitos redundantes) sea lo más eficiente posible, es decir, que la redundancia agregada sea mínima y máximo el rendimiento. 7.2.1. Rendimiento y Redundancia de un Código La inclusión de redundancia en la transmisión de datos tiene como consecuencia un aumento en la velocidad de modulación de las secuencias transmitidas, lo cual se traduce en un aumento del ancho de banda requerido. Se puede definir entonces dos parámetros de gran interés en la codificación: el rendimiento E del código, y la redundancia R. En efecto: Rendimiento del Código = E% = y la Redundancia, Información realmente transmitida 100 (7.1) Máxima información posible de transmitir R% = [1- E]100 (7.2) Por ejemplo, para el código [00, 01, 10, 11] se tiene: E% = 2 bits 100 = 100% 2 bits y R% = 1 – 1 = 0% En este código es fácil observar que el conjunto de mensajes o palabras no tiene redundancia; esto quiere decir que cualquier error en un dígito convierte la palabra en otra palabra válida pero diferente. En este caso no hay manera de detectar, y mucho menos corregir, cualquier error ocurrido en la transmisión. Comparemos esta situación con la transmisión del idioma español que es altamente redundante; es evidente que al recibirse, por ejemplo, la palabra “veloicdad”, se puede detectar que hubo una permutación entre la 423 VII. TECNICAS DE CONTROL DE ERROR “i” y la “c”, pues la palabra tal como está escrita no existe en español. Por otro lado, un conjunto de mensajes puede ser parcialmente redundante, pero con una estructura que lo hace ineficiente en cuanto a la protección contra errores. Por ejemplo, en el caso de los números telefónicos se puede decir que son parcialmente redundantes, pues no todas las combinaciones de números son utilizadas o que en algunos casos el orden de los dígitos pudiera tener algún significado. Este tipo de secuencias no es apropiado para ser protegido eficientemente contra errores de transmisión. Si mediante alguna forma controlada se le agrega dígitos de redundancia a una secuencia que necesita protección, la información adicional proporcionada por esos dígitos se puede utilizar para detectar y/o para corregir errores. Por ejemplo, en el código [00, 01, 10, 11] se le agrega a cada palabra un dígito extra de acuerdo con las siguientes condiciones: un CERO si el número de UNOS en la palabra original es par o ausencia de UNOS, o un UNO si el número de UNOS en la palabra original es impar. Esta es la denominada “paridad par”. El dígito extra se denomina “dígito de paridad” y el número de UNOS de la palabra resultante es el “peso” o “ponderación” del código. En la Fig. 7.2 se muestra este proceso. 0 0 1 1 0 1 0 1 0 1 1 0 Código Resultante [000, 011, 101, 110] Cuatro palabras codificadas con paridad par Dígitos Redundantes o de Verificación Dígitos de Información Fig. 7.2. Mecanismo de Codificación con Paridad Par En general, se dice que hay “paridad par” cuando la ponderación (número de UNOS) de la palabra codificada es cero o par. Si la ponderación es impar, se tiene la “paridad impar”. El código tiene ahora la forma [000, 011, 101, 110] y se puede detectar un simple error en cualquiera de las cuatro palabras del código. En efecto, supóngase que se transmitió la palabra 101 y que debido a las condiciones de transmisión se recibió la palabra 111. En el receptor se recalcula el dígito redundante con base en los dos primeros obteniéndose un CERO, pero esto está en conflicto con el dígito redundante recibido que es un UNO, de modo que el receptor deduce que hay un error presente, aunque no sabe si lo que se transmitió fue 101 ó 011. De todas maneras, se ha detectado la presencia de un error que se puede corregir solicitando la repetición o tomando alguna acción predeterminada. ♣ Ejemplo 7.1 En las siguientes secuencias codificadas el dígito de paridad está en negrita. Diga qué tipo de paridad (Par o Impar) es: 100101101, 010111001010, 101001110111001001101, 0111100101000110100101000 424 VII. TECNICAS DE CONTROL DE ERROR Solución: Recordemos la Regla de Paridad: “Si la Ponderación (número de UNOS en la palabra codificada) es cero o par, se tiene la Paridad Par. Si la ponderación es impar, se tiene la Paridad Impar”. Primera secuencia Î 5 UNOS Î paridad impar Segunda secuencia Î 6 UNOS Î paridad par Tercera secuencia Î 12 UNOS Î paridad par Cuarta secuencia Î 11 UNOS Î paridad impar ♣ La verificación efectuada por el receptor en el código de la Fig. 7.2 se denomina “prueba de paridad (parity check)” y ella permite detectar errores sencillos o triples (error también en el dígito redundante), pero no errores dobles (por ejemplo, enviado 101, recibido 011). Nótese que esta prueba de paridad no permite la corrección ni de un simple error, pues no hay información suficiente en la redundancia agregada que permita hacerlo. El precio que se paga al agregar redundancia es una disminución del rendimiento de transmisión y una exigencia mayor sobre el ancho de banda del sistema, pues si la velocidad de información se mantiene constante, hay que aumentar la velocidad de modulación. Para el caso de la Fig. 7.2, se puede ver que el rendimiento y la redundancia son E% = (2/3)100 = 66,6% y R% = 33,3%; sin embargo, el ancho de banda requerido es 1,5 veces el ancho de banda original. El proceso de agregar redundancia se denomina “codificación” y el de deducir la presencia o ausencia de errores, “descodificación”. Hemos utilizado estos términos pues son la traducción literal de las correspondientes inglesas (“encoding” y “decoding”), pero debe tenerse en cuenta que la palabra binaria ella misma es producida por otro proceso de codificación previo. Los códigos de detección solamente (ARQ) o de detección y corrección de error (FEC) se denominan, en general, “Códigos de Bloque”. La redundancia se agrega a cada “palabra de datos” (o “palabra mensaje”) y la expresión total [datos + redundancia] se denomina “palabra código” o “palabra codificada”. El número de dígitos en cada palabra código es la “longitud de bloque”, y habrá tantas palabras código como palabras mensaje o palabras de datos. Si la palabra mensaje tiene m dígitos y la redundancia agregada es de k dígitos, la longitud de bloque de la palabra código será de n = (m + k ) dígitos. Sería muy interesante poder calcular la probabilidad de error en un bloque de datos en un enlace dado, pero desafortunadamente esto es muy difícil. En primer lugar, porque los errores en los enlaces tienden a ser dependientes y ocurren en ráfagas; no hay modelos matemáticos apropiados para determinar la longitud o la intensidad de estas ráfagas, las cuales varían ampliamente dentro de un mismo enlace. En segundo lugar, porque para cualquier código razonable la frecuencia de errores es muy pequeña y muy difícil de medir experimentalmente debido a sus características aleatorias. Como resultado de estas dificultades, la efectividad de un código FEC o ARQ se caracteriza mediante tres parámetros: (1) la distancia mínima del código, (2) la capacidad de detección de ráfagas, y 425 VII. TECNICAS DE CONTROL DE ERROR (3) la probabilidad de que una secuencia aleatoria de datos sea aceptada como libre de errores. La distancia mínima de un código se define como el mínimo número de errores necesarios para convertir una palabra código en otra. La longitud de una ráfaga de errores en un bloque es el número de dígitos desde el primer dígito en error hasta el último, ambos inclusive. La capacidad de detección de ráfagas de un código se define como el entero B más grande tal que el código pueda detectar todas las ráfagas de longitud ≤ B. Todos estos parámetros se pueden calcular, pero eso está fuera de los propósitos de este libro. 7.3. ESQUEMAS DE DETECCION Y/O CORRECCION DE ERROR La necesidad de saber si los datos recibidos están o nó correctos impulsó el diseño de numerosos esquemas o códigos para la detección y/o corrección de errores. A continuación vamos a describir algunos de los esquemas más conocidos utilizados en las telecomunicaciones. 7.3.1. Repetición La repetición es la forma más simple de detección de error. La redundancia consiste en transmitir cada dígito de información dos veces y las dos versiones se comparan en el receptor. En esta forma se puede detectar errores en alguno de los dígitos. Los dígitos de información se pueden repetir también dos o más veces, y en el receptor se hace una prueba de mayoría (O-exclusivo o módulo 2) para establecer el valor correcto del dígito de información si por lo menos uno de los ellos llegó en error. En general, m transmisiones del m − 1 mismo dígito permite detectar (m – 1) errores y corregir ent errores. Sin embargo, 2 el precio a pagar en términos del rendimiento es alto. En efecto, para m = 2 → E = 1/2 para m = 3 → E = 1/3 para m transmisiones → E = 1/m pero la técnica de detección y corrección es sumamente sencilla aunque lenta. 7.3.2. Códigos de Ponderación Constante Los códigos de ponderación constante son códigos de bloque con N palabras código que consisten en todas las secuencias binarias posibles de longitud n que contienen m UNOS. Por ejemplo, sea el código siguiente donde: n=4; m=2 ; N = 6 Secuencias posibles: 1100 1010 1001 0101 0011 0110 N es el número de palabras código y viene dado por 426 VII. TECNICAS DE CONTROL DE ERROR N= n! m! (n − m)! (7.3) Las N secuencias particulares se obtienen desarrollando las 2n secuencias binarias tomándose aquellas que contienen m UNOS. Con este tipo de código se puede detectar errores simples, y errores dobles si los errores son ambos en los UNOS o ambos en los CEROS. Un esquema frecuentemente utilizado es aquel para el cual m = 3, n = 7 y N = 32, aplicado en la telegrafía. Estos códigos se conocen también con las denominaciones “código m-de-n” y “código de relación fija o constante”. Son de fácil instrumentación, pero su rendimiento es relativamente bajo. ♣ Ejemplo 7.2 En el Código de Ponderación Constante, escriba todas las secuencias de longitud 5 que contienen tres UNOS. Solución: n = 5; m = 3. Se desarrollan todas las 2n secuencias y de allí se extraen aquellas que contienen tres UNOS; son 25 = 32 secuencias: 00000 01000 10000 11000 00001 01001 10001 11001 00010 01010 10010 11010 00011 01011 10011 11011 00100 01100 10100 11100 00101 01101 10101 11101 00110 01110 10110 11110 00111 01111 10111 11111 Las secuencias que contienen tres UNOS están remarcadas en negrita; son 10. Por lo tanto, Número de palabras codificadas N = 10. Verificación, expresión (7.3): N= 1⋅ 2 ⋅ 3 ⋅ 4 ⋅ 5 = 10 1 ⋅ 2 ⋅ 3 ⋅1 ⋅ 2 ♣ 7.3.3. Suma de Verificación (Checksum) En este método la palabra mensaje forma un bloque sobre el cual se efectúa una cierta operación. El resultado de esta operación se agrega como redundancia formando la palabra código la cual se transmite. En el destino se repite la misma operación sobre la palabra mensaje y el resultado de esa operación se compara con la redundancia transmitida. Si los dos resultados son iguales, se estima que el bloque de datos fue recibido correctamente, y se reconoce la recepción correcta del mensaje; pero si los resultados no son iguales se considera que el mensaje está en error y se pide la retransmisión del mismo. Este es el procedimiento más utilizado en los protocolos de comunicación vistos. Uno de los esquemas más conocido es la "suma de verificación (checksum)" que se utiliza en el protocolo XMODEM. La operación consiste en sumar los valores de los caracteres contenidos en el campo Información y dividir la suma por 255. El cociente se 427 VII. TECNICAS DE CONTROL DE ERROR descarta y lo que se transmite como BCC es el resto de la división. Matemáticamente, el BCC se puede generalizar mediante la expresión N BCC = Re sto ∑ Valor de los caracteres ASCII 1 2N - 1 (7.4) donde N es el número de caracteres de la palabra mensaje; el número n de dígitos del BCC es igual a n = log 2 ( N) + 1 . En el caso del protocolo XMODEM, N = 128 y n = 8 dígitos; el BCC irá en un octeto. ♣ Ejemplo 7.3 Durante un intercambio de información en XMODEM la suma de los valores de los 128 caracteres contenidos en el campo Información es igual a 10850. Determine el BCC correspondiente. Solución: En el CODEC se efectúa la siguiente operación (que para más claridad la efectuamos en decimal, aunque en la práctica las operaciones son binarias o hexadecimales): 10850 255 0650 42 El cociente no se utiliza 140 => Resto => BCC = 10001100 MSB LSB El BCC que se le agrega a la trama es entonces 00110001. Nótese que el LSB se envía de primero. ♣ 7.3.4. Código de Prueba de Paridad Sencilla Este es el tipo de código detector de error que introducimos someramente en la Sección 7.1. Un código de prueba de paridad sencilla (“simple redundancy check, SRC”) de longitud de bloque n se puede establecer efectuando una prueba de paridad sobre los m dígitos de información de la palabra de datos o palabra mensaje. El dígito de paridad es la suma módulo 2 de los valores de los m dígitos de la palabra mensaje, es decir, sea c el dígito de paridad, entonces, m c = d1 ⊕ d 2 ⊕ d 3 ⊕ .... ⊕ d m = ∑ d j módulo 2 ; n = m + 1 (7.5) j=1 donde ⊕ ≡ suma módulo 2 [recuérdese que A ⊕ B = AB + AB ]; d1 es el dígito de menor peso (LSB) y m el número de dígitos de información. El dígito de paridad c se agrega a la 428 VII. TECNICAS DE CONTROL DE ERROR palabra mensaje y se transmite de último, siendo n = m + 1 la longitud de la palabra código; la paridad es par. La palabra transmitida tiene entonces la forma [ d1d 2 d 3 ⋅ ⋅ ⋅ d m c ]. Con este código se puede detectar errores sencillos, triples, en general, un número impar de errores en una palabra código; sin embargo, si el número de errores es par, los errores no pueden ser detectados. En consecuencia, se puede decir que este código detectará solamente el 50% de los errores de transmisión. El rendimiento es bueno: E = m/n y R = 1 / n ; si m >> 1, el aumento en el ancho de banda es despreciable y el rendimiento es casi del 100%. 7.3.5. Código de Prueba de Paridad Vertical y Horizontal La prueba de paridad vertical (VRC) es un esquema de detección de error similar a la prueba de paridad sencilla aplicada a cada uno de los caracteres de un bloque de datos. Por su parte, la prueba de paridad horizontal o longitudinal (HRC o LRC) se utiliza para determinar si un error de transmisión ha ocurrido en un mensaje compuesto por caracteres. La secuencia de dígitos en el LRC se calcula en el transmisor y se transmite como el último carácter del mensaje; es el carácter BCC visto en el Capítulo III . En el receptor el BCC se recalcula y el BCC recalculado se compara con el BCC transmitido. Si son iguales, se supone que no hubo errores en la transmisión; si son diferentes, hubo error en la transmisión y se puede solicitar la retransmisión del bloque completo. En la Fig. 7.3 se muestra el mecanismo de generación de las paridades VRC y LRC, en ASCII. El BCC contiene 8 dígitos. Sentido de Transmisión Caracteres …… E LRC (par)→ L [] B I T …… BCC b0 1 0 0 0 1 0 → 0 b1 0 0 0 1 0 0 → 1 b2 1 1 0 0 0 1 → 1 b3 0 1 0 0 1 0 → 0 b4 0 0 0 0 0 1 → 1 b5 0 0 1 0 0 0 → 1 b6 1 1 0 1 1 1 → 1 0 0 0 1 0 0 → 1 VRC↓ Paridad (impar) Fig. 7.3. Mecanismo de paridad vertical impar y paridad horizontal par 7.3.6. Códigos Matriciales (Array Codes) Los códigos matriciales son códigos de detección y corrección de error , y en su forma más sencilla, son una generalización del código SRC pero extendido a dos dimensiones. En efecto, a la prueba de paridad horizontal se le agrega una prueba de 429 VII. TECNICAS DE CONTROL DE ERROR paridad vertical y una prueba de prueba, lo que permite no sólo detectar sino corregir un error en el bloque transmitido. En estos códigos se utiliza la paridad par. En la Fig. 7.4 se muestra la Matriz Principal, la Submatriz y el mecanismo de codificación. Prueba Horizontal C columnas EJEMPLO: Palabra Dato: 1 1 1 1 0 0 F filas Paridad Par Prueba Vertical F x C dígitos de Información Prueba de Prueba (a) Matriz de (F +1)x (C +1) dígitos 1 1 1 1 1 0 0 1 0 1 1 0 Palabra Codificada: 111110010110 (b) Matriz de Codificación y Secuencia Transmitida Fig. 7.4. Generación del Código Matricial La palabra dato se distribuye en la Submatriz de F filas y C columnas. En los códigos matriciales la matriz principal generalmente es rectangular y C > F; la matriz será cuadrada cuando C = F. El rendimiento y la redundancia serán E= C⋅F ; (C + 1)(F + 1) R =1- E = C + F +1 (C + 1)(F + 1) (7.6) Sea m el número de dígitos de información y k el de redundancia. Se tiene entonces, n = m + k = (C + 1)(F + 1); m = C ⋅ F; k = C + F + 1; E = m k y R= m n Para la matriz de la Fig. 7.4(b), m = 6; k = 6; n = m + k = 12; C = 3; F = 2; E =1/2 ; R = 1/2. La palabra código de longitud n se puede transmitir en un formato apropiado, por ejemplo, serialmente por filas o columnas, o paralelamente en (F+1) secuencias paralelas. Cuando las pruebas de paridad vertical y horizontal fallan, es decir, que se detecta un error en un dígito, este error puede ser corregido de inmediato pues su emplazamiento se conoce con exactitud, como se puede apreciar en la Fig. 7.5. 430 VII. TECNICAS DE CONTROL DE ERROR Dígito en error 1 0 1 0 1 1 1 0 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 101001011111 (a) Bloque enviado en Serie por Filas 1 0 1 1 0 1 0 1 1 1 111001011111 (b) Bloque Recibido. Error en un dígito de información Dígito en error 1 0 1 0 1 0 1 0 1 1 1 1 1 0 101101011111 (c) Bloque Recibido. Error en un dígito de prueba Dígito en error 101001011110 (d) Bloque Recibido. Error en el dígito de prueba de prueba Fig. 7. 5. Mecanismo de Corrección de Error. Los códigos matriciales son muy eficientes en lo que se refiere a la corrección de errores, particularmente si la matriz es cuadrada. Estos códigos pueden extenderse también a más de dos dimensiones. ♣ Ejemplo 7.4 Código Matricial. Se recibió la siguiente secuencia codificada 011011101100111001011011011101 Diga cuál fue la palabra mensaje transmitida y el rendimiento de transmisión. Solución: 011011101100111001011011011101 Son 30 dígitos = 5 filas x 6 columnas Los 30 dígitos se colocan en una matriz de 5 filas por 6 columnas y se verifica la paridad tanto horizontal como verticalmente. Puede observarse que la paridad no se verifica en el dígito B3 que debe entonces ser CERO. Por lo tanto, la palabra mensaje transmitida fue 0110110010111000110101110 1 2 3 4 5 6 A 0 1 1 0 1 1 B 1 0 1 1 0 0 C 1 1 1 0 0 1 D 0 1 1 0 1 1 E 0 1 1 1 0 1 431 VII. TECNICAS DE CONTROL DE ERROR En cuanto al rendimiento, E% = 4x5 100 = 66,6% 5x 6 ♣ 7.3.7. Código de Hamming Dentro de la clase de códigos detectores/correctores de error el código Hamming es un código óptimo aún más eficiente que los códigos matriciales. La teoría de este código es muy compleja pero vamos a explicar su aplicación en una forma algorítmica. Los pasos de aplicación del algoritmo de Hamming son los siguientes (ver la TABLA No. 1): Algoritmo de Codificación Hamming (1) Considere que la palabra dato tiene la forma LSB d1 d2 d3 d4 MSB dm donde m es el número de dígitos de la palabra dato. (2) Con este valor de m seleccione la longitud n del bloque en la columna 1 de la Tabla No.1 o en la Tabla No. 2. Por ejemplo, para m = 8 → n = 12. (3) En la columna 2, Tabla No. 1, identifique las posiciones que son potencias enteras de 2i (i = 0, 1, 2,….), es decir, 20 = 1 → posición 1; 21 = 2 → posición 2; 2 2 = 4 → posición 4; etc. TABLA No. 1. CODIFICACION DE HAMMING ← 7 c4 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 6 c3 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 5 c2 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 4 c1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 3 ck/dm c1 c2 d1 c3 d2 d3 d4 c4 d5 d6 d7 d8 d9 d10 d11 2 2i 20 21 22 23 - 1 n 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 432 VII. TECNICAS DE CONTROL DE ERROR (4) En la columna 3 coloque los dígitos de paridad c1, c2, c3, …… en las posiciones identificadas en (3), y en el resto de las posiciones coloque los dígitos de información d1, d2, d3,…… La columna 3 constituye la “palabra codificada clave”, la cual tendrá la forma (remarcada en la Tabla No.1) Sentido del Flujo de Datos c1 c2 d1 c3 d2 d3 d4 c4 d5 m dígitos de información k dígitos de paridad n=m+k Para facilitar la descodificación, se envía primero los m dígitos de información seguidos de los k dígitos de paridad. La palabra codificada transmitida tendrá entonces la forma Sentido del Flujo de Datos DATOS BCC d1 d2 d3 dm c1 c2 LSB ck MSB (5) En las columnas 4 en adelante escriba en binario los números del 1 al n, e identifique la columna 4 con c1, la 5 con c2 y así sucesivamente, como se muestra en la Tabla No. 1. (6) La ecuación para cada dígito de paridad ci, se obtiene directamente de las columnas 4 en adelante. Por ejemplo, se suman en módulo 2 todos los dígitos de información dj cuya expresión en la columna 4 contiene un UNO. El cálculo de los Dígitos de Paridad para n ≤ 15, m ≤ 11 y k ≤ 4 nos da: c1 = d1 ⊕ d2 ⊕ d4 ⊕ d5 ⊕ d7 ⊕ d9 ⊕ d11 c2 = d1 ⊕ d3 ⊕ d4 ⊕ d6 ⊕ d7 ⊕ d10 ⊕ d11 c3 = d2 ⊕ d3 ⊕ d4 ⊕ d8 ⊕ d9 ⊕ d10 ⊕ d11 (7.7) c4 = d5 ⊕ d6 ⊕ d7 ⊕ d8 ⊕ d9 ⊕ d10 ⊕ d11 ................................................ Si 2 k ≥ (n + 1) > 2 k −1 entonces 2 k ≥ m + k + 1; también k ≥ log 2 (n + 1) . La Tabla se puede extender para cualquier valor de n. Estas relaciones nos permiten determinar m, k ó n cuando se conocen o establecen las otras dos. El rendimiento y la redundancia son: E% = k m m k 100 = 100 100 = 100; R% = n m+k m+k n (7.8) 433 VII. TECNICAS DE CONTROL DE ERROR En la Tabla 2 se muestra la relación entre estas variables. TABLA No. 2. Relación entre m, k, n, E y R m 3 4 5 6 7 8 9 10 11 k 3 3 4 4 4 4 4 4 4 n 6 7 9 10 11 12 13 14 15 E% 50 57 56 60 64 67 69 71 73 R% 50 43 44 40 36 33 31 29 27 Algoritmo de Descodificación Hamming Para la descodificación y corrección de error se siguen los siguientes pasos: (1) En el receptor se recalculan los dígitos de paridad a partir de los dígitos de información de la palabra codificada recibida. (2) Los dígitos de paridad recalculados c ,i y los recibidos ci se suman dígito a dígito en módulo 2 obteniéndose una expresión denominada “síndrome”, es decir, k Síndrome = S = ∑ c i ⊕ c ,i (7.9) i =1 (3) Si el síndrome S es una k-tupla formada por puros CEROS, entonces se supone que no hubo error en la transmisión. (4) Si el síndrome S es distinto de CERO (contiene por lo menos un UNO), entonces se lee en sentido inverso (el dígito menos significativo pasa a ser el más significativo y así sucesivamente). El valor del inverso del síndrome indica la posición en la Tabla No. 1, columna 1, de un error sencillo en la palabra codificada clave de la columna 3, el cual se puede corregir. ♣ Ejemplo 7.5 Supongamos que la palabra codificada recibida fue la de la figura DATOS Recalculemos la paridad: c1, = 1 ⊕ 1 ⊕ 0 = 0; c ,2 = 1 ⊕ 1 ⊕ 0 = 0; c ,3 = 1 ⊕ 1 ⊕ 0 = 0 d1 d2 d3 d4 c1 c2 c3 1 Cálculo del síndrome: Dígitos de paridad recalculados c i' Dígitos de paridad recibidos ci Síndrome BCC S = 1 1 0 0 1 0 0 0 1 0 1 0 1 1 ≠ 0 1 434 VII. TECNICAS DE CONTROL DE ERROR Puesto que el síndrome es distinto de cero, hubo error en la transmisión. Corrección del error: Inversión del síndrome c3 c2 c1 Síndrome invertido 1 1 0 ≡ Por consiguiente, en la Tabla No. 1, posición 6, columna 1, hay un error correspondiente al dígito d3 de la columna 3, el cual se puede corregir cambiando el UNO por un CERO. La palabra codificada correcta transmitida fue entonces ♣ 6 d1 d2 d3 d4 c1 c2 c3 1 1 0 0 0 1 1 Se han desarrollado otros códigos FEC y ARQ, entre los cuales se tiene los códigos cíclicos y los códigos convolucionales. Entre los códigos cíclicos el más conocido es el código CRC que describiremos a continuación. 7.3.8. Códigos de Redundancia Cíclica (CRC) Uno de los esquemas de detección de error más eficiente en cuanto a su instrumentación (circuitería) es el denominado Código de Redundancia Cíclica (Cyclic Redundancy Code, CRC), que es uno de la clase de los códigos cíclicos. La detección de errores se efectúa mediante un registro de desplazamiento de varias secciones que alimentan compuertas O-Exc, como se muestra en la Fig. 7.6. Entrada de Datos 16 LSB 0 1 2 3 4 X 5 6 7 8 12 X MSB 11 12 13 14 15 9 10 X (a) 5 X 0 Entrada de un "1" 0 0 0 1 0 Secuencia de Entrada (Datos) 1 0 Reloj de Sincronización 0 0 0 0 0 1 0 0 0 0 1 (b) 1 0 0 1 (c) Fig. 7.6. Registro CRC UIT-T V.41. Utilizado en los Protocolos SDLC y HDLC En la Fig. 7.6(a) se muestra la configuración normalizada por el UIT-T en su Recomendación V.41, aunque hay dos tipos más de configuración, llamadas CRC-16 y CRC-12, que veremos más adelante. Nótese que los dígitos LSB y MSB se refieren al registro: el lado LSB corresponde al término X16 y se envía de primero, es decir, es el primer dígito del BCC. 435 VII. TECNICAS DE CONTROL DE ERROR Previo a la codificación, el registro se inicializa a cero. A medida que cada dígito de datos se presenta en la primera compuerta O-Exc, se va desplazando el contenido del registro y se efectúan las operaciones correspondientes. En la Fig. 7.6(b) se muestra el contenido del registro cuando el primer dígito fue un UNO. Este dígito UNO se desplaza a cada impulso del reloj de sincronización y eventualmente llegará a las otras compuertas afectando el contenido del registro. La consecuencia general que debe tenerse en cuenta es que el efecto de un dígito cualquiera se refleja en las diferentes células del registro durante un tiempo bastante grande después que el mismo dígito fue transmitido. Al finalizar la codificación de un mensaje, la estación transmisora envía el mensaje propiamente más el contenido del registro, el cual es el BCC correspondiente, formando el mensaje codificado. En cuanto al receptor, la configuración del registro es idéntica a la del transmisor: el registro se inicializa a cero y los dígitos recibidos se aplican a su entrada. Finalizada la recepción del mensaje codificado, si el mensaje recibido es igual al mensaje transmitido, el contenido del registro será cero, es decir, el registro contendrá sólo CEROS. Esta situación se verifica no importa la forma de conexión de las compuertas O-Exc, de ahí que existan varios tipos de código CRC. Una excepción es en los protocolos SDLC y HDLC en los cuales el registro se inicializa con un valor predeterminado y al final de la codificación el contenido es distinto de cero (0 0 0 1 11 0 1 0 0 0 0 1111) . En los protocolos SDLC y HDLC a la secuencia BCC del registro se la denomina FCS (frame check sequence). La característica más importante del CRC es que debido a su forma realimentada el estado exacto del registro depende en gran parte de su historia pasada. Como consecuencia, es muy poco probable que una ráfaga de errores pueda producir un cálculo en el CRC que sea igual a la secuencia de datos tal como fue transmitida antes de la ocurrencia de los errores. La teoría matemática que justifica la utilización de este código es sumamente compleja y no se dará detalles de la misma. Sin embargo, vamos a explicar su aplicación práctica en una forma algorítmica y mediante ejemplos. Un mensaje codificado en forma cíclica consiste en una secuencia específica de datos y un BCC. Sea n igual al número total de dígitos del mensaje codificado o palabra código, y m el número de dígitos de información; entonces, el BCC tendrá (n – m) dígitos. El mensaje codificado se deduce de dos polinomios que son representaciones algebraicas de dos secuencias binarias: el polinomio generador PG(X) de k dígitos y el polinomio mensaje M(X) de m dígitos. El polinomio generador identifica el tipo de código (CRC UIT-T, CRC-12, CRC-16, etc.), y el polinomio mensaje es simplemente la secuencia de dígitos de información. Estos polinomios son expresiones algebraicas de la forma X p + X p −1 + X p − 2 + ... + X 3 + X 2 + X 1 + X 0 Para su representación en forma binaria, se coloca un “1” en las posiciones donde X ≠ 0, y un “0” cuando X = 0. La convención establecida es la de colocar el término X0 (que es igual a 1) a la derecha. Por ejemplo, una expresión algebraica o polinomio de la forma X5 + X3 + X + 1 se representará en binario en la forma 1 0 1 0 1 1. El grado de este 436 VII. TECNICAS DE CONTROL DE ERROR polinomio es 5, el término Xp con p = 5 representa el LSB y la secuencia binaria correspondiente tendrá p + 1 = 6 dígitos. El LSB siempre se coloca a la izquierda. El BCC está representado por un polinomio B(X) y el polinomio que representa la señal transmitida tendrá la forma T(X) = M’(X) + B(X) = Xn-mM(X) + B(X) de n dígitos. El polinomio B(X) se elige de tal manera que el polinomio T(X) sea exactamente divisible por el polinomio generador PG(X). En otras palabras, B(X) es el resto que resulta cuando el polinomio M’(X) se divide por el polinomio generador PG(X), es decir, M(X) M ' (X) = Cociente exacto de + B(X) PG (X) PG (X) También, (7.10 ) T(X) = M’(X) + B(X), donde M’(X) = Xn-mM(X) (7.11) Las operaciones expresadas en (7.10) y (7.11) se pueden realizar en binario mediante el algoritmo siguiente: 1. M’(X) se obtiene multiplicando el polinomio mensaje M(X) por Xn-m donde (n − m) es el número de dígitos del BCC. La multiplicación de Xn-m por M(X) en binario equivale a agregar (n – m) ceros a la forma binaria de M(X). 2. El producto resultante Xn-m M(X) se divide por el polinomio generador PG(X) y se calcula el resto B(X), es decir, se efectúa una división módulo 2. Entonces, M(X) X n −m M (X) = Cociente exacto de + B(X) PG (X) PG (X) La forma binaria de B(X) es el BCC. 3. En binario, el polinomio T(X) tendrá la forma siguiente: T(X) = Xn-m M(X) + B(X) = M’(X) + B(X) T(X) es el mensaje codificado que se transmite y que tendrá el siguiente formato Nótese que en la práctica m >> (n – m); por ejemplo, en transmision X.25 el LSB T(X) Dirección del Flujo de Datos MSB LSB DATOS m dígitos MSB BCC (n - m) dígitos n dígitos valor de m puede llegar a 32808, mientras que (n – m) = 16. 4. En el receptor el mensaje codificado T(X) recibido se divide por el mismo polinomio generador PG(X). Si no hay errores en la transmisión, la división será exacta y el resto B(X) será cero. Si el resto B(X) es distinto de cero, hubo errores en la transmisión y se demandará la repetición del bloque correspondiente. Las operaciones 1 a 4 son efectuadas por el registro de la Fig. 7.6. 437 VII. TECNICAS DE CONTROL DE ERROR La división (paso 2) se efectúa en binario sin “excesos” (carriers) ni “defectos” (borrows). En este caso, el resto B(X) siempre tendrá un dígito menos que el polinomio generador PG(X). Por lo tanto, se verifica que n – m = k - 1, de donde n = m + k - 1. El número de dígitos de B(X) es k – 1 y su grado k - 2. En la práctica m >> k, lo que implica que el rendimiento de este código es muy bueno. ♣ Ejemplo de aplicación del CRC UIT-T Rec. V.41, Fig. 7.6. Sea M(X) = X7 + X5 + X4 +X + 1 => 1 0 1 1 0 0 1 1 ; m = 8 dígitos 7 X corresponde al LSB de M(X). PG(X) = X16 + X12 + X5 + 1 => 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1; k = 17 dígitos X16 corresponde al LSB de PG(X). BCC → n – m = k - 1 = 16 dígitos y n = m + k - 1 = 24 dígitos 1. Producto Xn-m M(X) = X16(X7 + X5 + X4 + X + 1) = X23 + X21 + X20 + X17 + X16 Xn-m M(X) => 1 0 1 1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 → 24 dígitos 2. División del producto Xn-m M(X) por PG(X): 101100110000000000000000 : 10001000000100001 10001000000100001 0011101100010000100 El Cociente no se utiliza 10001000000100001 011001000101001010 10001000000100001 010000001011010110 10001000000100001 00001001011110111000 => B(X) => 1001011110111000 → 16 dígitos 2. El resto B(X) se suma al producto Xn-m m(X) para obtener T(X): Xn-m M(X) → 101100110000000000000000 1001011110111000 + B(X) → T(X) → 101100111001011110111000 => 24 dígitos T(X) se transmite; es un bloque de 24 dígitos. Nótese que T(X) es ahora divisible (en módulo 2) por PG(x). 438 VII. TECNICAS DE CONTROL DE ERROR 3. En el receptor se divide T(X) por PG(X): 101100111001011110111000 : 10001000000100001 10001000000100001 0011101110000111001 El Cociente no se utiliza 10001000000100001 011001100000110001 10001000000100001 010001000000100001 10001000000100001 00000000000000000 => Resto R(X) = 0 No hubo error en la transmisión. Si hubiera habido un error en el T(X) recibido, el Resto hubiera sido distinto de cero. ♣ En general, en el transmisor el BCC se calcula y se acumula en un registro de desplazamiento y se agrega al mensaje formando la palabra codificada a transmitir. La configuración del registro depende del código CRC que se quiere instrumentar. El número de etapas del registro es igual al grado k del polinomio generador y el número de compuertas O-Exc es también una función del polinomio. En la Fig. 7.6 se mostró el registro utilizado para el código CRC UIT–T cuyo polinomio es PG(X) = X16 + X12 + X5 + 1. Cuando opera con caracteres de 8 dígitos (un octeto) el BCC tendrá 2 octetos, como se pudo apreciar en el ejemplo de aplicación. En la Fig. 7.7 se muestra los códigos CRC-12 y CRC-16; los polinomios correspondientes son: CRC-12: PG(X) = X12 + X11 + X3 + X2 + X + 1 CRC-16: PG(X) = X16 + X15 + X2 + 1 Entrada de Datos 12 LSB 0 1 X 2 3 4 5 6 7 8 11 9 3 X X (a) Código CRC-12. Utilizado en el Transcódigo de 6 dígitos 2 MSB 11 10 X X 1 Entrada de Datos 16 X LSB 0 15 1 2 3 4 5 6 7 8 MSB 14 15 9 10 11 12 13 X 2 X (b) Código CRC-16. Utilizado en los Protocolos BSC y DDCMP Fig. 7.7. Codificadores CRC de aplicación práctica. 1 439 VII. TECNICAS DE CONTROL DE ERROR El polinomio generador del CRC utilizado en las Redes Ethernet tiene la forma PG(X) = X32 + X26 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X + 1 mientras que en el protocolo industrial DNP 3.0 se utiliza el polinomio PG(X) = X16 + X13 + X12 + X11 + X10 + X8 + X6 + X5 + X2 + 1 Los códigos CRC detectan todos los errores sencillos y dobles, todos los errores con un número impar de dígitos, todas las ráfagas de errores de longitud igual o menor de 16 dígitos, el 99,997% de las ráfagas de 17 dígitos y el 99,998% de todas las ráfagas iguales o superiores a 18 dígitos. Por esta razón, los códigos CRC son muy utilizados para el control de error en los sistemas de telecomunicaciones. El rendimiento de los códigos CRC es excelente, casi del 100% puesto que m >> k. En general, la instrumentación de este código es muy sencilla, como se puede ver en las figuras 7.6 y 7.7. Matemáticamente, los códigos CRC son códigos de bloque lineales. En la codificación lineal el grupo de m dígitos de información es aplicado al codificador, el cual responde con un bloque codificado de n dígitos que depende solamente de los m dígitos de entrada; cada bloque es procesado independientemente de los demás. Por esta razón estos códigos son llamados “códigos de bloque lineales (n, m)”, y como siempre hay redundancia agregada, siempre se verifica que n > m. El CRC no es el único código de bloque lineal; en la práctica se encuentran también los códigos Golay y BCH (Bose-Chaudhuri-Hocquenghem) que solamente nombraremos. Los códigos descritos hasta ahora, con la excepción del código de ponderación constante, son ejemplos de los códigos lineales cuyas palabras codificadas están formadas por los dígitos de información más los dígitos de redundancia. Los códigos de ponderación constante en general son códigos no lineales. Los códigos pueden ser no lineales ya sea porque ellos no tienen una estructura de “ información + redundancia” o porque contienen dígitos de paridad no lineales, es decir, que no son módulo 2. Los códigos lineales tienen un alto grado de complejidad matemática, pero al mismo tiempo esa estructura matemática compleja los hace relativamente simples para sintetizar, codificar y descodificar. Por otro lado, los códigos no lineales son en general difíciles de sintetizar y procesar. Para más información sobre los códigos cíclicos y convolucionales, ver la Bibliografía y la Recomendación UIT-T V.41. 440 VII. TECNICAS DE CONTROL DE ERROR 7.4. PRINCIPIO DE LA ALEATORIZACION 7.4.1. Introducción En los sistemas de transmisión digital se utiliza una técnica denominada “aleatorización” o “seudoaleatorización” (scrambling) que permite la regeneración de los impulsos del reloj de sincronización y por lo tanto previene la generación de errores en las secuencias recibidas. El “scrambling” es otra forma de codificación de canal. La operación de un código no debería depender de las estadísticas de la secuencia binaria y no imponer restricciones sobre el tipo de información a transmitir; por ejemplo, no debería causar problemas de sincronización una secuencia de varios ceros seguidos. Muchos códigos funcionan de acuerdo con lo previsto por la teoría sólo cuando los UNOS y los CEROS ocurren con igual probabilidad, y cuando la ocurrencia de un CERO o un UNO cualquiera es independiente de los UNOS o CEROS anteriores o posteriores. Esta situación no siempre se da y por eso a veces es necesario utilizar técnicas que mezclan o desordenan (scramblers) los dígitos para que la secuencia parezca más aleatoria. Por supuesto, en el destino hay que “desaleatorizar” o reordenar los dígitos a su forma original para que la información no se destruya. Un sistema de transmisión digital en principio acepta cualquiera secuencia arbitraria de dígitos y la reproduce exactamente a su salida sin más efecto en la secuencia que la introducción de un retardo fijo debido a la propagación. En la práctica, la secuencia se puede reproducir de manera inexacta, esto es, puede contener errores en la transmisión y el retardo puede variar originando una fluctuación de temporización. Si estos efectos se presentan aleatoriamente y son substancialmente independientes de la secuencia real transmitida, se dice que el sistema es independiente de las secuencias de dígitos y los errores se pueden detectar y/o corregir con los esquemas que hemos visto. Sin embargo, puede que en la práctica no suceda así y que se observe que la presencia de errores y de fluctuación depende de la configuración de los dígitos que constituyen la secuencia transmitida. Vamos a ilustrar esta situación con un ejemplo sencillo. Supongamos que se transmite secuencias binarias NRZ. Si las secuencias contienen largas cadenas de sólo UNOS o sólo CEROS, el receptor será incapaz de regenerar los impulsos de reloj y se producirá errores en la secuencia recibida. La idea fundamental en que se basa la seudoaleatorizacion, es, pues, la de reducir la probabilidad de errores modificando la secuencia transmitida en tal forma que se reduzca la probabilidad de aparición de secuencias particulares que podrían causar dificultades, es decir, hay que hacer que la secuencia transmitida sea o parezca lo más aleatoria posible. Una ventaja adicional de la seudoaleatorización es que centra al espectro en el canal disminuyendo las componentes espectrales en los bordes de la banda que podrían producir interferencia en los canales adyacentes, y con la eliminación de componentes continuas se impide la aparición de impulsos periódicos en el espectro. 441 VII. TECNICAS DE CONTROL DE ERROR 7.4.2. Seudoaleatorizador Autosincronizante El seudoaleatorizador autosincronizante es un dispositivo comúnmente utilizado en los Módems de las Series V y X del UIT-T. Este es un dispositivo de realimentación hacia adelante en un registro de desplazamiento de varias secciones que alimentan compuertas OExc, como se muestra en la Fig. 7.8(a) y (b). Esta configuración básica es la empleada en los Módems UIT-T V.27, en los cuales, mediante ciertos mecanismos de guarda, el sistema puede evitar secuencias repetidas de 1, 2, 3, 4 y 12 dígitos. En la práctica este circuito se construye de tal manera que no permite transiciones en la salida en los instantes de reloj. El reloj actúa solamente sobre el registro. X(n) Entrada de Datos Datos transmitidos Y(n) Z(n) Y(n) Datos recibidos Salida de Datos 7 6 5 4 3 2 1 (a) Aleatorizador o Desordenador 1 2 3 4 5 6 7 (b) Desaleatorizador o Reordenador Fig. 7.8. Aleatorizador y Desaleatorizador UIT-T V.27. La estructura de los aleatorizadores nos permite caracterizarlos mediante un polinomio generador, como se hizo para los códigos CRC. Por ejemplo, el aleatorizador V.27 de la Fig. 7.8 se puede caracterizar mediante el polinomio PG(X) = X7 + X6 + 1. Podemos demostrar fácilmente que la secuencia Z(n) de salida es igual a la secuencia de entrada X(n). En efecto, sea X(n) la entrada en un intervalo n cualquiera. Como cada una de las células del registro produce retardos unitarios, entonces de la Fig. 7.8(a), Y(n) = X(n) ⊕ [Y(n-6) ⊕ Y(n-7)] (7.12) Donde Y(n) es la salida del aleatorizador y entrada del desaleatorizador. También, de la Fig. 7.8(b), Z(n) = Y(n) ⊕ [Y(n-6) ⊕ Y(n-7)] (7.13) Reemplazando (7.12 ) en (7.13), Z(n) = X(n) ⊕ Y(n-6) ⊕ Y(n-7) ⊕ Y(n-6) ⊕ Y(n-7) Z(n) = X(n) ⊕ [Y(n-6) ⊕ Y(n-6)] ⊕ [Y(n-7) ⊕ Y(n-7)] Pero en la suma modulo 2 se verifica que Y(n-6) ⊕ Y(n-6) = Y(n-7) ⊕ Y(n-7) = 0; 0 ⊕ 0 = 0 y Entonces, Z(n) = X(n) ⊕ 0 ⊕ 0 = X(n) ⊕ 0 = X(n) X(n) ⊕ 0 = X(n) 442 VII. TECNICAS DE CONTROL DE ERROR El lector puede verificar que si la secuencia de entrada al aleatorizador tiene la forma 1 1 0 0 1 1 0 1, la secuencia de salida del aleatorizador será 0 0 0 0 1 1 0 1. Si esta secuencia se aplica al desaleatorizador, a su salida se recuperará la secuencia original (La flecha indica el sentido del flujo de datos, y se supone que el registro ha sido inicializado a cero antes de la codificación). La ventaja de este tipo de seudoaleatorización consiste en que es autosincronizante, es decir, que no necesita ningún reloj suplementario para su sincronización. El mayor inconveniente estriba en que produce una extensión o aumento de los errores. Si durante la transmisión ocurre errores en los dígitos, la salida resultante después de suprimida la seudoaleatorización contendrá errores adicionales, uno por cada derivación utilizada en el registro de desplazamiento. Supongamos que el registro tiene una longitud de X elementos y contiene Y derivaciones (incluida la derivación de entrada). El efecto de la desaleatorización será aumentar la proporción de errores en un factor aproximadamente igual a Y y extender en X dígitos la longitud de toda ráfaga de errores. Una solución para el problema de la extensión de errores con seudoaleatorizadores autosincronizantes es su emplazamiento en la cadena de transmisión. Normalmente el aleatorizador se sitúa inmediatamente antes del enlace de transmisión con el desaleatorizador inmediatamente después del enlace. Con esta disposición los descodificadores de control de error se encuentran antes del desaleatorizador con lo que la extensión de errores causada por este último no perturba el proceso de corrección de errores. Además, si el corrector de errores es capaz de corregir la mayoría de los errores de transmisión, habrá menos errores que lleguen al desaleatorizador para que éste los extienda. En la Fig. 7. 9 se muestra esta disposición. ALEATORIZADOR CODEC FEC ENLACE CODEC FEC DESALEATORIZADOR Fig. 7.9. Emplazamiento de los Aleatorizadores/Desaleatorizadores. En conclusión, los seudoaleatorizadores autosincronizantes son eficaces para suprimir la dependencia de la secuencia, pero introducen una extensión de los errores. La consecuencia es que cualquier dispositivo de corrección de errores que se utilice de esa forma para mantener un sistema de transmisión bastante flexible, tendría que ser mucho más complicado. El problema de extensión de errores se puede evitar utilizando un tipo distinto de seudoaleatorizador, denominado “seudoaleatorizador de reposición” en el que se genera una secuencia seudoaleatoria de longitud máxima que se suma a la secuencia transmitida. En el receptor se genera una secuencia seudoaleatoria idéntica que se resta de la secuencia transmitida. Mientras las secuencias seudoaleatorias estén en fase, las dos operaciones se anulan mutuamente y se recupera la secuencia original transmitida. En esta forma no se produce extensión de error. Para mantener los generadores de secuencias seudoaleatorias en fase, es necesario enviar información adicional de sincronización, lo que se traduce en un 443 VII. TECNICAS DE CONTROL DE ERROR aumento de la velocidad de modulación y de la complejidad de los equipos para procesar la información de sincronismo. En ciertos casos se puede aprovechar señales existentes de alineación de trama para la sincronización del desaleatorizador. Los procesos de aleatorización y desaleatorización son ampliamente utilizados en los Módems V.26, V.27, V.27 bis, V.27 ter, V.29, V.32, V.35 y V.36. En la Fig. 7.10 se muestra el circuito utilizado en el Módem V.27. o Desaleat Salida de Datos oAleat Registro de Desplazamiento dígitos 6 7 9 0 Entrada de Datos o :32 o o :2 o J Q o _ K Q 12 o Reloj Invierte un dígito de datos Reset Retardo Reloj Fig. 7.10. Aleatorizador/Desaleatorizador del Módem UIT-T V.27. 444 VII. TECNICAS DE CONTROL DE ERROR 7.5. Resumen Durante la transmisión de información digital a través de un sistema o canal se producen errores prácticamente inevitables debido a la presencia de ruido y a otros factores tales como la interferencia intersímbolo, la intermodulación, la fluctuación de fase, ecos, etc. Es por ello necesario establecer maneras, si nó para evitar los errores, por lo menos para poder reconocer su presencia y si es posible corregirlos. En los sistemas de comunicación actuales el control de error se efectúa mediante la aplicación de códigos especiales que agregan redundancia. Esta redundancia agregada permite detectar y/o corregir los errores ocurridos durante la transmisión de los bloques de datos. En este capítulo vamos a describir en forma algorítmica algunos de los códigos más utilizados para la detección y/o corrección de errores. Cuando se recibe un bloque de dígitos binarios es necesario asegurarse de que no contiene errores de transmisión. Si se detecta que el bloque está en error, se tiene dos opciones: una es corregir el error en el sitio y la otra solicitar la retransmisión del bloque. Esta situación ha producido las dos técnicas de control de error comúnmente utilizadas: la “Corrección Directa de Error (Forward Error Correction, FEC)” y la “Solicitud de Repetición Automática (Automatic Repeat Request, ARQ)”. En la técnica FEC se utiliza códigos para detectar y corregir los errores en el receptor; mientras que en la técnica ARQ los códigos solamente detectan la presencia de errores en los datos recibidos y se solicita en alguna forma la repetición de los bloques que vienen en error. En este capítulo se define, en primer lugar, el rendimiento y la redundancia de un código, que son los parámetros para determinar la eficacia de un código determinado. Hay otros parámetros tales como la “distancia mínima”, la “capacidad de detección de ráfagas” y otros que citamos pero que no describimos pues están fuera del marco de este libro. Los esquemas para la detección y/o corrección que se describen en este capítulo son: código de repetición, códigos de ponderación constante, codigo de suma de verificación, código de prueba de paridad sencilla, código de prueba de paridad vertical y horizontal, códigos matriciales, código de Hamming y códigos de redundancia cíclica (CRC). Por ser el Código CRC muy utilizado en muchos de los protocolos de comunicación vistos hasta ahora, su descripción es más detallada, aunque no entramos en su justificación teórica. Aunque la aleatorización no es un esquema de control de error, su descripción y operación descansa sobre los mismos principios de los códigos CRC. En particular, la aleatorización permite la regeneración de los impulsos de reloj y por lo tanto previene la generación de errores en las secuencias de datos transmitidas. En este capítulo se introduce solamente la noción de lo que es la aleatorización y sobre qué principios se basa, así como algunos tipos de aleatorizador utilizados en la práctica. 445 VII. TECNICAS DE CONTROL DE ERROR 7.5. CUESTIONARIO 1. Explique las razones fundamentales para la utilización de la detección y corrección de errores, y en qué sitios del sistema deben colocarse los dispositivos que efectúan las funciones de codificación y descodificación. 2. Defina lo que es el “Rendimiento de un Código” y explique su significado. ¿Para qué se le agrega “Redundancia” a un código dado? Se observa una palabra codificada con paridad sencilla, ¿ Cómo se puede reconocer si la paridad es par o impar? 3. En control de error ARQ, se tienen diferentes formas para solicitar la repetición del bloque o bloques en error. Investigue los esquemas más utilizados en la práctica. 4. En el Código de Ponderación Constante, escriba todas las secuencias de longitud 6 que contienen 4 UNOS. ¿Cuál es el valor de la redundancia? 5. En el protocolo XMODEM determine el valor (en decimal) y la forma (en binario) del BCC cuando el campo Información contiene 38 caracteres X, 30 caracteres Y, 30 caracteres Z y 30 caracteres W. 6. La palabra MURCIELAGO se va a transmitir con codificación horizontal y vertical en la forma mostrada en la Fig. 7.3. Demuestre que el BCC es 0 0 0 0 0 0 0 0. 7. En un sistema que utiliza un código matricial se recibió la siguiente palabra código: 101101101000011111100100111010 Diga si hay error en la transmisión y cuál fue la palabra mensaje transmitida. ¿Cuál es el valor de la redundancia? 8. Utilizando el código matricial se quiere transmitir la palabra 10110011001001110111. Construya la matriz principal, muestre la forma de la palabra código transmitida y determine la redundancia. 9. En un sistema que utiliza el código Hamming se recibió siguiente la palabra código: DATOS BCC 10011110 0000 Verifique si hay error en la transmisión. Si ese es el caso, diga cuál dígito está en error. ¿ Cuál es el valor de la redundancia? 10. En un sistema que utiliza el código de Hamming la palabra mensaje tiene la forma 1 0 0 1 1 0 1 0 1 1 . Demuestre que la palabra codificada transmitida tiene la forma 1 0 0 1 1 0 1 0 1 1 1 0 1 0. 11. Diga las características principales de los Códigos CRC y los más utilizados en la práctica. 12. Dibuje el registro CRC cuyo polinomio generador es PG(X) = X8 + X4 + X2 + 1. 13. Dibuje los registros CRC utilizados en la LAN Ethernet y en el protocolo industrial DNP 3.0. 446 VII. TECNICAS DE CONTROL DE ERROR 14. En el código CRC-12 el polinomio generador es PG(X) = X12 + X11 + X3 + X2 + X + 1 y el polinomio mensaje es M(X) = X7 + X4 + X2 + X + 1. Demuestre que el mensaje codificado transmitido T(X) es 1 0 0 1 0 1 1 1 1 1 0 1 1 0 0 1 0 0 1 1. 15. Sea un código CRC cuyo polinomio generador es P(X) = X5 + X4 + X + 1 y el polinomio mensaje M(X) = X7 + X5 + X4 + X2 + X + 1. Demuestre que el BCC tiene la forma B(X) => 01001 16. En el protocolo DNP 3.0 el polinomio mensaje es M(X) = X7 + X5 + X3 + X + 1. Determine el mensaje codificado transmitido T(X). 17. Diga las características, funciones y aplicaciones de la aleatorización. 18. Dibuje el aleatorizador y el desaleatorizador de un sistema dado, si el aleatorizador puede representar con un polinomio generador de la forma PG(X) = X7 + X5 + 1. se