- Ninguna Categoria

Instrucciones del PIC

Anuncio

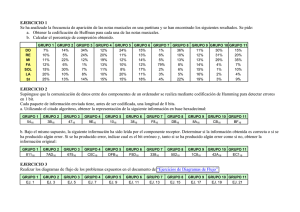

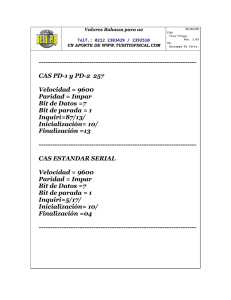

UTP – FIEM – ELECTRÓNICA – 2011 – I CIRCUITOS DIGITALES II Microcontroladores Pic 16F84A. Los PIC son una extensa familia de microcontroladores divididos en tres gamas, la gama baja con memoria de programa de 12 bits, la gama media y la gama alta con memoria de programa de 14 bits. En la tabla 1 se presentan algunos miembros de cada una de estas gamas con resumen de sus principales características. Nosotros utilizaremos el PIC 16f84 por sus especiales características. Los microcontroladores PIC 16f84 com memoria tipo FLASH y PIC 16c84 con memoria EEPROM, son potentes, flexibles y fáciles de emplear debido entre otras carcterísticas a que este tipo de memoria permite su grabación y su borrado miles de veces de forma casi instantánea al realizarse eléctricamente a diferencia de los microcontroladores basados en memoria EPROM que necesita un borrador ultravioleta. Pueden utilizarse tanto en el desarrollo como en la producción. Su coste se reduce frente a otros modelos ya que no necesitan encapsulados cerámicos con ventana de programación como los chips EPRPOMs. Disponen ademas de una EEPROM de 64 bytes para datos, lo que elimina la necesidad de una memoria EEPROM externa, y aun mas importante, pueden ser programados "en circuito" sin necesidad de ser retirados, lo que permite su grabación después del ensamblado y que los programas pueden ser actualizados o modificados para eliminar errores detectados con posterioridad o para introducir versiones mas actualizadas del programa. El PIC 16f84 pertenece a la gama media del fabricante, poseyendo unas características óptimas para su empleo en el aprendizaje. Este microntrolador con memoria FLASH ésta fabricado con tecnología CMOS. Su consumo es muy reducido siendo el circuito completamente estático por lo que su reloj puede detenerse completamente sin pérdida de los contenidos de los registros. Un consumo típico es de 2 mA a 4 Mhz y unos 40 microamperios en modo Sleep. Al ser un circuito CMOS, todas las entradas no usadas deben ser llevadas a +5V. El encapsulado de 18 pines así como la descripción del patillaje puede verse en la figura 1. Set de instrucciones Microcontrolador PIC. Estas son las todas las instrucciones que hay para poder programar el Pic 16c5x, 16c64, 16c71, 16c74, 16c84, 16f84, 16f873. Las encontraremos en orden alfabetico. En total son 37 y haciendo un clic sobre una de ellas podemos acceder a su respectiva descripción: NOTA: Las instrucciones OPTION y TRIS incluidas en este listado, no forman parte del set de instrucciones de los PIC 16f84 y 16f873. DOCENTE: Ing. Luis Pacheco Cribillero JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I CIRCUITOS DIGITALES II ADDLW CALL ADDWF ANDLW ANDWF BCF BSF BTFSC BTFSS CLRF CLRW CLRWDT COMF DECF DECFSZ GOTO ADDLW ADD Literal to W ADDWF ADD W to F Sintaxis ADDLW k Sintaxis ADDWF f, d Codificación 11 Codificación Palabras, Ciclos 1, 1 0001 11df 00 0111 dfff Operación W + k -> W Palabras, Ciclos 1, 1 111x kkkk SLEEP SUBLW SUBWF SWAPF TRIS XORLW XORWF kkkk Añade el contenido de W al contenido de k, y almacena el resultado en W Descripción Atención: Esta instrucción no existe en los Pic 16c5X Operación W + f -> W si d=0 Bit estado de C, DC, Z Añade el contenido de W al contenido de f, y almacena el Descripción resultado en W si d=0, y en f si d=1 ANDLW AND Literal and W ANDWF AND W with F Sintaxis ANDLW k Sintaxis ANDWF f, d Codificación 0001 01df ffff 00 0101 dfff Palabras, Ciclos 1, 1 Palabras, Ciclos 1, 1 Operación W AND k -> W Bit estado Z ffff W + f -> f si d=1 Bit de estado C, DC, Z Codificación 1110 kkkk kkkk 11 1001 kkkk ffff Kkkk ffff W AND f -> f si d=1 de Operación W AND f -> W si d=0 Efectúa un AND lógico entre el contenido de W y el Descripción literal k, y lo almacena en W DOCENTE: Ing. Luis Pacheco Cribillero Bit estado de Z Efectúa un AND lógico entre el contenido de W y Descripción el contenido de f, y almacena el resultado en W si d=0, y en f si d=1 JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I CIRCUITOS DIGITALES II BCF Bit Clear F BSF Bit Set F Sintaxis BCF f, b Sintaxis BSF f, b Codificación 0101 bbbf ffff 01 01bb bfff Palabras, Ciclos 1, 1 Operación 1 -> b(f) Bit estado Ninguno Codificación 0100 bbbf ffff 01 00bb bfff Palabras, Ciclos 1, 1 Operación 0 -> b(f) Bit estado de ffff Ninguno de Descripción Pone a uno el bit numero b de f Descripción Pone a cero el bit numero b de f BTFSC Bit Test, Skip If Clear BTFSS Bit Test, Skip If Set Sintaxis BTFSC f, b Sintaxis BTFSS f, b Codificación 0110 bbbf ffff 01 10bb bfff ffff Codificación 0111 01 Palabras, Ciclos 1, 1 o 2 Palabras, Ciclos 1, 1 o 2 Operación Salta si b(f)=0 Operación Salta si b(f)=1 Bit estado Ninguno Bit estado Ninguno de Si el bit numero b de f es nulo, la instrucción que sigue a esta se ignora y se Descripción trata como un NOP. En este caso, y solo en este caso, la instrucción BTFSC precisa dos ciclos para ejecutarse. de bbbf 11bb ffff bfff Subrutina Call CLRF Clear F with F Sintaxis CALL k Sintaxis CLRF f Codificación 1001 kkkk kkkk 10 0kkk kkkk Palabras, Ciclos 1, 2 Operación En el caso de los 16c64, 71, 74, 84: PC + 1 -> Pila, k -> PC(0-10), PCLATH(3,4) -> PC(11,12) Bit estado de Descripción Guarda Codificación 0000 011f 00 Ninguno la DOCENTE: Ing. Luis Pacheco Cribillero dirección de ffff Si el bit numero b de f esta en uno, la instrucción que sigue a esta se ignora y se trata Descripción como un NOP. En este caso, y solo en este caso, la instrucción BTFSC precisa dos ciclos para ejecutarse. CALL kkkk ffff 0001 1fff Palabras, Ciclos 1, 1 Operación 00 -> f Bit estado Z de Descripción ffff ffff Pone el contenido de f a cero y activa el bit Z. JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I CIRCUITOS DIGITALES II vuelta en la pila y después llama a la subrutina situada en la dirección cargada en el PC. Atención: En el modo de cálculo de la dirección hay que posicionar bien el registro PCLATH antes de ejecutar la instrucción CALL CLRW Clear W register CLRWDT Clear Watchdog Timer Sintaxis CLRW Sintaxis CLRWDT Codificación 0000 0100 0000 00 0001 0xxx xxxx Codificación 0000 0000 0100 00 0000 0110 0100 Palabras, Ciclos 1, 1 Palabras, Ciclos 1, 1 Operación 00 -> W Operación Bit estado 00 -> WDT y 0 -> predivisor del temporizador Z Bit estado 1 -> TO y 1 -> PD de Pone el registro W a cero y Descripción activa el bit Z de Pone a cero el registro contador del temporizador Descripción watchdog, asi como el predivisor COMF Complement F DECF Decrement F to F Sintaxis COMF f, d Sintaxis DECF f, d Codificación 0010 01df ffff 00 1001 dfff Codificación 0000 11df ffff 00 0011 dfff Palabras, Ciclos 1, 1 Palabras, Ciclos ffff 1, 1 ~f -> f su d=1 Operación ~f -> W si d=0 Bit estado de Z Hace un complemento de f bit a bit. El resultado lo Descripción almacena de nuevo en f si d=1 (borra el anterior), o en W si d=0 (f no varía) DECFSZ Decrement F, Skip If Zero Sintaxis DECFSZ f, d DOCENTE: Ing. Luis Pacheco Cribillero ffff f - 1 -> f si d=1 Operación f - 1 -> W si d=0 Bit estado de Z Decrementa el contenido de f en una unidad. El Descripción resultado se guarda en W si d=0 (f no varia), y en f si d=1 GOTO Salto Incondicional with F JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I Codificación Palabras, Ciclos 0010 11df ffff 00 1011 dfff CIRCUITOS DIGITALES II ffff Sintaxis GOTO k Codificación 101k kkkk kkkk 10 1kkk kkkk Palabras, Ciclos 1, 2 Operación En el caso de los 16c64,71,74 y 84: k -> PC(0-10), PCLATH(3,4) -> PC(11,12) Bit estado Ninguno 1, 1(2) f - 1 -> f si d=1 Operación f - 1 -> W si d=0 Bit estado de Ninguno Decrementa el contenido de f en una unidad. El resultado se guarda en W si d=0 (f no varia), y en f si d=1 de LLama a la subrutina situada en la dirección cargada en el PC Descripción Si el reusltado es nulo, se ignora la siguiente instrucción y en este caso la instrucción dura dos ciclos. kkkk Descripción Atención: En el modo de cálculo de la dirección hay que posicionar correctamente el registro PCLATH antes de ejecutar la instrucción GOTO INCF Increment F INCFSZ Increment F, Skip if Zero Sintaxis INCF f, d Sintaxis INCFSZ f, d Codificación 0010 10df ffff 00 1010 dfff Codificación 0011 11df ffff 00 1111 dfff Palabras, Ciclos 1, 1 Palabras, Ciclos 1, 1(2) ffff f + 1 -> f si d=1 ffff f + 1 -> f si d=1 Operación f + 1 -> W si d=0 Bit estado de Operación Z Incrementa el contenido de f en una unidad. El resultado se almacena de Descripción nuevo en f si d=1 y en W si d=0(en este caso f no varía) Bit estado de f + 1 -> W si d=0 En ambos casos: Salto si f +1=0 Ninguno Incrementa el contenido de f en 1. El resultado se guarda en f si d=1 y en w si d=0 (en este caso f no Descripción varía). Si el resultado es nulo, se ignora la siguiente instrucción y esta instrucción dura dos ciclos IORLW Inclusive OR Literal With W IORWF Inclusive OR W With f Sintaxis IORLW k Sintaxis IORWF f, d Codificación DOCENTE: Ing. Luis Pacheco Cribillero Codificación JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I 1101 11 kkkk 1000 Palabras, Ciclos 1, 1 Operación W OR k -> W Bit estado de CIRCUITOS DIGITALES II kkkk kkkk 0001 00df ffff 11 0100 dfff kkkk Palabras, Ciclos ffff 1, 1 W OR f -> f si d=1 Operación Z W OR f -> W si d=0 Efectúa un OR lógico inclusivo entre el contenido de Descripción W y el literal K, y almacena el resultado en W Bit estado de Z Efectúa un OR lógico inclusivo entre el contenido de W y el Descripción contenido de f, y almacena el resultado en f si d=1 o en W si d=0 MOVF Move F MOVLW Move Literal to W with F Sintaxis MOVF f, d Sintaxis MOVLW k Codificación 0010 00df ffff 00 1000 dfff Codificación 1100 kkkk kkkk 11 00xx kkkk 1, 1 Palabras, Ciclos 1, 1 f -> f si d=1 Operación k -> W f -> W si d=0 Bit estado Ninguno Z Descripción Carga W con el literal k Palabras, Ciclos ffff Operación Bit estado de de kkkk Pone el contenido de f en f si d=1 o f en W si d=0 Atención: El desplazamiento de f en f Descripción que parecería inútil, permite comprobar el contenido de f con respecto a cero ya que esta instrucción actúa sobre el bit Z MOVWF Move W to F NOP No Operation Sintaxis MOVWF f Sintaxis NOP Codificación 0000 001f ffff 00 0000 1fff Codificación 0000 0000 0000 00 0xx0 0000 Palabras, Ciclos 1, 1 Palabras, Ciclos 1, 1 Operación W -> f Operación Ninguna DOCENTE: Ing. Luis Pacheco Cribillero ffff JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I Bit estado de CIRCUITOS DIGITALES II Bit estado Ninguno de Ninguna Descripción Carga f con el contenido de W OPTION Load Option Register RETFIE Return From Interrupt Sintaxis Option Sintaxis RETFIE Codificación 0000 0000 0010 00 0000 0110 0010 Codificación 00 1, 2 Palabras, Ciclos Palabras, Ciclos 1, 1 Operación Pila -> PC, 1 -> GIE Operación W -> OPTION Ninguno Bit estado Bit estado Ninguno Carga el PC con el valor que se encuentra en la parte superior de la pila, asegurando así la vuelta de la interrupción. Pone a 1 el bit GIE, con el fin de Descripción autorizar de nuevo que se tengan en cuenta las interrupciones de Carga el registro OPTION con el contenido de W Atención: Esta instrucción Descripción es correctamente interpretada por los circuitos 16c64, 71, 74, 84 con el fin de asegurar una compatibilidad ascendente RETLW Return Literal to W Sintaxis RETLW k 1000 kkkk kkkk Codificación 11 01xx kkkk kkkk Consume tiempo de la maquina y ocupa un lugar Descripción en la memoria de programa. de 0000 0000 1001 Atención: Esta interrupción dura dos ciclos RETURN Return from Subroutine with F Sintaxis RETURN Codificación 00 0000 0000 0000 1, 2 Palabras, Ciclos 1, 2 Operación k -> W, Pila -> PC Operación Pila -> PC Bit estado Ninguno Bit estado Ninguno Palabras, Ciclos de Carga W con el literal k, y después carga el PC con el valor que se encuentra en la parte superior de la pila, Descripción efectuando así un retorno de subrutina. Atención: Esta instrucción dura dos ciclos DOCENTE: Ing. Luis Pacheco Cribillero de Carga el PC con el valor que se encuentra en la parte superior de la pila, efectuando así una vuelta a Descripción la subrutina. Se trata de la instrucción RETLW simplificada. Atención: Esta instrucción dura dos ciclos JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I CIRCUITOS DIGITALES II RLF Rotate Left F through Carry Sintaxis RLF f,d 0011 Codificación 00 01df 1101 Palabras, Ciclos 1, 1 Operación ver descr. Bit estado C de ffff dfff ffff Rotación de un bit a la izquierda del contenido de f, pasando por el bit de acarreo Descripción C. Si d=1 el resultado se almacena en f si d=0 el resultado se almacena en W RRF Rotate Right F through Carry Sintaxis RRF f, d Codificación 0011 00df ffff 00 1100 dfff Palabras, Ciclos 1, 1 Operación Ver descr. Bit estado C de ffff Rotación de un bit a la derecha del contenido de f, pasando por el bit de Descripción acarreo C. Si d=1 el resultado se introduce en f, si d=0 el resultado se amacena en W SLEEP Sleep SUBLW Substract W from Literal Sintaxis SLEEP Sintaxis SUBLW k Codificación 0000 0000 0011 00 0000 0110 0011 Codificación 11 1, 1 Palabras, Ciclos Palabras, Ciclos 1, 1 Operación k - W -> W Operación 0 -> PD, 1 -> TO, 00 -> WDT, 0 -> Predivisor del WDT Bit estado C, DC, Z Bit estado de PD, TO Pone el circuito a dormir con parada del oscilador. Su consumo es inferior. Descripción de 110x kkkk Sustrae el contenido de W del literal k, y almacena el Descripción resultado en W. La sustracción se realiza en complemento a dos Atención: Use esta instrucción con mucho cuidado, pues puede provocar que el micro no despierte si no se ha seteado correctamente. SUBWF Substract W from F SWAPF Swap F to F Sintaxis SUBWF f, d Sintaxis SWAPF f, d Codificación 0000 10df ffff 00 0010 dfff Codificación 0011 11df ffff 00 1110 dfff Palabras, 1, 1 Palabras, kkkk 1, 1 DOCENTE: Ing. Luis Pacheco Cribillero ffff ffff JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I CIRCUITOS DIGITALES II Ciclos Ciclos f - W -> f si d=1 f(0-3) -> f(4-7) y f(4-7) -> f(0-3) Operación f - W -> W si d=0 Bit estado de Operación Resultado -> f si d=1 Resultado -> W si d=0 C, DC, Z Sustrae el contenido de W del contenido de f, y almacena el resultado en Descripción W si d=0 y en f si d=1. La sustracción se realiza en complemento a dos TRIS Load TRIS Register Sintaxis TRIS f 0000 0000 0fff Codificación 00 0000 0110 0fff Palabras, Ciclos 1, 1 Operación W -> registro TRIS del puerto f Bit estado Ninguno de Carga el contenido de W en el registro TRIS del puerto f. Descripción Atención: Esta instrucción, es correctamente interpretada por los circuitos 16c64, 71, 74, 84, con el fin de asegurar una compatibilidad ascendente Bit estado de Ninguno Intercambia los cuatro bit de mayor peso por los Descripción cuatro de menor peso de f, y almacena el resultado en W si d=0, y en f si d=1 XORLW Exclusive OR Literal With W Sintaxis XORLW k Codificación 1111 kkkk kkkk 11 1010 kkkk Palabras, Ciclos 1, 1 Operación W OR (Exclusivo) k -> W Bit estado Z de kkkk Efectúa un OR lógico exclusivo entre el contenido de W y el Descripción contenido del Literal K y almacena el resultado en W XORWF Exclusive Or W with F Sintaxis XORWF f,d Codificación 0001 00 Palabras, Ciclos 1, 1 Operación W OR (Exclusivo) W OR (Exclusivo) f -> W si d=0 Bit de estado Z Descripción Efectúa un Or lógico exclusivo entre el contenido de W y el contenido de f y almacena el resultado en f si d=1 o en W si d=0 DOCENTE: Ing. Luis Pacheco Cribillero 10df 0110 ffff dfff f ffff -> f si d=1 JUEGO DE INSTRUCCIONES UTP – FIEM – ELECTRÓNICA – 2011 – I DOCENTE: Ing. Luis Pacheco Cribillero CIRCUITOS DIGITALES II JUEGO DE INSTRUCCIONES

Anuncio

Documentos relacionados

Descargar

Anuncio

Añadir este documento a la recogida (s)

Puede agregar este documento a su colección de estudio (s)

Iniciar sesión Disponible sólo para usuarios autorizadosAñadir a este documento guardado

Puede agregar este documento a su lista guardada

Iniciar sesión Disponible sólo para usuarios autorizados