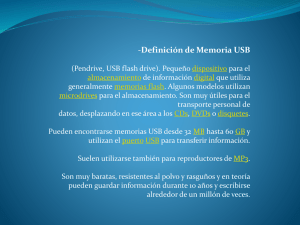

1 interfaz usb de almacenamiento de datos en memorias flash

Anuncio