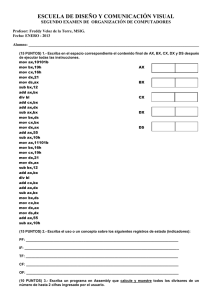

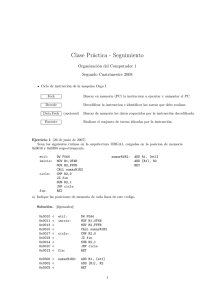

Arquitectura y lenguaje ensamblador Orga1

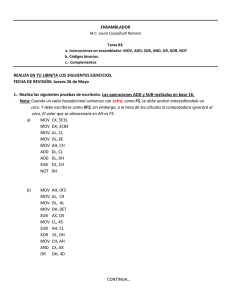

Anuncio

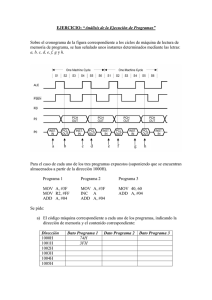

Arquitectura ORGA1 Lenguaje Ensamblador (MOV, ADD, CMP,ect.) Microcódigo (...) Lógica Digital (Flip­flops, clocks, etc) Arquitectura ORGA1 • Arquitectura Von Neumann • Palabras de 16 bits • Espacio de memoria de 65.535 palabras ( 0x0000 a 0xFFFF) • Direccionamiento a Palabra • 8 registros de propósito general de 16 bits (R0 a R7) • 2 registros de propósito específico de 16 bits: – Program counter (PC) – stack pointer (SP) Arquitectura ORGA1 4 Flags: Z, N, C y V – Z: El resultado es el numeral 0 – N: El resultado es “negativo” (complemento a 2) – C: La suma bit­a­bit produjo acarreo – V: Hubo “overflow” (complemento a 2) Algunas instrucciones alteran los flags, otras no lo hacen Arquitectura ORGA1 R0 R1 .... R7 0000 010A .... 4F00 PC SP Z N C V 0141 FFEF 0 1 1 0 CPU 0000 0001 .... 0141 .... AD1B 010A .... 11FF .... FFFF 0C02 ¿Qué cosas puedo hacer con esta máquina? Memoria Arquitectura ORGA1­ Instrucciones Instrucción MOV (mover) Formato: MOV Destino, Fuente Copia el contenido de “Fuente” en “Destino”, pisando este último. ¿Pero qué pueden ser “Destino” y “Fuente”? Arquitectura ORGA1­ Instrucciones Instrucción MOV (mover) Formato: MOV Destino, Fuente Copia el contenido de “Fuente” en “Destino”, pisando este último. ¿Pero qué pueden ser “Destino” y “Fuente”? Abramos un paréntesis para aprender sobre modos de direccionamiento de la máquina ORGA1. ( Arquitectura ORGA1 ­ Modos de direccionamiento Inmediato Destino o fuente es una constante de 16 bits. Por ejemplo 0xFFFF, 0x8000, 0x0000, etc... Registro Destino o fuente hacen referencia a uno de los 8 registros. Los registros se nombran como: R0, R1, etc… Ejemplos: 3. Poner R0 en 0x0: 4. Poner R1 en 0xFFFF: MOV R0, 0x0000 MOV R1, 0xFFFF Arquitectura ORGA1 – Modos de direccionamiento Pero con solo esos dos, no puedo interactuar con la memoria… Para eso necesito modos de direccionamiento mas complicados… Bienvenidos al fantástico mundo de los punteros! Direccionamiento directo Destino o fuente son una constante de 16 bits, pero que representa una de mis 65.535 direcciones de memoria. Para indicar que estamos usando este modo de direccionamiento, ponemos la constante entre corchetes. Ejemplos: 3. Guardar el valor 0x0001 en la posición de memoria 0x0000: 4. Guardar el contenido de la dirección 0x0001 en la dirección 0x0000: 5. Guardar el contenido de la dirección de 0x0000 en R0: 6. Guardar el contenido de R0 en la dirección 0x0002: MOV [0x0000], 0x0001 MOV [0x0000], [0x0001] MOV R0, [0x0000] MOV [0x0002], R0 Arquitectura ORGA1 – Modos de direccionamiento Direccionamiento indirecto Destino o fuente son una constante de 16 bits, que ahora representa una de mis 65.535 direcciones de memoria, pero en donde yo antes guardé un puntero. Para indicar que estoy usando este modo, uso doble corchete. Ejemplos: 2. Guardar 0x0004 en la dirección a la que apunta el contenido de la dirección 0x0000: 3. Guardar 0x0004 en la dirección a la que apunta el contenido de la dirección 0x0002: 4. Guardar en R0 el contenido de la posición a la que apunta el contenido de la dirección 0x0002: MOV [[0x0000]], 0x0004 MOV [[0x0000]], 0x0004 MOV R0, [[0x0002]] Arquitectura ORGA1 – Modos de direccionamiento Pero con solo esos dos, no puedo interactuar con la memoria… Para eso necesito modos de direccionamiento mas complicados… Direccionamiento indirecto mediante registro Destino o fuente son un registro, en donde guardé un puntero. Es similar al indirecto, pero utilizando un registro en lugar de una posición de memoria. También uso corchetes. Ejemplos: MOV [R0], 0x0004 3. Guardar un 4 en la posición de memoria a la que apunta R0: 4. Guardar en R1 el contenido de memoria al que apunta R0: MOV R1, [R0] Arquitectura ORGA1 – Modos de direccionamiento Pero con solo esos dos, no puedo interactuar con la memoria… Para eso necesito modos de direccionamiento mas complicados… Direccionamiento indirecto mediante registro + índice Destino o fuente son un registro, en donde guardé un puntero, al que le sumo una constante de 16 bits. Es similar al anterior. Ejemplos: 2. Guardar un 4 en la posición de memoria a la que apunta R0 desplazado por 1: 3. Guardar en R1 el contenido apuntado por R0 desplazado por 3: MOV [R0 + 0x0001], 0x0004 MOV R1, [R0 + 0x0003] Arquitectura ORGA1 – Instrucciones ) Fin del paréntesis sobre modos de direccionamiento. Instrucción ADD (sumar) Formato: ADD Destino, Fuente Hace la operación Destino + Fuente, y guarda el resultado en Destino. Instrucción SUB (restar) Formato: SUB Destino, Fuente Hace la operación Destino ­ Fuente, y guarda el resultado en Destino. Para ello invierte el signo de Fuente y realiza una suma, pero el valor de Fuente no es alterado por la operación. Arquitectura ORGA1 – Instrucciones Instrucción AND (and bit­a­bit) Formato: AND Destino, Fuente Hace la operación Destino AND Fuente, y guarda el resultado en Destino. Instrucción OR (and bit­a­bit) Formato: OR Destino, Fuente Hace la operación Destino OR Fuente, y guarda el resultado en Destino. Instrucción NOT (not bit­a­bit) Formato: NOT Destino Hace la operación NOT Destino y guarda el resultado en Destino. Arquitectura ORGA1 – Instrucciones Instrucción NEG (negación complemento a 2) Formato: NEG Destino Invierte el signo (complemento a 2 de 16 bits) de Destino, y guarda el resultado en Destino. Ejemplos: 2. Sumar R0 y la dirección 00F0 3. Restar la dirección 1FFF y la dirección a la que apunta la dirección 1FFFF 4. Realizar el AND bit­a­bit de la dirección 1FF0 y la dirección a la que apunta R0 5. Realizar el OR bit­a­bit de la dirección a la que apunta R0 y R0 6. Realizar el NOT bit­a­bit de la dirección a la que apunta R0 desplazado en 4 7. Negar R4 desplazado ­2 ADD R0, [0x00F0] SUB [0x1FFF], [[0x1FFF]] AND [0x1FF0],[R0] OR [R0],R0 NOT [R4+0xFFFE] Arquitectura ORGA1 – Instrucciones Instrucciones de comparación y salto Instrucción JMP (saltar) Formato: JMP Fuente Sobreescribe el PC con el contenido de la fuente Ejemplos: Saltar a la dirección 0x00FF Saltar a la dirección 0x1EFE JMP 0x00FF JMP 0x1EFE Arquitectura ORGA1 – Instrucciones Instrucciones de comparación y salto Instrucción CMP (comparar) Formato: CMP Destino, Fuente Funciona “como si hiciera” lo mismo que SUB Destino, Fuente… Pero no altera los registros. Sólo cambia los flags. Arquitectura ORGA1 – Instrucciones ¿Cuáles eran los flags? Z: Zero N: Negative C: Carry V: oVerflow Todas las instrucciones alteran los flags, menos MOV y las instrucciones de salto. Tampoco las alteran CALL y RET (que vamos a ver mas adelante). C y V quedan siempre en 0, salvo cuando hacemos ADD, SUB, CMP y NEG. Arquitectura ORGA1 – Instrucciones La movida de los flags es así: N: Está “cableada” al bit mas significativo del resultado. Es el equivalente al bit de signo si los números están codificados en complemento a 2 de 16 bits. Prendería con: MOV R0, 0x0000 ADD R0, 0x8000 MOV R0, 0x0000 SUB R0, 0x0004 NEG 0x0001 Arquitectura ORGA1 – Instrucciones La movida de los flags es así: Z: Se prende cuando la operación da el numeral 0000 como resultado. Por ejemplo: MOV R0, 0x0000 ADD R0, 0x0000 MOV R1, 0x0000 SUB R0, R1 MOV R0, 0x0004 CMP R0, 0x0004 o SUB R0, 0x0004 NEG 0x0000 Arquitectura ORGA1 – Instrucciones La movida de los flags es así: C: Se prende cuando hay carry. Por ejemplo: MOV R0, 0x7FFF ADD R0, 0x000F V: Se prende cuando hay oVerflow (complemento a 2, 16 bits) Prendería con: MOV R0, 0x7FFF ADD R0, 0x000F Arquitectura ORGA1 – Instrucciones Leyendo estos flags se implementan las instrucciones de salto: Jxx Desplazamiento: PC=PC+Desplazamiento Operación Descripción Condición de salto. JE Igual / Cero Z JNE No Igual not Z JLE Menor o Igual Z or ( N xor V) JG Mayor not (Z or (N xor V)) JL Menor N xor V JGE Mayor o Igual not (N xor V) JLEU Menor o Igual sin signo C or Z JGU Mayor sin signo not (C or Z) JCS Carry / Menor sin signo C JNEG Negativo N JVS Overflow V Instrucciones ORGA1­ Codificación Ejercicio: ¿Cuál es el valor del PC luego de ejecutar estas instrucciones? Pc antes condición Pc después Condición 00F1: JLE 0xFF ; Z=1 0075: JVS 0x12 ; V=1 000E: JGU 0x12 ; C=1 Z=0 009E: JG 0x55 ; C=1 Z=0 N=0 V=1 Arquitectura ORGA1 ­ Recapitulando... Con una máquina ORGA1 podemos: • Mover bits (MOV) • Aritmética: ADD, SUB, NEG • Lógica: AND, OR, NOT • Comparar: CMP • Saltar: Jxx's Ejercicio 1: Escribir el siguiente pseudo­código en lenguaje ensamblador ORGA1. El programa comienza en la dirección 00F0 de memoria. Utilizar el registro R0 como contenedor de la variable i. i := 15 Mientras i!=0 i:=i­1 Fin Mientras Problema: Tenemos que definir el desplazamiento de cada salto condicional 3. Tedioso 4. Necesitamos conocer la codificación de cada instr. Lenguaje Ensamblador ORGA1 ­ Etiquetas El lenguaje ensamblador de ORGA1 soporta ETIQUETAS. Cada instrucción puede ser “decorada” con una etiqueta. Los valores finales de las etiquetas son RESUELTOS por el programa ensamblador. Ciclo: MOV R0, 0 ADD R0, 1 CMP R0, 000F JLEU Ciclo RET Ejercicio 1 (ahora sí): Escribir el siguiente pseudo­código en lenguaje ensamblador ORGA1... i := 15 inicio: MOV R0, 0x000F Mientras i!=0 mientras: CMP R0,0x000 i:=i­1 JE finMientras ; salto condicional Fin Mientras SUB R0, 0x0001 JMP mientras ; salto absoluto finMientras: ... Lenguaje Ensamblador ORGA1 ­ Valores Además de etiquetas, el lenguaje ensamblador de la máquina ORGA1 soporta la definición explícita de valores usando el keyword DW (Define Word) Valor: Inicio: JMP Inicio DW 0A0A MOV R0, [Valor] ADD R0, 000F MOV [Valor], R0 RET Ejercicio 2: Escribir el siguiente pseudo­código en lenguaje ORGA1. No puede utilizar ningún registro como contenedor de la variable i i := 15 Mientras i!=0 i:=i­1 Fin Mientras Arquitectura ORGA1 – Instrucciones CALL y RET: Llamado a “procedimiento” CALL Destino Guarda en el stack la dirección de memoria de la próxima instrucción, y salta incondicionalmente a Destino. Fin de “procedimiento” RET Saca del tope del stack una dirección de memoria, y salta incondicionalmente a ella. Ejemplo: Invocar el procedimiento en 0xFF3F Invocar la etiqueta PROC1 Retornar al procedimiento que llamó Saltar a la dirección 0xFF3F Saltar a la etiqueta Seguir CALL 0xFF3F CALL PROC1 RET JMP 0xFF3F JMP Seguir (programa) Ensamblador ORGA1 – Recapitulando... Lenguaje Ensamblador ORGA1 (ya vimos) Valor: DW 00FF MOV R0,[Valor] Ciclo: ADD R0,1 JZ Salir JMP Ciclo Salir: RET... Dirección de inicio del programa (programa) Ensamblador ORGA1 •Codifica instrucciones y operandos •Resuelve etiquetas (usa codificación) •Resuelve valores (DW) Lenguaje Máquina ORGA1 (ya veremos) 0001 100000 000000 0000 000011 1111111 0001 100001 000000 0001 000000 0000000 0010 100000 100001 ... (programa) Ensamblador ORGA1 – Recapitulando... Inicio: ADD R0,R1 JMP Inicio 00FF: ADD R0,R1 JMP 0x00FF EA00: ADD R0,R1 JMP 0xEA00 Inicio: ADD R0,R1 JE Inicio 00FF: ADD R0,R1 JE 0xFD EA00: ADD R0,R1 JE 0xFD La codificación de algunas instrucciones dependerá del valor de la dir. de inicio del programa La codificación de algunas instrucciones no depende del valor de inicio del programa Estas codificaciones son resueltas por el (programa) ENSAMBLADOR Ejercicio: Escribir en lenguaje ensamblador ORGA1 el procediemiento RecorrerLista. Este programa recorre una lista simplemente encadenada buscando un valor. • El puntero a la cabeza de la lista está en el registro R1. • El valor buscando está apuntado por el registro R2. • Los nodos tienen 2 palabras. • La primer palabra es el valor • La segunda palabra es el puntero al próximo nodo • El valor de puntero 0xFFFF representa que no hay más nodos. • Indicar si encontró el valor escribiendo en R3 el valor 0x0001, sino escribir 0x0000 Una solución Pseudo­código: RecorrerLista: MOV R4, R1 MOV R3, 0x0000 Mientras: CMP R4,0xFFFF JE FinMientras CMP [R4],[R2] JNE FinSi MOV R3,0x0001 JMP FinMientras FinSi: MOV R4, [R4+0x0001] JMP Mientras Fin Mientras: RET Pseudo­código: Programa RecorrerLista ptr := R1 R3 := 0x0000 Mientras ptr!=0xFFFF Si primer[ptr]=[R2] R3:=0x0001 Fin Si ptr := segundo[ptr] Fin Mientras Fin Programa Tarea: Cambiar el programa de modo de no usar el registro R4 como temporal Máquina ORGA1 Ensamblar (a mano/ automáticamente) •Resolver etiquetas •Transforma símbolos en 0's y 1's •Necesita codificación Lenguaje Ensamblador MOV R0,0x00FF MOV R1,0x1000 ADD R0,R1... Etiquetas Valores 0001 100000 000000 0000 0000 1111 11111 0001 100001 000000 0001 0000 0000 00000 0010 100000 100001 ... Lenguaje Máquina Desensamblar (a mano/automáticamente) ¿qué perdimos? Instrucciones ORGA1­ Codificación Tipo 1: Instrucciones de 2 operandos: Abramos un paréntesis para conocer la codificación de los modos de direccionamiento de la máquina ORGA1. ( Instrucciones ORGA1­ Codificación Codificación modos de direccionamiento operandos Ejemplos: ADD R0,R1 ADD R0,0x0010 ADD R0,[0x0010] ADD R0,[0x0000] Las instrucciones que tienen en Dest operandos del tipo Inmediato son consideredas como inválidas por el procesador. Ejemplo: 0x1000 0xFFFF 0xF000 Fin del paréntesis sobre modos de direccionamiento. ) Instrucciones ORGA1­ Codificación Tipo 2a: Instrucciones de 1 operando Destino Tipo 2b: Instrucciones de 1 operando Fuente Ejemplos: NOT R0 NEG [0x00FF] JMP R0 CALL [[0xFF1F]] Instrucciones ORGA1­ Codificación Tipo 3: Instrucciones sin operandos Ejemplos: ? Instrucciones ORGA1­ Codificación Tipo 4: Saltos condicionales