Tarea Sistemas digitales Profa: Sully Sánchez Gálvez 1. Analice el

Anuncio

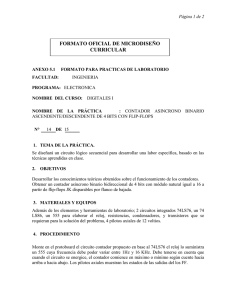

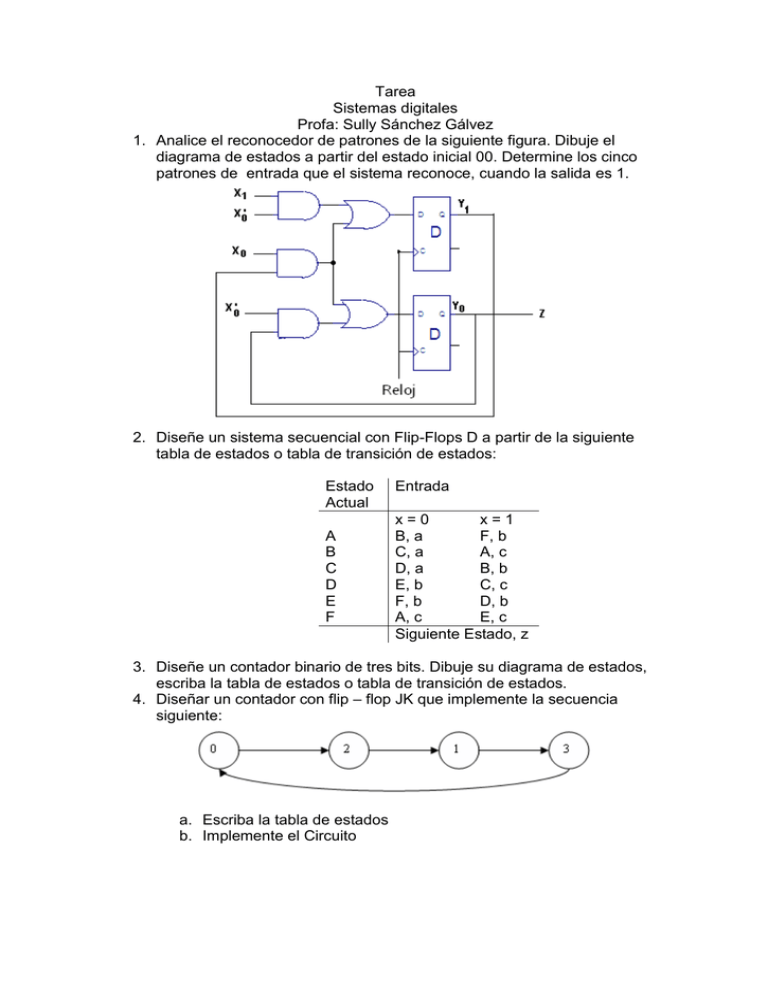

Tarea Sistemas digitales Profa: Sully Sánchez Gálvez 1. Analice el reconocedor de patrones de la siguiente figura. Dibuje el diagrama de estados a partir del estado inicial 00. Determine los cinco patrones de entrada que el sistema reconoce, cuando la salida es 1. 2. Diseñe un sistema secuencial con Flip-Flops D a partir de la siguiente tabla de estados o tabla de transición de estados: Estado Actual A B C D E F Entrada x=0 x=1 B, a F, b C, a A, c D, a B, b E, b C, c F, b D, b A, c E, c Siguiente Estado, z 3. Diseñe un contador binario de tres bits. Dibuje su diagrama de estados, escriba la tabla de estados o tabla de transición de estados. 4. Diseñar un contador con flip – flop JK que implemente la secuencia siguiente: a. Escriba la tabla de estados b. Implemente el Circuito 5. En la siguiente máquina de estado la entrada es X y la salida es Z: a. Hallar la tabla de transición de estados b. Realizar el diagrama de estados 6. Derive la tabla de estados para el circuito de la figura y el diagrama de estados 7. El circuito de la figura parece un contador ¿Cuál es la secuencia en que cuenta? 8. Diseñe un contador ascendente/descendente de tres bits con flip-flops T. Debe incluir una entrada de control llamada Up /Down. Si Up /Down=0, entonces el circuito debe comportarse como un contador ascendente. Si es igual a 1, entonces el circuito debe comportarse como un contador descendente. 9. El diagrama de estados de la figura es un ejemplo de un detector de secuencia. En general, el detector de secuencia. En general, el detector de secuencia se usa para buscar en un flujo de entrada de bits una se 10. Determine la tabla de estados, el diagrama de estados y el tipo de circuito para el siguiente diagrama. 11. Verifique si la sintaxis del siguiente programa es correcta y posteriormente determine su diagrama de estados y la tabla de estados. Library________ Use _____ entity _____ is port Clk, x: in std_logic; Z:out std_logic); End Architecture __of___is TYPE estados is (d0,d1,d2,d3); Signal edo_presente, edo_futuro:estados; Begin Proceso1:process edo_presente, x) begin Case edo_presente is When d0=>z<=´’0’; If x=’1’ then Edo_futuro<=d1; Else Edo_futuro<=d0 End if; When d1=>z<=’0’; If x=1 then Edo_futuro<=d2 Else Edo_futuro<=d1; End if; When d2>z<=’0’; If x=1then Edo_futuro<=d3 Else Edo_futuro<=d0; End if; When d3=> If x=’1’ then Edo_futuro<=d0; Z<=’1’; Else Edo_futuro <=d3; Z<=0 End if; End case; End process proceso1; Proceso2: process clk) begin If (clk’event and clk=’1’) then Edo_presente<=edo_futuro; End if; End process proceso2; end ____; 12. Implemente el circuito secuencial indicado por el siguiente diagrama de estados usando flip-flops tipo JK 13. Consulte el contador que se muestra en la figura ¿Cómo se puede saber si se trata de un contador descendente? Ha sido modificado de manera que no cuenta a través de la secuencia binaria completa 111 a 000. Determine la secuencia real a la que cuenta. 14. Diseñe un contador síncrono que tenga la siguiente secuencia: 000, 010, 101, 110 y repita.