Síntesis - S3 amazonaws com

Anuncio

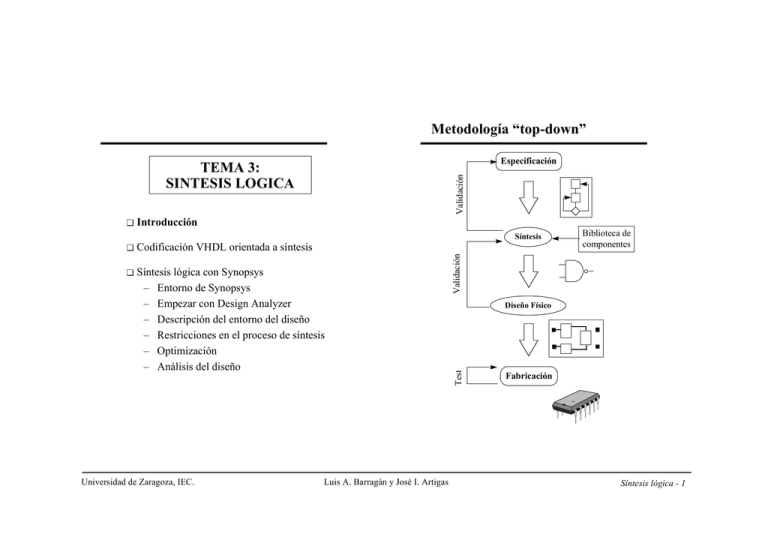

Metodología “top-down”

Especificación

❏

Validación

TEMA 3:

SINTESIS LOGICA

Introducción

Codificación VHDL orientada a síntesis

❏

Síntesis lógica con Synopsys

– Entorno de Synopsys

– Empezar con Design Analyzer

– Descripción del entorno del diseño

– Restricciones en el proceso de síntesis

– Optimización

– Análisis del diseño

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Diseño Físico

Test

❏

Biblioteca de

componentes

Validación

Síntesis

Fabricación

Síntesis lógica - 1

Síntesis

❏

Introducción

Síntesis: conversión de una descripción

comportamental en una estructural, en la

que cada bloque es un componente de la

biblioteca elegida

Tareas de síntesis

❏

Descripción VHDL de un sistema.

Requisitos:

– Capturar la funcionalidad

– Cumplir especificaciones de diseño

– Ser SINTETIZABLE

❏

SINTESIS: proceso de transformar una

descripción VHDL comportamental/RTL

en un netlist de puertas y biestables de una

tecnología dada

❏

La descripción funcional VHDL es

independiente de la tecnología.

Sin embargo:

Síntesis de la

arquitectura

EL CIRCUITO SINTETIZADO

DEPENDE FUERTEMENTE

DEL ESTILO DE CODIFICACION

Síntesis

Lógica

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 2

Introducción

❏

Introducción

entity combi is

port(A,B,C: in std_logic;

D: out std_logic);

end combi;

architecture behavioral of combi is

begin

D <= (A and B) or C;

end behavioral

Síntesis:

– Estilo de diseño => Celdas estándar

– Herramienta de síntesis => Synopsys

– Librería de celdas => ES2

HDL

Comportamental

/RTL

Librería

de Celdas

A

B

C

Objetivos

de Diseño

HERRAMIENTA

DE SÍNTESIS

A

B

C

Netlist de puertas

optimizado e

independiente de

la tecnología

D

Netlist para una tecnología:

- CMOS, nº metales, 1µ

- Fabricante

D

Netlist

A

B

C

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

D

Buffers adicionales para

satisfacer necesidades de

corriente

Síntesis lógica - 3

Codificación VHDL orientada

a síntesis

❏

TEMA 3:

SINTESIS LOGICA

• Recordar que VHDL es principalmente un

lenguaje de descripción de hardware.

❏

Introducción

❏

Codificación VHDL orientada a síntesis

❏

Síntesis lógica con Synopsys

– Entorno de Synopsys

– Empezar con Design Analyzer

– Descripción del entorno del diseño

– Restricciones en el proceso de síntesis

– Optimización

– Análisis del diseño

Universidad de Zaragoza, IEC.

La síntesis lógica es muy dependiente del

estilo de código utilizado.

– Pensar en téminos de circuito.

– Estilo recomendado:

• Sentencias de asignación de señal

concurrentes.

• Procesos simples.

• Uso de componentes para el particionado.

❏

Luis A. Barragán y José I. Artigas

Vamos a considerar los siguientes temas:

– Tipos VHDL.

– Señales frente a variables.

– Estructuras condicionales.

– Operadores aritméticos.

– Compartir recursos.

– Particionado del sistema.

Síntesis lógica - 4

Tipos VHDL (1)

❏

Tipos VHDL (2)

Tipos soportados para síntesis:

❏

El package std_logic_1164 de la librería

IEEE contiene:

– Los tipos std_logic y std_logic_vector

– Funciones lógicas y de conversión de

tipos.

❏

Es recomendable usar el tipo Std_logic

– Sus 9 valores son muy apropiados

para describir el comportamiento del

hardware.

– En simulación se inicializa a 'U', lo

que ayuda a no olvidar el RESET.

STD_LOGIC

Tiene 9 valores:

'U' → Sin inicializar; no tiene significado en síntesis.

'X' → Desconocido (fuerte); conflicto, ¡¡ERROR!!.

'0' → Cero (fuerte); equivalente a Vss.

'1' → Uno (fuerte); equivalente a Vcc o Vdd.

'Z' → Alta impedancia; se infiere un triestado.

'W' → Desconocido (débil).

'L' → Cero (débil); resistencias pull-down.

'H' → Uno (débil); resistencias pull-up.

'-' → Don't care; Se sintetiza en 0 ó 1.

Permite vectores:

std_logic_vector (7 downto 0)

std_logic_vector ( 0 to 7)

¡Ojo!, no inicializar las señales cuando se declaran:

INTEGER

signal out1: std_logic:= '0'; --mala idea

Si no se acota el rango, se sintetizan 32 bits.

integer range 0 to 7 → Se sintetizan 3 bits.

La herramienta de síntesis ignora las inicializaciones,

puesto que no tienen sentido circuital.

TIPOS ENUMERADOS

– En particular, usar Std_logic para la

declaración de todos los puertos de

entidades.

Por defecto se codifican en representación binaria

type STATE_TYPE is (S0, S1, S2, S3, S4);

S0 → "000", S1 → "001", ..., S4 → "100", 3 bits.

En la codificación de MEF, incorporar mecanismos

para salir de estados no deseados, por ejemplo "101".

Ö

Universidad de Zaragoza, IEC.

• Evita la necesidad de funciones de

conversión en la jerarquía.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 5

Tipos VHDL (3)

❏

Minimizar el uso de puertos declarados

como BUFFER.

– El modo buffer se usa cuando se desea

leer internamente una señal de salida.

– El inconveniente es que el modo

buffer se propaga por la jerarquía.

– Solución: declarar el puerto como

OUT y añadir una señal interna.

entity BUF is

port (A:

In std_logic;

CLK: In std_logic;

B:

Out std_logic);

end BUF;

Señales frente a variables (1)

❏

Las variables se actualizan en el instante

– se simulan más rápido, pero

– pueden enmascarar aleas.

❏

Las señales esperan un delta de tiempo

antes de tomar un nuevo valor

– simulación más lenta, pero

– su comportamiento se acerca más al

hardware que las variables.

❏

Es recomendable usar señales para la

descripción de hardware. Las variables se

pueden sintetizar de forma ineficiente.

– Ejemplo pág. siguiente: circuito

modelado con variables y con señales.

architecture BEHAVIORAL of BUF is

signal B_tmp: std_logic; -- señal interna

begin

B <= B_tmp; -- asignación concurrente

-- En el código, ya sólo se usa la señal

-- interna b_tmp.

process begin

wait until CLK = '1';

B_tmp <= A and B_tmp;

end process;

end BEHAVIORAL;

Universidad de Zaragoza, IEC.

• VHDL Compiler genera un registro para

todas las señales y algunas variables

asignadas en un proceso con wait o 'event.

– El modelo con variables es ineficiente

para síntesis pues utiliza un registro

adicional.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 6

Señales frente a variables (2)

Estructuras condicionales (1)

VARIABLE_ARCH: process

variable SUM: std_logic;

begin

wait until CLK = '1';

if RST = '0' then

SUM := '0';

else SUM := SUM + '1';

end if;

O1 <= SUM;

end process;

'0'

D Q

'1'

La estructura de la lógica sintetizada

se infiere directamente de la estructura

del código VHDL de partida.

Sentencia if, else

– Genera lógica más estructurada =>

– suele ocupar menos área

❏

Sentencia case

– Genera lógica más paralela =>

– suele ser más rápida

❏

Recomendaciones:

– Usar case para decodificaciones

complejas.

– Usar if para caminos críticos.

0

O1

D Q

+

❏

1

RST

SIGNAL_ARCH: process begin

wait until CLK = '1';

if RST = '0' then

SUM <= '0';

else SUM <= SUM + '1';

end if;

end process;

O1

O1 <= SUM;

'0'

D Q

'1'

+

• Genera lógica en que cada condición tiene

mayor prioridad que la siguiente. Pasar el

camino crítico por la primera condición.

• En cualquier caso, no usar sentencias if

muy anidadas.

0

1

RST

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 7

Estructuras condicionales (2)

❏

Operadores aritméticos (1)

Ejemplo de estilo de codificación y

eficiencia del hardware sintetizado.

process (SEL,A,B,C,D)

begin

if SEL = "00" then

DO <= A;

elsif SEL = "01" then

DO <= B;

elsif SEL = "10" then

DO <= C;

else

process (SEL,A,B,C,D)

DO <= D;

begin

end if;

case SEL is

end process;

when "00" => DO <=

when "01" => DO <=

when "10" => DO <=

when "11" => DO <=

D

0

end case;

end process;

C

1

❏

El package std_logic_1164 no incluye

funciones aritméticas y de comparación

❏

Para realizar estas funciones, es necesario

incluir el package std_logic_arith.

– Contiene funciones de conversión

para pasar de std_logic_vector a

signed o unsigned:

• Codificación binaria sin signo

UNSIGNED("1011") -- representa 11

A;

B;

C;

D;

0

B

1

0

DO

A

SEL[0]

SEL[1]

1

A

0

B

1

0

SEL[0]

DO

1

C

0

D

1

• Codificación en complemento a 2

SIGNED("1011") -- representa -5

– Suministra funciones aritméticas, de

comparación y conversión para los

tipos signed, unsigned e integer.

– Además se puede incluir el package

• std_logic_unsigned: por defecto interpreta

los std_logic_vector como sin signo.

• std_logic_signed: por defecto interpreta

los std_logic_vector como complem. a 2.

SEL[1]

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 8

Operadores aritméticos (2)

❏

Dos posibilidades de codificación:

library IEEE

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

entity ARITH is

Port ( A: In std_logic_vector (0 to 15);

B: In std_logic_vector (0 to 15);

O: Out std_logic_vector (0 to 15));

end ARITH;

architecture BEHAVIORAL of ARITH is

begin

O <= UNSIGNED (A) + UNSIGNED (B);

end BEHAVIORAL;

Compartir recursos

❏

Un recurso es un circuito presintetizado

que se puede seleccionar para implementar

un operador VHDL "complejo", como

*

La síntesis puede

+,compartir los operadores

de la misma línea

> , < , >= , <=

❏

Los recursos se pueden compartir sólo si

están en el mismo proceso y en distintas

ramas de sentencias if o case.

if CTL = '0' then

Z <= A + B;

else

Z <= C + D;

end if;

library IEEE

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity ARITH is

Port ( A: In std_logic_vector (0 to 15);

B: In std_logic_vector (0 to 15);

O: Out std_logic_vector (0 to 15));

end ARITH;

architecture BEHAVIORAL of ARITH is

begin

O <= A + B;

end BEHAVIORAL;

A

B

0

A

0

C

1

B

0

D

1

+

Z

C

D

CTL

Universidad de Zaragoza, IEC.

+

Luis A. Barragán y José I. Artigas

1

+

Z

CTL

Síntesis lógica - 9

Particionado del sistema

❏

El particionado debe tener en cuenta

– La funcionalidad y la estructura del

diseño.

– El proceso de síntesis lógica posterior.

La estructura de la lógica sintetizada

se infiere directamente de la estructura

del código VHDL de partida.

❏

❏

Un particionado adecuado consigue

– Alcanzar los mejores resultados de

la síntesis lógica.

– Acelerar el proceso de síntesis.

– Simplificar las restricciones de

optimización.

Particionado del sistema:

resultados de la síntesis lógica

❏

• recomendable modificar la jerarquía para

que esté contenido en un único bloque.

❏

Describir los recursos que se pueden

compartir en el mismo bloque.

– Es la única forma para que DC los

pueda compartir.

❏

Separar en bloques distintos las partes a

optimizar con diferentes objetivos o

estrategias.

– Area frente a velocidad.

– Lógica aleatoria frente a estructurada.

– ...

Aunque el particionado se define en SGE

al principio del diseño, se puede modificar

en DC mediante las órdenes group y

ungroup.

Universidad de Zaragoza, IEC.

Describir toda la lógica combinacional

relacionada en un sólo bloque.

– DC no puede optimizar entre bloques.

– En particular, para el camino crítico

Luis A. Barragán y José I. Artigas

Síntesis lógica - 10

Particionado del sistema:

acelerar el proceso de síntesis

❏

Eliminar lógica entre bloques.

– El diseño sólo debe contener puertas

en los últimos bloques de la jerarquía.

NO

Particionado del sistema:

simplificar las restricciones

❏

Registrar todas las salidas.

❏

Utilizar un único reloj en cada bloque.

❏

Separar los FF que se disparan con

distintos flancos.

– Test Compiler genera las cadenas de

registros para los de un tipo de flanco.

• De los otros se olvida.

❏

❏

Aislar las máquinas de estados

– si se desean optimizar con su

compilador específico.

Número de puertas.

– Limitar entre 250 y 5000 puertas los

últimos bloques de la jerarquía.

• Depende de la CPU y de la memoria

disponible en la máquina.

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 11

ENTORNO DE SYNOPSYS:

Flujo de diseño

TEMA 3:

SINTESIS LOGICA

VHDL Comportamental

Síntesis Lógica

Descripción Booleana

❏

Introducción

❏

Codificación VHDL orientada a síntesis

❏

Síntesis lógica con Synopsys

– Entorno de Synopsys

– Empezar con Design Analyzer

– Descripción del entorno del diseño

– Restricciones en el proceso de síntesis

– Optimización

– Análisis del diseño

Librería

de

Celdas

Descripción Booleana

Optimizada

Mapeado Tecnológico

Objetivos

de

Diseño

Area,

velocidad

NO

Netlist

Vectores

de test

Cobertura de Fallos

Simulación lógica

NO

NO

DISEÑO FISICO

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 12

Entorno de Synopsys:

Herramientas de síntesis

Entorno de Synopsys:

Interfaz con Design Compiler

❏

Design Analyzer

SGE

Captura del diseño

VHDL Compiler

Síntesis

Design Compiler Family

Optimización del circuito

FPGA

Compiler

Design

Compiler

(CMOS)

Test Compiler

VHDL

Synthetic

Library Compiler

Esquemas

Tablas de estados

Objetivos

Interfaz gráfico con menús

Design Analyzer

Librería

tecnológica

Design

Compiler

dc_shell

Library

Compiler

Vectores

de test

Universidad de Zaragoza, IEC.

Modos de interaccionar con DC:

– design_analyzer invoca el

interfaz gráfico de Synopsys.

– dc_shell invoca el interfaz de línea

de comandos.

Línea de comandos

Luis A. Barragán y José I. Artigas

Síntesis lógica - 13

EMPEZAR CON DESIGN

ANALYZER

❏

Configuración inicial

❏

Librerías tecnológicas

❏

Generadores de macroceldas

❏

Iniciar un diseño

– analyze y elaborate

– read

Configuración inicial

❏

Cuando DC arranca, lee el archivo

.synopsys_dc.setup

– Se pueden leer hasta tres archivos:

• .synopsys_dc.setup del sistema.

• .synopsys_dc.setup del directorio home.

• .synopsys_dc.setup del direct. de trabajo.

– Se leen en el orden listado y prevalece

el último leído.

❏

Permite personalizar el entorno de trabajo.

❏

Contiene información sobre:

– Lista de directorios en los que DC

debe buscar los archivos

• search_path = {. /usr/my_dir/design}

– Librerías tecnológicas a utilizar:

• target_library = "___.db"

• symbol_library = "___.sdb"

• link_library = { }

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Síntesis lógica - 14

Librerías tecnológicas (1)

❏

Librerías tecnológicas (2):

Ejemplo hoja características

Contiene las celdas prediseñadas que serán

utilizadas en el proceso de síntesis lógica.

NA2

2-input NAND

Truth Table

❏

❏

ECPD07

StdLib

DC utiliza las librerías tecnológicas

asignadas a las variables:

– target_library

– link_library

Datasheet Version: 2.0

A

B

Y

0

X

1

X

0

1

1

1

0

Symbol

Y = A AND B

A

Y

B

Ejemplo para CELDAS ESTANDAR

– Proceso: ECPD10 (1.0 micra)

– Lista de Componentes:

Code

Parameter

Value

X

Length

10.000

Y

Height

38.000

Ntran

Transistor count

4

Power

AC Power dissipation

2.21

Unit

NA2

um

um

trans

uW/MHz

Input/Output Specifications

Input

Description

A

Data in

0.048

pF

B

Data in

Fanin

0.050

Unit

pF

Output

Description

Y

Data out

Fanout

0.82

Unit

pF

• StandardLib

• PadLib2

– Información de cada celda:

•

•

•

•

Propagation Delays

Función Lógica

Entradas/Salidas

Parámetros temporales

Area

Code

From

To

Min

Typ

tplh

A

Y

0.07

0.14

0.27

0.32

ns

tphl

A

Y

0.04

0.09

0.18

0.21

ns

tplh

B

Y

0.05

0.11

0.21

0.25

tphl

B

Y

0.07

0.14

0.28

0.32

ns

dtplh

ANY

Y

0.55

1.18

2.33

2.71

ns/pF

dtphl

ANY

Y

0.46

0.97

1.93

2.24

ns/pF

Page 2-42

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Max

Mil

Unit

ns

E02A03

Síntesis lógica - 15