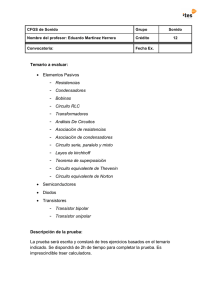

Test basado en sensores de corriente internos para circuitos

Anuncio