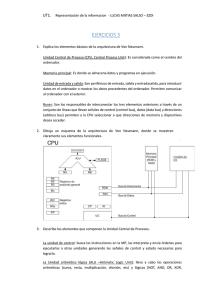

Estructura y Tecnología de Computadores

Anuncio