semana2 - sistemasdigitales2

Anuncio

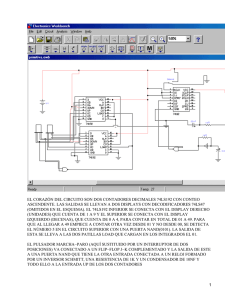

1.2.1 CELDA BÁSICA RS CON NAND SON RELOJ EL LATCH R-S (RESET-SET) CON ENTRADA ACTIVA A NIVEL BAJO ES UN TIPO DE DISPOSITIVO LÓGICO BIESTABLE COMPUESTO DE DOS PUERTAS NAND ACOPLADAS TAL Y COMO MUESTRA LA FIGURA. AL COMPARAR EL FUNCIONAMIENTO DE UNA PUERTA NAND CON OTRA NOR PODEMOS VER QUE SI BIEN UNA PUERTA NOR SE ASEMEJA A UN INVERSOR CUANDO UNA DE SUS ENTRADAS ESTÁ CONECTADA A ‘0’, LA PUERTA NAND SE ASEMEJA A UN INVERSOR CUANDO UNA DE SUS ENTRADAS ESTÁ CONECTADA A ‘1’ (VER TABLA DE VERDAD DE UNA PUERTA NAND EN LA FIGURA). POR TANTO EL MODO DE MEMORIA DEL LATCH (QN=QN-1) CORRESPONDE EN ESTE CASO CON LAS DOS ENTRADAS A ‘1’. SI LA ENTRADA S SE LLEVA A NIVEL BAJO ‘0’ LA SALIDA Q SE PONE A ‘1’ (SET) Y SI LA ENTRADA R SE LLEVA A NIVEL BAJO ‘0’ LA SALIDA Q SERÁ ‘0’ (RESET). DE AHÍ QUE A ESTE LATCH SE LE DÉ EL NOMBRE DE LATCH CON ENTRADA ACTIVA A NIVEL BAJO. EN LA FIGURA PODEMOS APRECIAR LA TABLA DE VERDAD CORRESPONDIENTE A ESTE LACTH Y EN LA FIGURA SIGUIENTE SU SÍMBOLO LÓGICO. [ 6 ] REGISTRO BÁSICO CONSTRUIDO CON COMPUERTAS NAND ESTE ES EL CIRCUITO MÁS SENCILLO Y BÁSICO DE UN FF, PUEDE SER CONSTRUIDO A PARTIR DE DOS COMPUERTAS NAND O DOS COMPUERTAS NOR CON DOS ENTRADAS, A CONTINUACIÓN SE ILUSTRA CON COMPUERTAS NAND, Y ES DENOMINADO "REGISTRO BÁSICO NAND". LA FORMA DE CONECTARLAS ES LA SIGUIENTE: SE DEJA LIBRE UNA DE LAS ENTRADAS DE CADA COMPUERTA, LAS SOBRANTES SON CONECTADAS INDEPENDIENTEMENTE DE MANERA CRUZADA HACIA LA SALIDA DE LA COMPUERTA CONTRARIA. QUEDANDO LA CONEXIÓN DE LA SIGUIENTE MANERA: LA SIGUIENTE TABLA MUESTRA EL ESTADO INICIAL DEL REGISTRO BÁSICO NAND, CUANDO SUS ENTRADAS SE ENCUENTRAN EN ALTO (ESTADO DE REPOSO DEL FF). PARA COMENZAR LA ACCIÓN DE "FLIP FLOP" SERÁ NECESARIO ENVIAR A BAJO ALGUNA DE LAS ENTRADAS, CON SU CORRESPONDIENTE CAMBIO DE ESTADO A LA SALIDA. LA SIGUIENTE TABLA NOS MUESTRA LOS DIFERENTES CAMBIOS DE LAS SALIDAS, SEGÚN CADA SELECCIÓN DE ENTRADAS (LA "X" SIGNIFICA QUE NO IMPORTA EL ESTADO EN EL QUE SE ENCUENTREN EN ESE MOMENTO): SIGUIENDO LOS DATOS DE LA TABLA PODEMOS RESUMIR QUE: SI SET Y RESET ESTÁN EN ALTO, EL FF MANTIENE SUS SALIDAS EN EL ESTADO ACTUAL. SI RESET RECIBE UN PULSO BAJO, LAS SALIDAS SON FORZADAS A Q = 0 Y /Q = 1 SI SET RECIBE UN PULSO BAJO, LAS SALIDAS SON FORZADAS A Q = 1 Y /Q = 0 SI LAS DOS ENTRADAS RECIBEN PULSOS BAJOS, LAS SALIDAS SON FORZADAS A Q = 1 Y /Q = 1 ESTE ÚLTIMO CAMBIO NORMALMENTE SE CONSIDERA COMO NO DESEADO, YA QUE EL PRINCIPIO BÁSICO ES QUE LAS SALIDAS SIEMPRE ESTÉN ESPECIALES, INVERTIDAS NOSOTROS (AUNQUE PODRÍAMOS EN CIERTOS UTILIZAR ESTE CASOS EFECTO). ENTONCES, LA TABLA DE VERDAD DEL REGISTRO BÁSICO NAND ES LA SIGUIENTE: [ 7 ] AQUÍ SE PRESENTÓ OTRA FORMA DE ABORDAR EL TEMA DEL FLIP – FLOP RS NAND; DE NUEVO, ES EL ALUMNO QUIEN DECIDE QUÉ MÉTODO LE PERMITIRÁ CONSTRUIR EL MEJOR ANÁLISIS PARA EL RS NAND. 1.2.2 CELDA BÁSICA RS CON NOR SIN RELOJ VAMOS A ANALIZAR UNA SITUACIÓN EN EL LATCH RS CON PUERTAS NOR ( P.E. ) PARA ENTENDER LA TABLA DE VERDAD ANTERIOR: CONSIDERAMOS LA SITUACIÓN DE PARTIDA (ESTADO PRESENTE ) Y VAMOS A INTRODUCIR R=S=0 ( LA SITUACIÓN DE PARTIDA ESTÁ EN AZUL ). COMO SE PUEDE OBSERVAR SE MANTIENE EL ESTADO 0 COMO CABÍA ESPERAR, LUEGO SE ENCUENTRA EN ESTADO DE MEMORIA. , CONSIDERAMOS AHORA LA SITUACIÓN DE PARTIDA (ESTADO PRESENTE ) Y VAMOS A INTRODUCIR R=0 Y S=1( LA SITUACIÓN DE PARTIDA ESTÁ EN AZUL ). COMO SE PUEDE OBSERVAR EL ESTADO FUTURO CAMBIA A 1 COMO CABÍA ESPERAR SEGÚN LA TABLA, , UNA VEZ QUE SE ESTABILIZA LA REALIMENTACIÓN DE LAS SALIDAS. LA ? QUE APARECE EN LA TABLA DE VERDAD CORRESPONDE A UNA SITUACIÓN NO PERMITIDA EN LA QUE SE GENERA UN CONFLICTO DE INDETERMINACIÓN QUE SE SOLUCIONARÁ CON EL BIESTABLE JK HACIENDO QUE CUANDO LAS ENTRADAS ESTÁN EN ALTA EL CIRCUITO CAMBIE DE ESTADO. SI ANALIZO LA SOLUCIÓN DEL LATCH RS CON PUERTAS NAND LLEGARÉ A LA CONCLUSIÓN QUE SE DIFERENCIA DEL ANTERIORMENTE ANALIZADO PORQUE ES ACTIVO SUS ENTRADAS A NIVEL BAJO (CEROS LÓGICOS ). [ 8 ] EL LATCH R-S (RESET-SET) CON ENTRADA ACTIVA A NIVEL ALTO ES UN TIPO DE DISPOSITIVO LÓGICO BIESTABLE CON DOS SALIDAS Q Q (UNA LA COMPLEMENTARIA DE LA OTRA), COMPUESTO DE DOS PUERTAS NOR ACOPLADAS TAL Y COMO MUESTRA LA FIGURA. SE PUEDE OBSERVAR QUE LA SALIDA DE CADA PUERTA NOR SE CONECTA A LA ENTRADA DE LA PUERTA OPUESTA. EL FUNCIONAMIENTO DEL LATCH R-S CON ENTRADA ACTIVA A NIVEL ALTO SE DERIVA DEL COMPORTAMIENTO DE LA PUERTA NOR (VER TABLA DE VERDAD DE LA FIGURA ANTERIOR. SI UNA DE LAS ENTRADAS DE UNA PUERTA NOR (DE DOS ENTRADAS) SE MANTIENE A ‘0’ LA SALIDA SERÁ LA INVERSA DE LA OTRA ENTRADA. EN CONSECUENCIA SI EN EL LATCH R Y S SON ‘0’, LA SALIDA DEL CIRCUITO SE MANTENDRÁ EN EL ESTADO EN EL ESTUVIERA (VER TABLA DE VERDAD DEL LATCH EN LA FIGURA ANTERIOR. SI LA ENTRADA R DEL LATCH SE PONE A ‘1’ MIENTRAS QUE LA ENTRADA S PERMANECE A ‘0’, LA SALIDA Q SE PONDRÁ A ‘0’ SIN IMPORTAR SU ESTADO PREVIO (EN UNA PUERTA NOR EN CUANTO HAY UNA ENTRADA A ‘1’ LA SALIDA ES ‘0‘) Y A SU VEZ LA SALIDA NEGADA, Q SE PONDRÁ A ‘1‘, EL LATCH PASARÁ AL ESTADO DE RESET. SI AHORA R VUELVE A ‘0’ EL CIRCUITO ENTRARÁ DE NUEVO EN SU MODO DE MEMORIA. DE MANERA SIMILAR SI S SE LLEVA A ‘1’ MIENTRAS R PERMANECE A ‘0’, ENTONCES LA SALIDA NEGADA Q SE PONDRÁ A ‘0’, CON LO QUE LA SALIDA Q SE COLOCARÁ A ‘1’. EN RESUMEN EL FUNCIONAMIENTO DEL LATCH ES EL SIGUIENTE: • LA ENTRADA R ACTIVA (‘1’) REALIZA UN RESET DEL LATCH (PONE LA SALIDA A ‘0’). • LA ENTRADA S ACTIVA (‘1’) REALIZA UN SET DEL LATCH (PONE LA SALIDA A ‘1’ ). • SI LAS ENTRADAS ESTÁN DESACTIVADAS (R=0 Y S=0) LA SALIDA DEL LATCH NO CAMBIA (QN=QN-1). • SI SE ACTIVAN LAS DOS ENTRADAS (R=1 Y S=1) EL CIRCUITO NO FUNCIONA CORRECTAMENTE (Q=0 Y Q =0). EL SÍMBOLO LÓGICO DEL LATCH R-S CON ENTRADA ACTIVA SE MUESTRA EN LA FIGURA SIGUIENTE: [ 6 ] DE NUEVO, AQUÍ SE PRESENTÓ OTRA FORMA DE ABORDAR EL TEMA DEL FLIP – FLOP RS NOR; UNA VEZ MÁS, ES EL ALUMNO QUIEN DECIDE QUÉ MÉTODO DE ANÁLISIS LE PERMITIRÁ ENTENDER MEJOR EL RS NOR. 1.2.3 CELDA BASICA JK SIN RELOJ BIESTABLE JK ES VERSÁTIL Y ES UNO DE LOS TIPOS DE FLIP-FLOP MAS USADOS. SU FUNCIONAMIENTO ES IDÉNTICO AL DEL FLIP-FLOP S-R EN LAS CONDICIONES SET, RESET Y DE PERMANENCIA DE ESTADO. LA DIFERENCIA ESTÁ EN QUE EL FLIP-FLOP J-K NO TIENE CONDICIONES NO VALIDAS COMO OCURRE EN EL S-R. ESTE DISPOSITIVO DE ALMACENAMIENTO ES TEMPORAL QUE SE ENCUENTRA DOS ESTADOS (ALTO Y BAJO), CUYAS ENTRADAS PRINCIPALES, J Y K, A LAS QUE DEBE EL NOMBRE, PERMITEN AL SER ACTIVADAS: J: EL GRABADO (SET EN INGLÉS), PUESTA A 1 Ó NIVEL ALTO DE LA SALIDA. K: EL BORRADO (RESET EN INGLÉS), PUESTA A 0 Ó NIVEL BAJO DE LA SALIDA. SI NO SE ACTIVA NINGUNA DE LAS ENTRADAS, EL BIESTABLE PERMANECE EN EL ESTADO QUE POSEÍA TRAS LA ÚLTIMA OPERACIÓN DE BORRADO O GRABADO. A DIFERENCIA DEL BIESTABLE RS, EN EL CASO DE ACTIVARSE AMBAS ENTRADAS A LA VEZ, LA SALIDA ADQUIRIRÁ EL ESTADO CONTRARIO AL QUE TENÍA. LA ECUACIÓN CARACTERÍSTICA DEL BIESTABLE JK QUE DESCRIBE SU COMPORTAMIENTO ES: Y SU TABLA DE VERDAD ES: J K Q 0 0 Q 0 1 0 1 0 1 1 1 EL BIESTABLE SE DENOMINA ASÍ POR JACK KILBY, EL INVENTOR DE LOS CIRCUITOS INTEGRADOS EN 1958, POR LO CUAL SE LE CONCEDIÓ EL PREMIO NOBEL EN FÍSICA DE 2000. [ 9 ] FLIP FLOP TIPO "J-K" ESTE FF ES UNO DE LOS MÁS USADOS EN LOS CIRCUITOS DIGITALES, Y DE HECHO ES PARTE FUNDAMENTAL DE MUCHOS CIRCUITOS AVANZADOS COMO CONTADORES Y REGISTROS DE CORRIMIENTO, QUE YA VIENEN INTEGRADOS EN UN CHIP. ESTE FF CUENTA CON DOS ENTRADAS DE DATOS J Y K, SU FUNCIÓN ES EN PRINCIPIO LA MISMA QUE EL REGISTRO BÁSICO NAND O NOR, PERO CON LA DIFERENCIA QUE LA CONDICIÓN EN LAS ENTRADAS J = 1, K = 1, A DIFERENCIA DEL REGISTRO NAND, QUE GENERARÍA UNA SALIDA ERRÓNEA O NO DESEADA, EN UN FF J-K, OBLIGA A LAS SALIDAS A CONMUTAR SU ESTADO AL OPUESTO (TOGGLE) A CADA PULSO DEL RELOJ. ESTO LO CONVIERTE EN UN TIPO DE FF MUY VERSÁTIL. TABLA DE VERDAD DE UN FF TIPO J-K SÍNCRONO. OBSERVANDO LA TABLA DE VERDAD OBSERVAMOS LOS CAMBIOS QUE PROVOCA EN SUS SALIDAS ESTE FF: SI J Y K = 0, NO HAY CAMBIOS EN LAS SALIDAS. SI J = 1, Y K = 0, SE FORZAN LAS SALIDAS A Q = 1, /Q = 0 SI J = 0, Y K = 1, SE FORZAN LAS SALIDAS A Q = 0, /Q = 1 SI J = 1, Y K = 1, LAS SALIDAS CONMUTAN SU ESTADO HACIA EL SIGUIENTE A CADA PULSO DEL RELOJ (TOGGLE) [ 9 ] HASTA QUÍ SE HAN REVISADO LOS FLIP – FLOP RS, NAND Y NOR, ADEMÁS DEL FLIP – FLOP JK; LA TEORÍA DE LOS SECUENCIALES NO CAMBIA, SÓLO LO HACE EL ESTILO DEL INVESTIGADOR. UNA VEZ MÁS, EL ECHO DE CITAR VARIAS FUENTES, ES CON EL FIN DE QUE EL CONCEPTO/DEFINICIÓN DE LOS TEMAS SE COMPLEMENTEN, O BIEN, QUE OTRA FUENTE DE EXPLICACIÓN MEJORE LA COMPRENSIÓN DEL TEMA. REFERENCIAS [1] RINCON, LUIS; MARTINEZ, JOSE; SERRANO, ANGEL (2008). . Introducción a los circuitos secuenciales En /docencia/ETCITIG_LADE/teoria-cuat1 [En línea] Recuperado el 20 de noviembre del 2011, de http://dac.escet.urjc.es/docencia/ETC-ITIG_LADE/teoriacuat1/tema7_circuitos_secuenciales.pdf [2] NAVA, OSCAR (2011). Arquitectura de Computadoras. Recuperado el 20 de noviembre del 2011 del sitio web de la Universidad Autónoma Metropolitana: http://ce.azc.uam.mx/profesores/oalvarado/ac/ac_08b_ctosSecuenciales_Imp.pdf [3] RENGEL, RAUL; MARTIN, MARIA. CIRCUITOS SECUENCIALES. Recuperado el 20 de noviembre del 2011 del sitio web de la Universidad de Salamanca: http://ocw.usal.es/ensenanzastecnicas/electronica/contenido/electronica/Tema10_SistemSecuencial.pdf [4] Circuitos Secuenciales. Recuperado el 20 de noviembre del 2011 del sitio web de la Universidad Nacional Experimental de los Llanos Centrales Rómulo Gallegos: http://www.unerg.edu.ve/index.php?option=com_docman&task=doc_view&gid=271 [5] Circuitos Secuenciales. [En línea]Recuperado el 20 de noviembre del 2011, de: http://www.ecured.cu/index.php/Circuitos_Secuenciales [6] ALVAREZ, JUAN (2011). LOGICA SECUENCIAL REGISTROS DE DESPLAZAMIENTO Y CONTADORES. Recuperado el 20 de noviembre del 2011 del sitio web de la Universidad de Valladolid: http://www.infor.uva.es/~jjalvarez/asignaturas/fundamentos/lectures/digital/Tema3_sec uenciales.pdf [7] El Mundo Digital III: Los Flip Flops (2011). [En línea] Recuperado el 20 de noviembre del 2011, de: http://www.forosdeelectronica.com/tutoriales/flip-flops.htm [8] BIESTABLES (2011). [En línea] Recuperado el 20 de noviembre del 2011, de: http://www.profesormolina.com.ar/electronica/componentes/int/biest.htm [9] STROGATZ, STEVEN (2001). Nonlinear Dynamics and Chaos. En /wiki/Biestable [En línea] Recuperado de el 20 de noviembre del 2011, de: http://es.wikipedia.org/wiki/Biestable [10] Definición de Señal de reloj (clock signal) (2011). En /Dic/se%C3%B1al%20de%20reloj.php [En línea] Recuperado el 20 de noviembre del 2011, de: http://www.alegsa.com.ar/Dic/se%C3%B1al%20de%20reloj.php [11] Este artículo fue creado a partir de la traducción del artículo Taktsignal de la Wikipedia en alemán, concretamente de esta versión, bajo licencia Creative Commons Atribución Compartir Igual 3.0 y GFDL. En /wiki/Se%C3%B1al_de_reloj [En línea] Recuperado el 20 de noviembre del 2011, de: http://es.wikipedia.org/wiki/Se%C3%B1al_de_reloj [12] Circuito integrado 555 (2011). En /wiki/Circuito_integrado_555 [En línea] Recuperado el 20 de noviembre del 2011, de: http://es.wikipedia.org/wiki/Circuito_integrado_555 [13] Circuitos Digitales (2011). En /circuitos-digitales_1.html [En línea] Recuperado el 20 de noviembre del 2011, de: http://html.rincondelvago.com/circuitos-digitales_1.html [14] Flanco (electrónica) (2011). En /Flanco_(electr%C3%B3nica) [En línea[ Recuperado el 20 de noviembre del 2011, de: http://es.wikipedia.org/wiki/Flanco_(electr%C3%B3nica) [15] ROMERO, EDUARDO (201). 1.2.4 El concepto de señal de reloj. Recuperado el 20 de noviembre del 2011del sitio web del Instituto Tecnológico de Sonora: http://es.wikipedia.org/wiki/Flanco_(electr%C3%B3nica) [16] FLIP – FLOPS (2011). En /teoria/electronica-digital/193-flip-flop-flipflop-rs [En línea] Recuperado el 20 de noviembre del 2011, de: http://ladelec.com/teoria/electronica-digital/193-flip-flop-flip-flop-rs [17] El flip-flop SR (2011). En /~vruiz/docencia/laboratorio_estructura/practicas/html/node26.html [En línea] Recuperado el 20 de noviembre del 2011, de: http://www.hpca.ual.es/~vruiz/docencia/laboratorio_estructura/practicas/h tml/node26.html [18] Flip-Flop tipo D. Descripción. Símbolo (2011). En /dig_FF_D.asp [En línea] recuperado el 20 de noviembre del 2011, de: http://www.unicrom.com/dig_FF_D.asp [19] GONZALES, MARIBEL (2011). Circuitos digitales. En /trabajos14/flipflop/flipflop.shtml [En línea] Recuperado el 20 de noviembre del 2011, de: http://www.monografias.com/trabajos14/flipflop/flipflop.shtml