2do. Parcial

Anuncio

Segundo Parcial

Organización del Computador I

2 de Diciembre de 2003

Justifique detalladamente cada respuesta, incluyendo todas las cuentas y esquemas auxiliares.

Evite responder en lápiz. Resuelva cada ejercicio en hoja separada. Identifique todas las hojas.

Los números entre paréntesis al margen de cada ejercicio indican el valor de los mismos.

Se recomienda no invertir más de 32 p minutos en la resolución de un ejercicio de p puntos.

El parcial tiene 6 ejercicios, que permiten obtener un máximo de 100 puntos.

Se aprueba con un 60 % del puntaje máximo, y se promociona con un 80 % de dicho puntaje.

(04) 1. Para una arquitectura en la que el bus principal (o system bus) será accedido por dispositivos que operan

a muy diversas velocidades ¿Recomendarı́a Ud. un bus asincrónico o sincrónico?

Basándose tan sólo en las velocidades de los dispositivos que accederán al bus principal, la recomendación

primaria serı́a un bus asincrónico, ya que con un bus sincrónico se estarı́an imponiendo limitaciones de

velocidad innecesarias a los dispositivos más rápidos.

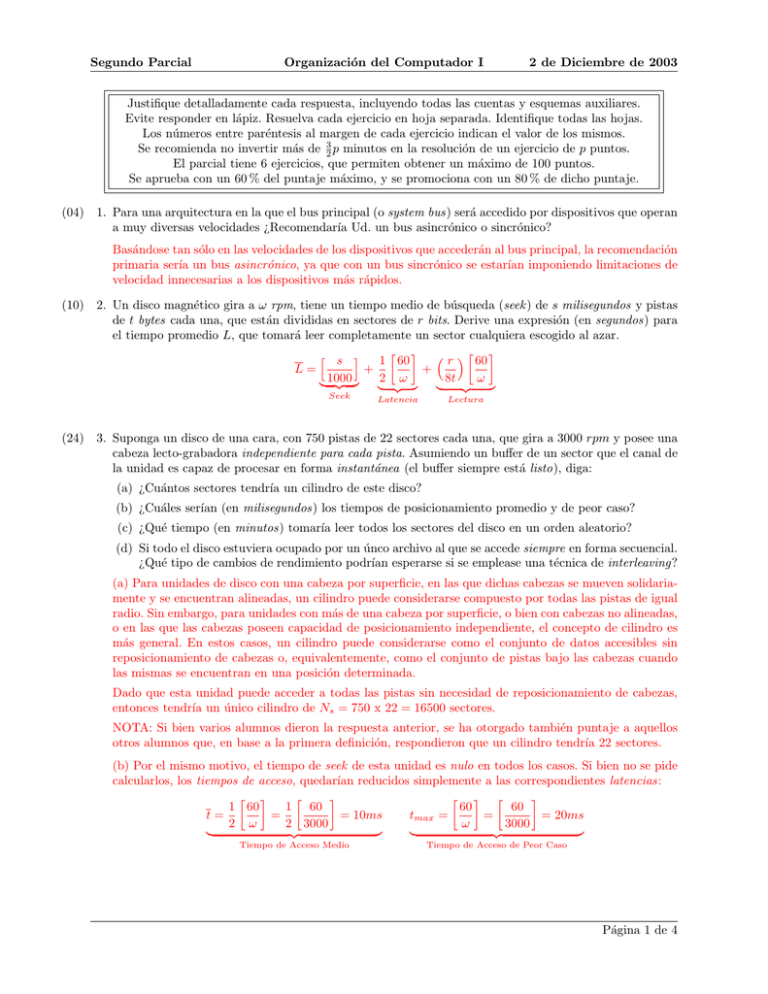

(10) 2. Un disco magnético gira a ω rpm, tiene un tiempo medio de búsqueda (seek ) de s milisegundos y pistas

de t bytes cada una, que están divididas en sectores de r bits. Derive una expresión (en segundos) para

el tiempo promedio L, que tomará leer completamente un sector cualquiera escogido al azar.

h s i

1 60

r

60

+

+

L=

| 1000

{z } |2 {zω } | 8t {z ω }

Seek

Latencia

Lectura

(24) 3. Suponga un disco de una cara, con 750 pistas de 22 sectores cada una, que gira a 3000 rpm y posee una

cabeza lecto-grabadora independiente para cada pista. Asumiendo un buffer de un sector que el canal de

la unidad es capaz de procesar en forma instantánea (el buffer siempre está listo), diga:

(a) ¿Cuántos sectores tendrı́a un cilindro de este disco?

(b) ¿Cuáles serı́an (en milisegundos) los tiempos de posicionamiento promedio y de peor caso?

(c) ¿Qué tiempo (en minutos) tomarı́a leer todos los sectores del disco en un orden aleatorio?

(d) Si todo el disco estuviera ocupado por un únco archivo al que se accede siempre en forma secuencial.

¿Qué tipo de cambios de rendimiento podrı́an esperarse si se emplease una técnica de interleaving?

(a) Para unidades de disco con una cabeza por superficie, en las que dichas cabezas se mueven solidariamente y se encuentran alineadas, un cilindro puede considerarse compuesto por todas las pistas de igual

radio. Sin embargo, para unidades con más de una cabeza por superficie, o bien con cabezas no alineadas,

o en las que las cabezas poseen capacidad de posicionamiento independiente, el concepto de cilindro es

más general. En estos casos, un cilindro puede considerarse como el conjunto de datos accesibles sin

reposicionamiento de cabezas o, equivalentemente, como el conjunto de pistas bajo las cabezas cuando

las mismas se encuentran en una posición determinada.

Dado que esta unidad puede acceder a todas las pistas sin necesidad de reposicionamiento de cabezas,

entonces tendrı́a un único cilindro de Ns = 750 x 22 = 16500 sectores.

NOTA: Si bien varios alumnos dieron la respuesta anterior, se ha otorgado también puntaje a aquellos

otros alumnos que, en base a la primera definición, respondieron que un cilindro tendrı́a 22 sectores.

(b) Por el mismo motivo, el tiempo de seek de esta unidad es nulo en todos los casos. Si bien no se pide

calcularlos, los tiempos de acceso, quedarı́an reducidos simplemente a las correspondientes latencias:

1 60

1 60

60

60

t=

=

= 10ms

tmax =

=

= 20ms

2 ω

2 3000

ω

3000

|

{z

}

|

{z

}

Tiempo de Acceso Medio

Tiempo de Acceso de Peor Caso

Página 1 de 4

Segundo Parcial

Organización del Computador I

2 de Diciembre de 2003

(c) Con la notación empleada en los puntos anteriores, el tiempo esperado promedio de lectura serı́a:

Ltot = Número de Sectores × (Tiempo de Acceso Medio + Tiempo de lectura) =

1 60

16500 60

165

= Ns t +

= 16500 × 0,01 +

= 165 +

= 180 segundos = 3 minutos

22 ω

22 3000

11

(d) Si el canal es capaz de descargar el buffer en forma instantánea, entonces no introduce ningún

factor de retardo que pueda compensarse dejando sectores fı́sicos libres entre dos sectores lógicamente

consecutivos. En consecuencia, el empleo de una técnica de interleaving producirı́a indefectiblemente una

degradación en el rendimiento de esta unidad.

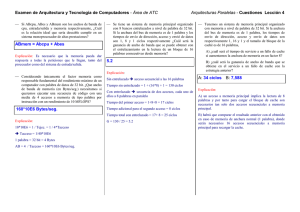

(26) 4. Una arquitectura emplea una memoria principal de 64 MB, direccionable a palabras de 32 bits, y una

cache de correspondencia directa de 4096 lı́neas, que trabaja con bloques de memoria de 16 palabras.

(a) ¿Cuántos bits tendrı́an los campos etiqueta (MSB de la dirección) e ı́ndice (LSB de la dirección)?

(b) ¿Cuál serı́a el tamaño total (en KB ) de la cache incluyendo sus etiquetas?

(c) Suponiendo que todas las instrucciones son de 32 bits y que la única actividad que tiene lugar en la

máquina es la ejecución del siguiente segmento de código (que está cargado a partir de la dirección

AD21A0h) ¿Cuál serı́a el porcentaje esperable de de aciertos durante la ejecución del mismo?

Ciclo:

MOV

MOV

MOV

JMP

REG1 ,

REG2 ,

[REG1],

Ciclo

8623

[REG1]

REG2

;Mueve al registro 1 la constente decimal 8623

;Donde [REG1] denota direccionamiento

; indirecto sobre el registro 1

;Repite el ciclo indefinidamente

(d) Idem (c), pero si la cache fuese de correspondencia totalmente asociativa?

(a) Si la memoria tiene 64 MB (226 bytes) direccionables a palabras de 32 bits (22 bytes), entonces tiene

26

un total de 222 = 224 direcciones que, en consecuencia, serán de 24 bits. Si los bloques tienen 16 = 24

palabras, entonces el campo ı́ndice de la cache requerirá 4 bits. Como la cache tiene 4096 = 212 lı́neas, el

campo lı́nea requerirá 12 bits, de forma que el campo etiqueta resultará de 24 − 4 − 12 = 8 bits. Sabiendo

que etiqueta se almacena en los M SB de la dirección, y el campo ı́ndice en los LSB, entonces la cache

interpretará una dirección de 24 bits como:

Campo etiqueta Campo lı́nea Campo ı́ndice

{z

}|

{z

}|

{z

}

|

8 bits

12 bits

4 bits

(b) Por cada una de sus 212 lı́neas la cache deberá almacenar 23 bits de etiqueta y un bloque de 24

palabras de 25 bits cada una. De este modo (y teniendo en cuenta que la cache emplea una polı́tica de

escritura inmediata) su tamaño total resultará:

212 23 + 24 25 bits = 215 1 + 26 bits = 212 × 65 bytes = 4 × 65 KB = 260KB

(c) Como la ejecución del segmento es la única actividad de la máquina, el estado de la cache dependerá exclusivamente de los accesos a memoria que requiera dicho segmento. Dado que el mismo se repite

indefinidamente, la tasa de aciertos se estabilizará después de varios ciclos resultando independiente del

contenido inicial de la cache. El procesador requerirá accesos a memoria durante i) Los ciclos de fetch

de cada instrucción, y ii) La ejecución de aquellas instrucciones que referencien la memoria. Como las

instrucciones son de una palabra, el segmento de código se cargará entre AD21A0h y AD21A3h, por

lo que una cache de correspondencia directa almacenarı́a el bloque de código en su lı́nea 21Ah. Dado

que la única dirección de memoria referenciada por el segmento es la 8632 decimal (0021AFh), la cache

emplearı́a la misma lı́nea (21Ah) para almacenar el bloque que contiene dicha posición. De este modo

(y teneiendo en cuenta que todas las escrituras pasan por la cache) los ciclos de fetch y ejecución competirán por la misma lı́nea de cache, resultando en:

Página 2 de 4

Segundo Parcial

Ciclo:

MOV

MOV

MOV

JMP

Organización del Computador I

REG1 ,

REG2 ,

[REG1],

Ciclo

8623

[REG1]

REG2

2 de Diciembre de 2003

;HIT o MISS que será irrelevante después de varos ciclos

;HIT en el fetch, MISS en el operando

;MISS en el fetch y MISS en el operando

;MISS en el fetch

Con lo que la tasa de aciertos será de 1/5 = 20 %.

(d) Después de algunos ciclos, una cache de correspondencia totalmente asociativa emplearı́a lı́neas

distintas para ambos bloques, los que quedarı́an referenciados por las etiquetas AD21Ah y 0021Ah

respectivamente. De este modo, resultarı́a una tasa de aciertos del 100 %.(NOTA: Esto continuarı́a siendo

válido aún en el caso particular de que la cache emplease un algoritmo de sustitución aleatorio ¿Por qué?).

(24) 5. Una unidad de cinta lee y graba a 60 ips y 1600 bpi. Después de cada bloque (registro fı́sico) la unidad

deja un gap de 53 de pulgada, a lo largo del que la velocidad efectiva de la cinta se reduce a la mitad.

En un carrete de 2400 pies útiles, se han grabado registros lógicos de 120 bytes c/u. Sabiendo que la

controladora agrega un header de 28 bytes y un trailer de 12 bytes a cada bloque que graba, diga:

(a) ¿Cuánto tiempo (en segundos) toma leer la cinta entera si en cada bloque hay 5 registros lógicos?

(b) ¿Cuánto tiempo (en segundos) toma leer la cinta entera si en cada bloque hay 77 registros lógicos?

(c) ¿Cuál es la velocidad de transferencia efectiva (en bytes/seg.) en cada uno de los casos anteriores?

Independientemente del número de regı́stros lógicos que contenga cada bloque, la contrloadora añade

1

siempre 40 bytes por bloque, los que ocuparán por sı́ mismos una longitud de lh = 40Bytes

1600bpi = 40 de

3

pulgada. Adicionalmente, después de cada bloque se deja un gap de lg = 5 de pulgada sobre el que se

1

avanza en tg = (3/5)pulgada

= 50

de segundo. De este modo, un bloque que contenga n registros lógicos

30ips

de 120 bytes cada uno ocupará una longitud

lb = lh +

120nBytes

1 + 3n

=

de pulgada

1600bpi

40

y podrá ser leido o grabado en un tiempo

tb =

[(1 + 3n)/40] pulgadas

1 + 3n

=

segundos

60 ips

2400

En consecuencia, un bloque más su correspondiente gap ocupan

l = l b + lg =

25 + 3n

1 + 3n 3

+ =

pulgadas

40

5

40

y se avanza sobre ambos en

t = tb + t g =

1

49 + 3n

1 + 3n

+

=

segundos

2400

50

2400

Si la longitud útil de la cinta es de 2400 pies, entonces el tiempo total de lectura T será

T =

12 × 2400 × t

12 × (49 + 3n) × 40

480 × (49 + 3n)

=

=

segundos

l

25 + 3n

25 + 3n

Y la velocidad efectiva de transferencia R será

R=

120n

120n × 2400

288000n

=

=

bytes/segundo

t

49 + 3n

49 + 3n

(a) Haciendo n = 5, se tiene T5 =

480×(49+15)

25+15

(b) Haciendo n = 77, se tiene T77 =

= 768 segundos.

480×(49+231)

25+231

= 525 segundos.

Página 3 de 4

Segundo Parcial

Organización del Computador I

2 de Diciembre de 2003

(c) Reemplazando los valores de n en la expresión obtenida para R, se tiene

R5 =

288000 × 5

= 22500 bytes/segundo

49 + 15

y

R77 =

288000 × 77

= 79200 bytes/segundo

49 + 231

(12) 6. Considere la memoria principal del ejercicio (4) trabajando con una cache de 4096 lı́neas y bloques de

16 palabras de la que se sabe, además, que NO es asociativa por conjuntos. Con la cache inicialmente

vacı́a, el procesador direcciona las siguientes posiciones, obteniendo los resultados que se especifican:

1) 000000h MISS 2) 00000Ch ???? 3) 333334h MISS 4) 330004h MISS 5) 330008h ???? 6) 000000h HIT

(a) El segundo requrimiento, ¿resultará en MISS o HIT ? ¿Y el quinto?

(b) Diga qué tipo de correspondencia emplea la cache.

Dentro del marco de este curso, si una cache NO es de correspondencia asociativa por conjuntos, entonces

sólo podrı́a ser de correspondencia directa o de correspondencia totalmente asociativa.

(a) Para cualquiera de los dos tipos de cache, el segundo requerimiento resultará en HIT, ya que la

lı́nea correspondiente debió cargarse a consecuencia del primer requerimiento. De igual modo, el cuarto

requerimiento garantiza que el quinto tanbién resulte en HIT.

(b) Si la cache fuese directa, entonces el cuarto requerimiento hubiese desalojado la lı́nea 000h, y el sexto

requerimiento hubiese resultado un MISS. En consecuencia, la cache debe ser totalmente asociativa.

Página 4 de 4