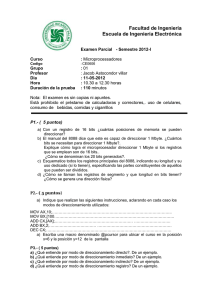

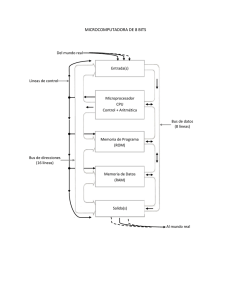

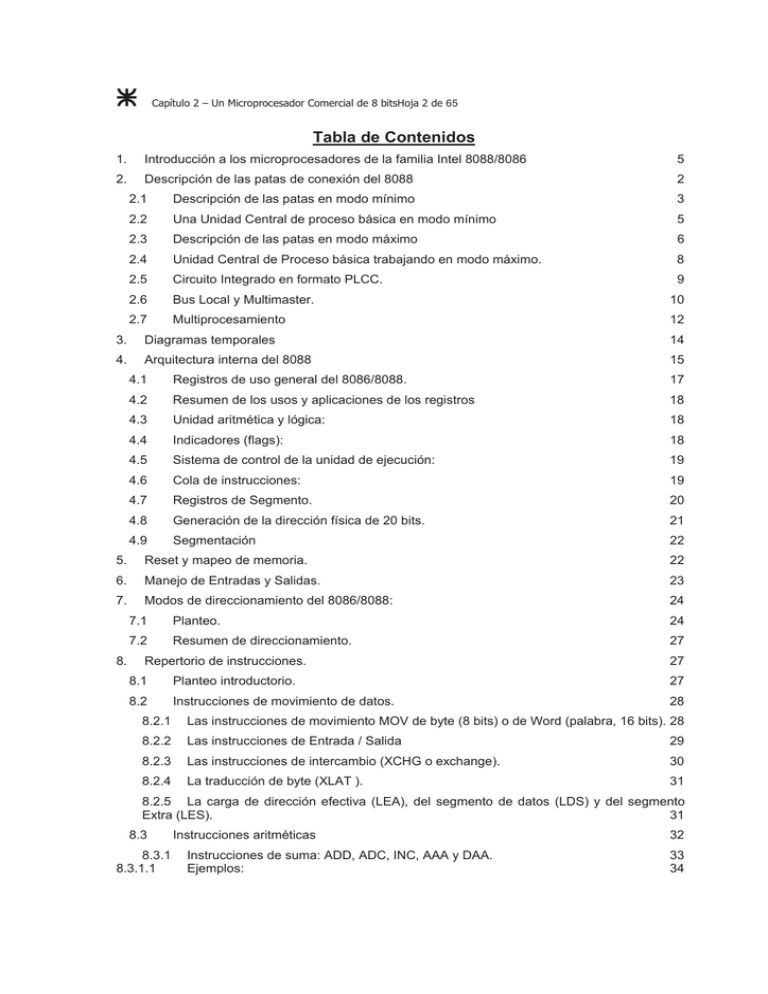

Microprocesador 8088

Anuncio