PDF 319 KB

Anuncio

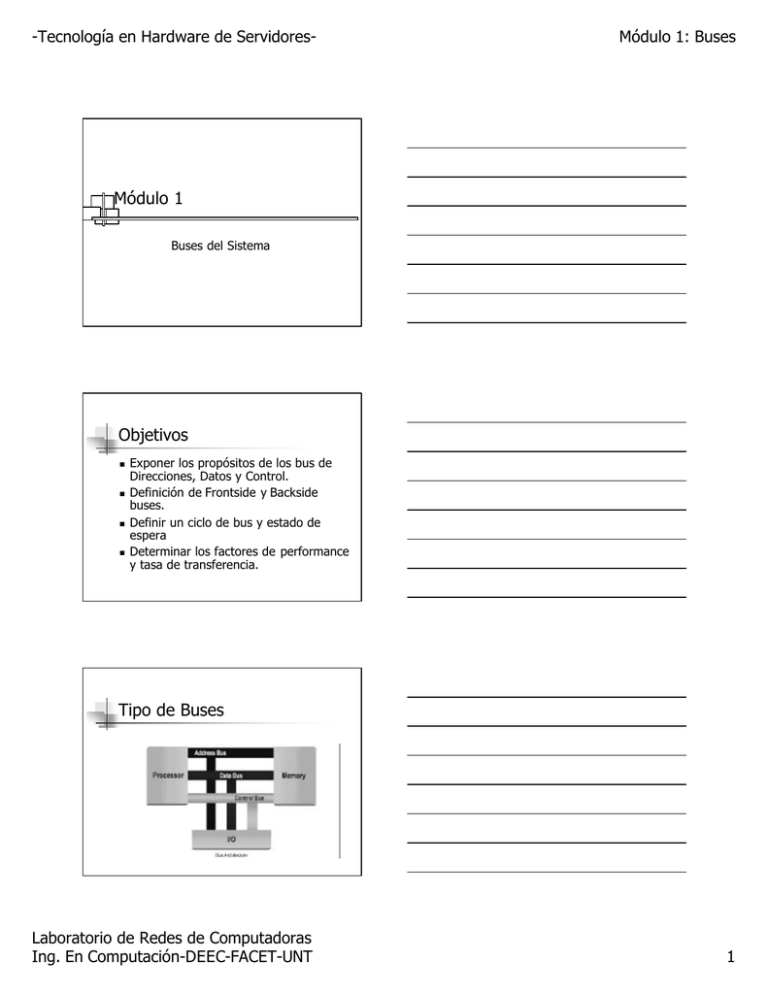

-Tecnología en Hardware de Servidores- Módulo 1: Buses Módulo 1 Buses del Sistema Objetivos n n n n Exponer los propósitos de los bus de Direcciones, Datos y Control. Definición de Frontside y Backside buses. Definir un ciclo de bus y estado de espera Determinar los factores de performance y tasa de transferencia. Tipo de Buses Laboratorio de Redes de Computadoras Ing. En Computación-DEEC-FACET-UNT 1 -Tecnología en Hardware de Servidores- Módulo 1: Buses Bus de Direcciones Bus de Direcciones (Ejemplos) Procesador Líneas Direcciones Max. Mem. Direccionable 80286 24 16 MB 80386/486 32 4 GB Pentium 32 4 GB Pentium Pro P. II, III, IV 36 36 64 GB 64 GB P. II y III Xeon 36 64 GB Itanium 64 2^64 B Alpha 21164 Alpha 21264 40 44 1 TB 16 TB Bus de Datos Laboratorio de Redes de Computadoras Ing. En Computación-DEEC-FACET-UNT 2 -Tecnología en Hardware de Servidores- Módulo 1: Buses Bus de Datos (Ejemplos) Procesador 8086/80286 Ancho Bus Datos 16 Bits 80386/486 32 Bits Pentium/Pentium Pro Pentium II, III, 4 64 Bits 64 Bits Pentium II y III Xeon Itanium 64 Bits 64 Bits Alpha 21164/264 64 Bits (128 bits Cache) Bus de Control Dual Independent Bus (DIB) n GTL+ Bus n n n n Local bus que conecta Procesador, Controladores de Memoria y de I/O Opera a 66 MHz o 100 MHz Usado por Pentium II y Pentium Pro AGTL+ Bus n n n Assisted (o Accelerated) GTL+ 100 MHz, 133 MHz o superior Pentium III y posteriores Laboratorio de Redes de Computadoras Ing. En Computación-DEEC-FACET-UNT 3 -Tecnología en Hardware de Servidores- Módulo 1: Buses Frontside y Backside Bus n Frontside Bus n Backside Bus n n n n Conecta Procesador, Memoria e I/O Conecta el Core del Procesador con el Cache L2 Pentium Pro & Xeon frecuencia igual a la del Core Pentium II y III (pre-coppermine) mitad de la frecuencia del Core Dual Independent Bus (DIB) n Sin backside bus (Pentium) DIB n Backside Bus (1/2 Velocidad) Laboratorio de Redes de Computadoras Ing. En Computación-DEEC-FACET-UNT 4 -Tecnología en Hardware de Servidores- Módulo 1: Buses DIB n Backside Bus (Full Speed) Ciclos de Bus Performance del Bus Laboratorio de Redes de Computadoras Ing. En Computación-DEEC-FACET-UNT 5 -Tecnología en Hardware de Servidores- Módulo 1: Buses Zero Wait State One Wait State Tasa de Transferencia Máximo Laboratorio de Redes de Computadoras Ing. En Computación-DEEC-FACET-UNT 6 -Tecnología en Hardware de Servidores- Módulo 1: Buses Ciclos con Ráfagas (“Burst”) Tasa de Transferencia (Burst) Nota: El tiempo de Direccionamiento no se incluye en está formula. Comparación de Velocidad de Buses Laboratorio de Redes de Computadoras Ing. En Computación-DEEC-FACET-UNT 7