Primer Parcial

Anuncio

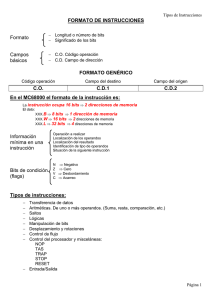

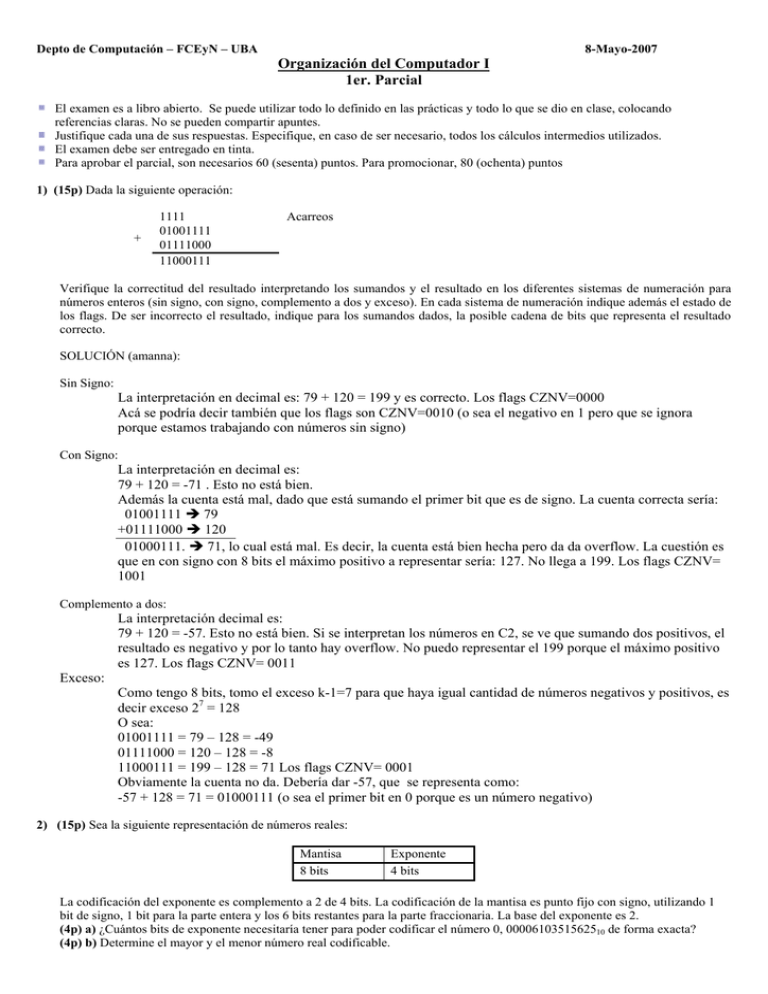

Depto de Computación – FCEyN – UBA 8-Mayo-2007 Organización del Computador I 1er. Parcial El examen es a libro abierto. Se puede utilizar todo lo definido en las prácticas y todo lo que se dio en clase, colocando referencias claras. No se pueden compartir apuntes. Justifique cada una de sus respuestas. Especifique, en caso de ser necesario, todos los cálculos intermedios utilizados. El examen debe ser entregado en tinta. Para aprobar el parcial, son necesarios 60 (sesenta) puntos. Para promocionar, 80 (ochenta) puntos 1) (15p) Dada la siguiente operación: + 1111 01001111 01111000 11000111 Acarreos Verifique la correctitud del resultado interpretando los sumandos y el resultado en los diferentes sistemas de numeración para números enteros (sin signo, con signo, complemento a dos y exceso). En cada sistema de numeración indique además el estado de los flags. De ser incorrecto el resultado, indique para los sumandos dados, la posible cadena de bits que representa el resultado correcto. SOLUCIÓN (amanna): Sin Signo: La interpretación en decimal es: 79 + 120 = 199 y es correcto. Los flags CZNV=0000 Acá se podría decir también que los flags son CZNV=0010 (o sea el negativo en 1 pero que se ignora porque estamos trabajando con números sin signo) Con Signo: La interpretación en decimal es: 79 + 120 = -71 . Esto no está bien. Además la cuenta está mal, dado que está sumando el primer bit que es de signo. La cuenta correcta sería: 01001111 Î 79 +01111000 Î 120 01000111. Î 71, lo cual está mal. Es decir, la cuenta está bien hecha pero da da overflow. La cuestión es que en con signo con 8 bits el máximo positivo a representar sería: 127. No llega a 199. Los flags CZNV= 1001 Complemento a dos: La interpretación decimal es: 79 + 120 = -57. Esto no está bien. Si se interpretan los números en C2, se ve que sumando dos positivos, el resultado es negativo y por lo tanto hay overflow. No puedo representar el 199 porque el máximo positivo es 127. Los flags CZNV= 0011 Exceso: Como tengo 8 bits, tomo el exceso k-1=7 para que haya igual cantidad de números negativos y positivos, es decir exceso 27 = 128 O sea: 01001111 = 79 – 128 = -49 01111000 = 120 – 128 = -8 11000111 = 199 – 128 = 71 Los flags CZNV= 0001 Obviamente la cuenta no da. Debería dar -57, que se representa como: -57 + 128 = 71 = 01000111 (o sea el primer bit en 0 porque es un número negativo) 2) (15p) Sea la siguiente representación de números reales: Mantisa 8 bits Exponente 4 bits La codificación del exponente es complemento a 2 de 4 bits. La codificación de la mantisa es punto fijo con signo, utilizando 1 bit de signo, 1 bit para la parte entera y los 6 bits restantes para la parte fraccionaria. La base del exponente es 2. (4p) a) ¿Cuántos bits de exponente necesitaría tener para poder codificar el número 0, 0000610351562510 de forma exacta? (4p) b) Determine el mayor y el menor número real codificable. Depto de Computación – FCEyN – UBA 8-Mayo-2007 Organización del Computador I 1er. Parcial (4p) c) ¿Qué números reales fueron codificados en 0x03F y 0xFF4? (3p) d) ¿La representación es única? SOLUCIÓN (dgonzalez): a) Se necesitan al menos los 8 bits de la mantisa y 4 para el exponente. (2^(-6)*2^(-8)) b) El mayor numero es 011111110111 = ((-1) ^ 0)*(1-2^(-6)+1)*2^(7) = 254 El menor numero es 111111111111 = ((-1) ^ 1)* (1-2^(-6)+1)*2^(7) = -254 c) 0x03F = 0000 0011 1111 = +(2^(-5)+2^(-6))*2^(-1) 0xFF4 = 1111 1111 0100 = -(1-2^(-6)+1)*2^(4) d) No tiene representación única si tomamos 0100 0000 0000 y 0010 0000 0001 representan el 1. 3) (25p) El microcontrolador MSP430 tiene 16 registros (R0. . .R15) de 16 bits (tamaño de la palabra). Posee las siguientes instrucciones: Dos Operandos MOV(.B) src,dst ADD(.B) src,dst ADDC(.B) src,dst SUB(.B) src,dst SUBC(.B) src,dst CMP(.B) src,dst DADD(.B) src,dst BIT(.B) src,dst BIC(.B) src,dst BIS(.B) src,dst XOR(.B) src,dst AND(.B) src,dst Un/Ningún Operando RRC(.B) dst RRA(.B) dst PUSH(.B) src SWPB dst CALL dst RETI SXT dst Jumps JEQ/JZ Label JNE/JNZ Label JC Label JNC Label JN Label JGE Label JL Label JMP Label Las instrucciones trabajan todas con palabras, a menos que se agregue .B, en cuyo caso trabaja en modo Byte. Todos los jumps realizan un salto relativo de 10 bits. Los modos de direccionamiento posibles son: Modo Registro Indexado Inmediato Sintaxis Rn X(Rn) #N Descripción El contenido del registro es el operando. (Rn+X) apunta al operando. X es guardado en la siguiente palabra. La palabra siguiente contiene la constante absoluta N. Los operandos src pueden tener cualquiera de los 3 modos de direccionamiento. Por otro lado, los operandos dst pueden tener sólo los primeros 2 modos. (20p) a) Se pide diseñar el formato de instrucción de 16 bits, más operandos adicionales según describen los modos de direccionamiento. (5p) b) El set de instrucciones del MSP430, no incluye la instrucción de salto condicional JLEU (menor o igual en notación sin signo). ¿Cómo podría simularse? SOLUCIÓN (dgonzalez): a) Modo SRC Registro 00 Indexado 01 Inmediato 11 Registros SRC/DST R0 000 R1 001 R2 010 R3 011 Modo DST Registro 0 Indexado 1 Registros SRC/DST R4 100 R5 101 R6 110 R7 111 Depto de Computación – FCEyN – UBA 8-Mayo-2007 Organización del Computador I 1er. Parcial Byte / Word Byte 1 Word 0 Código de operación Byte/Word Modo DST Instrucción tipo 1: Modo SRC - - - - - - - Instrucción MOV ADD ADDC SUB SUBC CMP - SRC - - Código 0001 0010 0011 0100 0101 0110 DST - - Instrucción DADD BIT BIC BIS XOR AND - - - - Código 0111 1000 1001 1010 1011 1100 Código de operación 1 1 0 - - Instrucción RRC RRA PUSH - 0 0 0 - Código 000 001 010 Modo DST/SRC Byte/Word Instrucción tipo 2: - - Instrucción SWPB CALL SXT RETI DST/SRC - - - - Código 011 100 101 111 Nota: Para SWPB, CALL y SXT que no utilizan el bit de Modo DST/SRC entonces el bit vale 0. Para la instrucción RETI el bit de Modo DST/SRC vale 0 y los 4 bits de DST/SRC también valen 0. Instrucción tipo 3: Código de Jcc 1 1 1 - Instrucción JEQ/JZ JNE/JNZ JC JNC - Label / Etiqueta - Código 000 001 010 011 - - - - - - Instrucción JN JGE JL JMP - - - - Código 100 101 110 111 b) Puede utilizarse un salto por igualdad (JZ) y luego un salto por carry (JC), para simular el salto de menor o igual sin signo. 4) (20p) Se pide construir el módulo que decodifica el modo de direccionamiento de la arquitectura ORGA1. El dispositivo tiene 6 entradas (e1,..., e6) que indican los 6 bits que identifican el tipo de direccionamiento y una salida por cada tipo de direccionamiento y registro. En caso que el modo no incluya registro debe devolverse 0 en las salidas de los registros. Depto de Computación – FCEyN – UBA 8-Mayo-2007 Organización del Computador I 1er. Parcial 0 1 2 DECO SOLUCIÓN (dgonzalez): 0 1 2 DECO e1 e2 e3 e4 e5 e6 0 1 2 3 4 5 6 7 Inmediato Directo Indirecto Registro Indirecto Registro Indexado R0 R1 R2 R3 R4 R5 R6 R7 0 1 2 3 4 5 6 7 (Otra opción para su resolución seria construir los decodificadores con compuertas básicas) 5) (25p) Dado el siguiente código escrito en arquitectura ORGA1 y el vuelco de memoria que se encuentra debajo. Suponiendo que el programa se encuentra cargado a partir de la posición 0x6140. Todos los flags y registros comienzan en 0, excepto el Program Counter cuyo valor inicial es 0x6143 y el Stack Pointer que empieza en 0xFFEE. dato1 dato2 cont inicio : : : : resto : comparo : 4530 +0 F303 +1 ABCD inc : fin : +2 21E2 +3 6530 DW 0x1C18 DW 0x4532 DW 0x4533 MOV R1,dato1 MOV R2,[dato2] ADD R2,[R1] SUB [R2],[[cont]] CMP R1,R3 JE fin ADD R3,1 JMP comparo MOV [R2],FFFF ret +4 8000 +5 1840 +6 95B3 +7 C925 +8 A639 +9 ECBD +A FAF0 +B ABCD +C D788 +D A631 +E F17B (5p) a) Indicar las direcciones de memoria donde se encuentra cada instrucción. (5p) b) Mostrar cual es la codificación del salto condicional. (15p) c) Realizar un seguimiento del programa hasta encontrar una instrucción inválida. ACLARACIÓN: No hace falta hacer la decodificación detallada para cada instrucción. Alcanza con indicar cuantos operandos tiene y el tamaño total que ocupa en memoria cada instrucción. +F 49F6 Depto de Computación – FCEyN – UBA 8-Mayo-2007 Organización del Computador I 1er. Parcial SOLUCIÓN: a) Posición 0x6140 0x6141 0x6142 0x6143 0x6145 0x6147 0x6148 0x614A 0x614B 0x614C 0x614E 0x6150 0x6152 Etiquetas dato1 : dato2 : cont : inicio : Instrucciones DW 0x1C18 DW 0x4532 DW 0x4533 MOV R1,dato1 MOV R2,[dato2] ADD R2,[R1] SUB [R2],[[cont]] CMP R1,R3 JE fin ADD R3,1 JMP comparo MOV [R2],FFFF ret resto : comparo : inc : fin : b) JE fin 1 1 1 1 0 0 F 0 1 1 0 0 0 0 0 0 1 0 0 4 c) PC 0x6143 0x6145 0x6147 0x6148 0x614A Instrucción MOV R1, dato1 MOV R2, [dato2] ADD R2, [R1] SUB [R2], [[cont]] 0x0333 Deco. INVALIDA Fech de Ins. 0x6144 0x6146 0x6148 0x6149 Flags - Fech de Datos 0x6145 0x6147 0x6148 0x614A Acción R1 = 0x6140 R2 = 0x4532 R2 = 0x4532 + [0x6140] = 0x614A [0x614A] = 0x6863 – 0x6530 = 0x0333