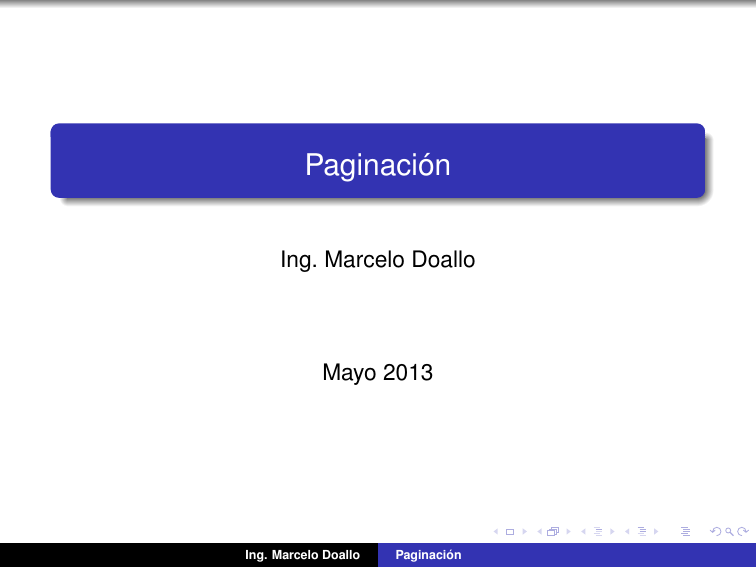

Paginaci´on

Anuncio

Paginación Ing. Marcelo Doallo Mayo 2013 Ing. Marcelo Doallo Paginación Paginación Es la conversión de direcciones lineales en fı́sicas. Implica también: Derechos de acceso. Especifica el tipo de cache utilizado. Cuando NO está activada la paginación, entonces las direcciones lineales coinciden con las fı́sicas. Si está activada la paginación entra en funciomiento esta conversión de direcciones lineales a fı́sicas. Ing. Marcelo Doallo Paginación Esquema general Ing. Marcelo Doallo Paginación Bits que controlan la paginación WP y PG en CR0 (bit 16 y bit 31, respectivamente). LME y NXE en IA32 EFER MSR (bit 8 y bit 11,respectivamente). PSE, PAE, y PGE en CR4 (bit 4, bit 5, y bit 7, respectivamente). Para que la paginación esté activada requiere, CR0.PE=1, CR0.PG=1. Ing. Marcelo Doallo Paginación Tres modos de paginación IA-32 (32 bits): CR4.PAE=0, el comportamiento está regido por CR0.WP, CR4.PSE, y CR4.PGE PAE: CR4.PAE=1 y IA32 EFER.LME=0, el comportamiento está regido por CR0.WP, CR4.PGE y IA32 EFER.NXE IA-32e: CR4.PAE=1 y IA32 EFER.LME=1, el comportamiento está regido por CR0.WP, CR4.PGE y IA32 EFER.NXE Ing. Marcelo Doallo Paginación Propiedades de los diferentes modos de paginación Ing. Marcelo Doallo Paginación Submodos de la paginación IA-32e Modo compatibilidad: Direcciones lineales de 32 bits, los bits 47 a 32 valen 0. Modo 64 bits: Direcciones lineales de 48 bits denominadas direcciones canónicas. ¿Cómo se define el submodo?: Lo determina el registro cs, dado que si está corriendo código de 16 o 32 bits está en submodo compatibilidad. Si está corriendo código de 64 bits está en submodo 64 bits. Ing. Marcelo Doallo Paginación Habilitación y cambio de modos de paginación Ing. Marcelo Doallo Paginación Significado de algunos otros bits en paginación CR0.WP=0: El supervisor puede escribir una página read-only. CR0.WP=1: Ni el nivel supervisor puede escribir una página read-only. CR4.PSE=0: En paginación de 32 bits indica que las páginas serán de 4 K. CR4.PSE=1: En paginación de 32 bits indica que las páginas serán de 4 KByte o de 4 Mbyte. CR4.PSE No tiene significado en paginación PAE ni IA-32e. Ing. Marcelo Doallo Paginación Paginación en IA-32 Ing. Marcelo Doallo Mayo 2013 Ing. Marcelo Doallo Paginación en IA-32 Paginación con páginas de 4 KBytes en IA-32 Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 Detalle de CR3 en IA-32 PCD=1, indica que el directorio de página en uso no estará en cache. PWT=1, indica uso de técnica de Write-through para el cache del directorio de página en uso, si CR0.CD=1 Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 Selección de la entrada de directorio de página (PDE) Bits 31:12 salen de CR3. Bits 11:2 salen de bits 31:22 de la dirección lineal. Bits 1:0 en 0. Una entrada de directorio de página son 4 bytes. Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 Detalle de PDE Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 Selección de la entrada de tabla de páginas (PTE) CR4.PSE = 0 ó PS=0 en la PDE. Bits 31:12 salen de PDE. Bits 11:2 salen de bits 21:12 de la dirección lineal. Bits 1:0 en 0. Una entrada de tabla de páginas son 4 bytes. Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 Detalle de PTE Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 Paginación con páginas de 4 MBytes en IA-32 CR4.PSE=1 para habilitar páginas de 4 MBytes. Ing. Marcelo Doallo Paginación con páginas de 4 MBytes en IA-32 Selección de la entrada de directorio de página (PDE) Bits 31:12 salen de CR3. Bits 11:2 salen de bits 31:22 de la dirección lineal. Bits 1:0 en 0. Una entrada de directorio de página son 4 bytes. Ing. Marcelo Doallo Paginación con páginas de 4 MBytes en IA-32 Detalle de PDE Ing. Marcelo Doallo Paginación con páginas de 4 MBytes en IA-32 PSE-36 (Nota 2) Si el mecanismo PSE-36 no está soportado por el procesador, M es 32 y la fila “M-20:13” ni tiene sentido. Si el mecanismo PSE-36 está soportado, M tiene un mı́nimo de 40 y su valor es MAXPHYADDR. Ing. Marcelo Doallo Paginación con páginas de 4 MBytes en IA-32 Detalle de MAXPHYADDR MAXPHYADDR se obtiene mediante la instrucción CPUID. Ese valor depende del procesador, por lo que es de sólo lectura. CPUID.80000008H:EAX[7:0] informa la cantidad de bits de dirección fı́sica que soporta el procesador. Este valor es MAXPHYADDR y es a lo sumo 52. CPUID.80000008H:EAX[15:8] informa la cantidad de bits de dirección lineal que soporte el procesador. Ing. Marcelo Doallo Paginación con páginas de 4 MBytes en IA-32 Obtención de MAXPHYADDR mov eax,80000008h ;Selector de CPUID. cpuid ; Luego analizar eax[7:0] y eax[15:8] Ing. Marcelo Doallo Paginación con páginas de 4 MBytes en IA-32 Paginación en IA-32 con PAE Ing. Marcelo Doallo Mayo 2013 Ing. Marcelo Doallo Paginación en IA-32 con PAE Paginación con PAE CR0.PG = 1 CR4.PAE = 1 IA32 EFER.LME = 0 Paginación PAE convierte direcciones lineales de 32-bit a direcciones fı́sicas de hasta 52-bits, dependiendo de MAXPHYADDR (<52). Aunque 52 bits Corresponde a 4 PBytes, las direcciones lineales están limitadas a 32 bits (4GB), entonces sólo 4 GB son direccionables simultáneamente. Ing. Marcelo Doallo Paginación en IA-32 con PAE Paginación con páginas de 4 KBytes en IA-32 con PAE Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Detalle de CR3 con PAE Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Selección de una entrada de tabla de puntero de directorio de página (PDPTE) Inicio de tabla determinado por CR3. Bits 31:30 de la dirección lineal seleccionan un registro PDPTE. Una entrada de tabla de puntero de directorio de página (PDPTE) son 8 bytes. Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Detalle de PDPTE Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Selección de la entrada de directorio de página (PDE) Bits 51:12 salen de PDPTE. Bits 11:3 salen de bits 29:21 de la dirección lineal. Bits 2:0 en 0. Una entrada de directorio de página son 8 bytes. Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Detalle de PDE PS=0. Porque las páginas son de 4 KBytes. Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Selección de la entrada de tabla de páginas (PTE) Si PS en la PDE está en 0, entonces esa entrada de la PDE apunta a una tabla de páginas de 4-KByte. Bits 51:12 salen de PDE. Bits 11:3 salen de bits 20:12 de la dirección lineal. Bits 2:0 en 0. Una entrada de tabla de páginas son 8 bytes. Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Detalle de PTE Ing. Marcelo Doallo Paginación con páginas de 4 KBytes en IA-32 con PAE Paginación con páginas de 2 MBytes en IA-32 con PAE PDE con PS=1 Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE Selección de la entrada de directorio de página (PDE) Bits 51:12 salen de PDPTE. Bits 11:3 salen de bits 29:21 de la dirección lineal. Bits 2:0 en 0. Una entrada de directorio de página son 8 bytes. Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE Detalle de PDE PS=1. Porque las páginas son de 2 MBytes. Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE Protección combinada Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE Comando útil en bochs info tab Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE TIP’s de programación Align 4096 page directory base: pd entry 0 equ ($-page directory base)/4 ; dd (page table base) + PD DEFAULT CODE ATTS ; align 4096 page table base: pt entry 0 equ ($-page table base)/4 dd 0b8000h + PT DEFAULT CODE ATTS Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE TIP’s de programación (2) PD PD PD PD PD PD PD PD ; PRESENT EQU 01h READBAR READWRITE EQU 02h USER SUPERVISORBAR EQU 04h WRITETHROUGH EQU 08h CACHEDISABLED EQU 10h ACCESSED EQU 20h PAGESIZE 4KBAR EQU 80h GLOBALPAGE EQU 100h PD DEFAULT CODE ATTS EQU PD PRESENT + PD CACHEDISABLED Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE TIP’s de programación (3) PT PT PT PT PT PT PT PT PT PRESENT EQU 01h READBAR READWRITE EQU 02h USER SUPERVISORBAR EQU 04h WRITETHROUGH EQU 08h CACHEDISABLED EQU 10h ACCESSED EQU 20h DIRTY EQU 40h PAGEATTRINDEX EQU 80h GLOBALPAGE EQU 100h ; PT DEFAULT CODE ATTS EQU PT PRESENT + PT CACHEDISABLED Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE TIP’s de programación (4) mov eax, page directory base ; cargo en cr3 mov cr3, eax ; base del directorio mov eax, cr0 ; seteo el bit de paginacion or eax,80000000h ; seteo el MSB mov cr0, eax ; activo la unidad de paginación Ing. Marcelo Doallo Paginación con páginas de 2 MBytes en IA-32 con PAE