Clase Lab 1

Anuncio

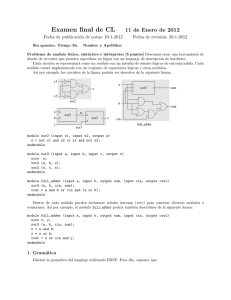

LAB 1 Introducción a Verilog Laboratorio de Sistemas Digitales ELO212 Primer Semestre de 2010 Objetivos Generales Conocer un lenguaje de tipo HDL. Trabajar bajo un ambiente ISE. Diseñar un circuito digital usando HDL. Diseñar módulos de prueba. Familiarizarse con el ambiente de edición Webpack Xilinx. Recursos Disponibles Software Xilinx ISE Design Suite. Software ModelSIM de Mentor Graphics. Manuales y Tutoriales sobre Verilog. Mi Primer Programa en Verilog f(a,b,c,d) = abc + cb’ + a’c’ Descripción de Circuitos: Estructural. De comportamiento. Descripción Estructural module sOr(a, b, c, f) input a, b, c; output f; or (f, a, b, c); endmodule Descripción Basada en el Comportamiento de la Red module sOr(a, b, c, f) input a, b, c; output f; assign f = a | b | c; endmodule Bloque always (1) module sOr(a, b, c, f) input a, b, c; output reg f; always@(c) begin if (c) f = a; else f = b & c; end endmodule Bloque always (2) module sOr(a, b, c, f) input a, b, c; output reg f; always@(b or c) begin if (c && b) f = a; else f = b & c; end endmodule Uso de Buses module CounterA(Sum, w); output reg [0:1] Sum; input [0:3] w; always @(w) begin if (w == 0) Sum = 0; else if (w == 1) Sum = 1; else if (w == 2) Sum = 1; else Sum = 2; end endmodule Definición de Constantes Sin especificación de largo Octal: 'o372 Hexadecimal: 'hFe31 Decimal: 321 Con especificación de tamaño Binario: 5'b01101 Hexadecimal: 12'h72 Decimal: 11'd3029 Diseño Jerárquico module TheCounter(Sum, w); output [0:4] Sum; input [0:15] w; wire [0:2] Sum1, Sum2, Sum3, Sum4; CounterA myAdder0 (Sum1, w[0:3]); CounterA myAdder1 (Sum2, w[4:7]); // ... assign Sum = Sum1 + Sum2 + Sum3 + Sum4; endmodule Decodificador BCD – Decimal (1) // // // // // // // // // // 1-of-10 inverting decoder/demultiplexer. +----------+ +-------------------------------+ /Y0 |1 +--+ 16| VCC | S3| S2| S1| S0|/Y0|/Y1|...|/Y9| /Y1 |2 15| S0 |---+---+---+---+---+---+---+---| /Y2 |3 14| S1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | /Y3 |4 13| S2 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | /Y4 |5 7442 12| S3 | . | . | . | . | 1 | 1 | . | 1 | /Y5 |6 11| /Y9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | /Y6 |7 10| /Y8 | 1 | 0 | 1 | X | 1 | 1 | 1 | 1 | GND |8 9| /Y7 | 1 | 1 | X | X | 1 | 1 | 1 | 1 | +----------+ +-------------------------------+ Decodificador BCD – Decimal (2) module v7442(A, Y); input [3:0] A; output [9:0] Y; assign assign assign assign assign assign assign assign assign assign endmodule Y[0] Y[1] Y[2] Y[3] Y[4] Y[5] Y[6] Y[7] Y[8] Y[9] = = = = = = = = = = ~(A ~(A ~(A ~(A ~(A ~(A ~(A ~(A ~(A ~(A == == == == == == == == == == 4'b0000); 4'b0001); 4'b0010); 4'b0011); 4'b0100); 4'b0101); 4'b0110); 4'b0111); 4'b1000); 4'b1001); Circuito Verificador module test_v7442; reg [3:0] A; // Inputs wire [9:0] Y; // Outputs v7442 uut ( // Instantiate the Unit Under Test (UUT) .A(A), .Y(Y) ); initial begin A = 0; #(100) // Initialize Inputs // Wait 100 time unit for global reset to finish // Add stimulus here repeat (16) begin #(10) A = A + 1; $display ("t=%t \t\t\t A=%d \t\t\t Y=%b", $realtime, A, Y); end end endmodule Trabajo Previo (1) Estudio de Verilog (punto 2.2) Diseño de un programa en Verilog f(a,b,c,d) = a’b + b’d + abc Descripción estructural Descripción de comportamiento (punto 2.3) Diseño usando bloque always Si ctl es 1 f = a’b + b’d + abc Si ctl es 0 f = b’c’d Trabajo Previo (2) (punto 2.4) Modificar módulo CounterA (punto 2.5) Usando diseño jerárquico Contar secuencias 11 en palabras de 4 bit Contador de secuencias 11 en palabras de 16 bit Diseño de módulos de prueba Circuito del punto 2.3 (bloque always) Circuito del punto 2.5 (contador sec.) En el Laboratorio (1) Revisión actividades previas. Simulación temporal y funcional. Circuito punto 2.3 (bloque always y ctl) Circuito contador de secuencias Uso de monitor(). Uso de $display y $strobe. En el Laboratorio (2) Diseño de un circuito: Si entrada tiene número par de unos: 1100111101101010, -> 0001111111111000 Si entrada tiene número par de unos: 1101111101101010, p 010 -> 0000000000000010