Dispositivos Lógicos Programables (PLDs)

Anuncio

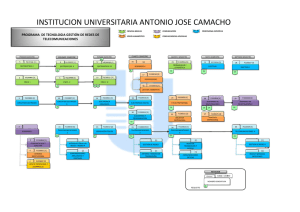

Dispositivos Lógicos Programables (PLDs) Sistemas Digitales II / Electronica Digital II Dispositivos Logicos Programables (PLDs) • Dispositivos Programables Simples (SPLD) • Di Dispositivos iti P Programmables bl C Complejos l j (CPLD) • Arreglo de Compuertas Programables en Campo (Field Programmable Gate Arrays, FPGAs) Sistemas Digitales II / Electronica Digital II Evolución de los Dispositivos Logicos Programables Sistemas Digitales II / Electronica Digital II Dispositivos Lógicos Programables (PLDs) Dispositivos Lógicos Programables Simples (SPLDs) Dispositivos Lógicos Programables Complejos (CPLDs) Arreglo de Compuertas Programables en el Campo (Field Programmable Gate Arrays, FPGAs) Sistemas Digitales II / Electronica Digital II Cuadro Comparativo de los diferentes PLDs Sistemas Digitales II / Electronica Digital II Producción de PLDs Xilinx Altera Lattice Atmel Actel I t l Intel AMD Motorola Philips Vantis Sistemas Digitales II / Electronica Digital II Dispositivos Lógicos Programables Complejos (CPLDs) Sistemas Digitales II / Electronica Digital II CPLDs CPLDS contiene el equivalente de varios PALs/ GALs connectados p por interconnecciones p programmables. g CPLDs pueden reemplazar miles o cientos de miles compuertas p lógicas. g El tiempo de E/S del CPLD es predecible debido a su simple estructura de interconecciones CPLDs contiene ti 16 16-1024 1024 macroceldas ld cada macrocelda equivale a unas 20/40 compuertas (incluyendo un Flip/Flop programable) puede tener desde 20 hasta 381 I/Os hay un trade-off entre el espacio para las macroceldas y el espacio para las interconecciones Sistemas Digitales II / Electronica Digital II Programación de los CPLDs Opciones de Programación one-time programmable el dispositivo es programado una vez y mantiene su programación para siempre usualmente usa fusible para crear/romper una unión de interconección no se puede re-programar, pero normalmente es muy barato sii se d debe b h hacer alguna l modificación difi ió a lla ló lógica i iinterna t del CPLD, el dispositivo se descarta y se usa uno nuevo (no programado) Sistemas Digitales II / Electronica Digital II Programación de los CPLDs (cont.) Borrable por UV la programacion del CPLD es borrada por emisión UV tiene un encapsulado cerámico con una ventana arriba del área del chip este encapsulado especial es bastante caro normalmente se debe remover el CPLD del zócalo para borrarlo/reprogramarlo programación es retenida después de cortar Vcc (no-volatile) programación/borrado es limitada a unos 1000s ciclos Sistemas Digitales II / Electronica Digital II Programación de los CPLDs (cont.) Borrable electricamente borrado y programado del CPLD se hace con una corriente eléctrica el CPLD puede ser programado/borrado en el PCB, no es necesario encapsulado especial o zócalo tiempo de borrado es mucho menor que el borrado UV no-volatile programación/borrado es limitada a unos 1000s ciclos Programación/borrado se lleva a cabo mediante la conección del CPLD a una computadora (una PC cualquiera con un software del fabricante del CPLD). C Como ell CPLD no necesita it ser sacado d d dell sistema/plaqueta en que esta soldado, esto es conocido como In-System-Programmable In System Programmable (ISP). (ISP) Sistemas Digitales II / Electronica Digital II Diseño con CPLDs – Pasos a Seguir Sistemas Digitales II / Electronica Digital II Xilinx XC9500 CPLD Sistemas Digitales II / Electronica Digital II Xilinx XC9500 CPLD - Arquitectura Sistemas Digitales II / Electronica Digital II XC9500 Bloque Funcional Sistemas Digitales II / Electronica Digital II XC9500 Macrocelda Sistemas Digitales II / Electronica Digital II XC9500 – Clock y Reset de una Macrocelda Sistemas Digitales II / Electronica Digital II XC9500 – Asignación de Término Producto de 15 PT Sistemas Digitales II / Electronica Digital II XC9500 – Lógica de Asignación de PTs Sistemas Digitales II / Electronica Digital II XC9500 – Matriz de Conecciones Fast Switch Sistemas Digitales II / Electronica Digital II XC9500 – Bloque de E/S (IO Block) Sistemas Digitales II / Electronica Digital II XC9500 – Modelo de Retardos Lógicos Sistemas Digitales II / Electronica Digital II Familia Comercial del XC9500 Sistemas Digitales II / Electronica Digital II L tti ispXPLD5000MX Lattice i XPLD5000MX (eXpanded Programmable Logic Device) Sistemas Digitales II / Electronica Digital II ispXPLD 5000MX - Diagrama de Bloques Sistemas Digitales II / Electronica Digital II ispXPLD 5000MX – Bloque Multi-Función Sistemas Digitales II / Electronica Digital II ispXPLD 5000MX – Modos de Memoria Sistemas Digitales II / Electronica Digital II ispXPLD 5000MX – Modo Lógico Super-Extenso Sistemas Digitales II / Electronica Digital II ispXPLD 5000MX - Macrocelda Sistemas Digitales II / Electronica Digital II ispXPLD5000MX – Bloque de E/S Sistemas Digitales II / Electronica Digital II ispXPLD5000M – Red de Distribución de Reloj Sistemas Digitales II / Electronica Digital II Porque algunos PLDs tienen PLLs internos ? • Facilita el funcionamiento de la red de relojj • Facilita el incremento de la frecuencia de funcionamiento de la lógica g implementada p • PLL ayuda a: • Remover R retardos t d d de b buffers ff • Controlar el Sesgo (Skew) del reloj • Multiplicar/Dividir la frecuencia de entrada. Sistemas Digitales II / Electronica Digital II ispXPLD5000MX - PLL CLK_IN Input Clock (M) Divider PLL_RST* Programmable +Delay CLK OUT** CLK_OUT** Post-scalar PLL Clock Net (V) Divider Programmable -Delay PLL_LOCK+ Secondary Feedback Clock (K) Divider (N) Divider SEC_OUT _ Clock Net PLL_FBK* • Frequency Range 7 to 160MHz • Multiply From 1 to 32 * Internal Node or Shared I/O Pin + Internal Node ** Shared I/O Pin • Divide From 1 to 32 • Shift Clock +/- 3.5ns in 500ps Steps • Internal and External Feedback Sistemas Digitales II / Electronica Digital II ispXPLD5000MX – Aplicación del PLL ispMACH 51024VG 133 MHz Processor Tsetup = 4.0ns CPLD Tco = 4.5ns Clock A PLL 3.5ns Global Clock 3.5ns Clock A is same phase as Global Clock tco =4.5ns ta Note ta << tsetup = 4ns Data Valid 3.5ns 3.5ns Clock A is advanced by ~ 2ns using PLL Clock A tco =4.5ns ta Data Valid Sistemas Digitales II / Electronica Digital II Global Clock Note ta >> tsetup = 4ns ispXPLD5000MX – E/S Bancos de Alimentación Vref0 GNDO0 Vref3 VCCO0 VCCO3 GNDO3 • Four IO Banks Per Device Bank 0 • Output Standard Support Dependent on: Bank 3 Clk0 Clk3 Clk1 Clk2 Bank 1 Bank 2 – Vcco – Vref • Input Standard Support Dependent on Vref • Multiple Compatible IO Standards Can Be pp in Single g Bank Supported GNDO1 VCCO1 VCCO2 Vref1 GNDO2 Vref2 Sistemas Digitales II / Electronica Digital II ispXPLD5000MX sysIO™ Blocks Chip-to-Memory Chip to Memory SSTL2 I and II SSTL3 I and II HSTL I HSTL III Interface to External RAM Chip-to-Chip Chip to Chip Chip-to-Backplane Chip to Backplane LVTTL LVCMOS 3.3 LVCMOS 2.5 LVCMOS 1.8 Programmable Drive Strength PCI33_3 PCI66 3 PCI66_3 PCIX GTL+ AGP LVDS * LVPECL * SSTL2: Stub Series Terminated Logic g for 2.5V ((for DDR SDRAM memories) HSTL: High Speed Transceiver Logic GTL+: Gunning Transceiver Logic Plus (used in the Pentium buses) AGP: Accelerated Graphics Port Sistemas Digitales II / Electronica Digital II ispXPLD 5000MX – Capacidad de E/S • Cada E/S LVCMOS puede ser configurada con una Corriente de Salida Programable – Minimiza la reflección de señales LVCMOS 3.3 LVCMOS 2.5 LVCMOS 1.8 • 4mA • 5.33 mA • 8 mA • 12 mA • 16 mA • 20 mA • 4mA • 5.33 mA • 8 mA • 12 mA • 16 mA • 4mA • 5.33 mA • 8 mA • 12 mA Además • Por cada E/S se puede: • Fast and Slow Slew Rates (Minimizes Ground Bounce) • Open Drain Outputs • Pull-Up, Pull-Down, Bus-Keeper & No-Connect • Hot Socketing Sistemas Digitales II / Electronica Digital II Aplicaciones de uso de CPLD • Maquinas q de Estado • Lógica de Control • ‘Glue Logic’ para lógica de retardo minimo (Timing Critical Functions) • Handshaking de señales • Decodificación de buses amplios • Buffer B ff d de señales ñ l • Lógica de Interrupción • Lógica de Control de Power-up Sistemas Digitales II / Electronica Digital II Aplicación de uso de CPLD Sistemas Digitales II / Electronica Digital II Aplicación de uso de CPLD Sistemas Digitales II / Electronica Digital II Notas Aplicaciones de Uso de CPLD - Xilinx Sistemas Digitales II / Electronica Digital II Deberes: ☺ E Encontrar t ell CY37256P160-83C CY37256P160 83C Traer informacion tecnica del mismo Macroceldas? Encapsulado? R Rango T Temperatura? t ? Minimo tiempo de retardo? Sistemas Digitales II / Electronica Digital II