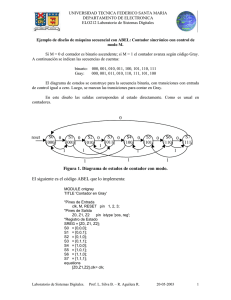

9-Sistemas Secuenciales

Anuncio

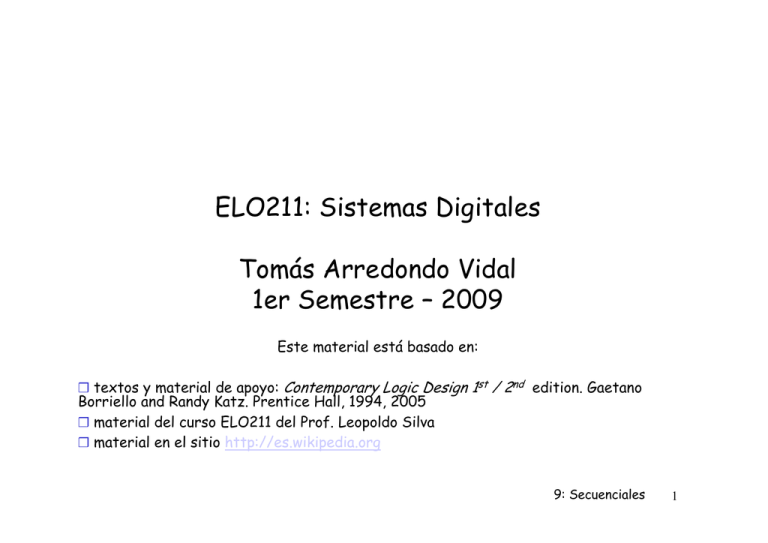

ELO211: Sistemas Digitales Tomás Arredondo Vidal 1er Semestre – 2009 Este material está basado en: ❒ textos y material de apoyo: Contemporary Logic Design 1st / 2nd edition. Gaetano Borriello and Randy Katz. Prentice Hall, 1994, 2005 ❒ material del curso ELO211 del Prof. Leopoldo Silva ❒ material en el sitio http://es.wikipedia.org 9: Secuenciales 1 9-Sistemas Secuenciales 9.1 Maquinas de Estados Finitos 9.2 Mealy y Moore FSMs 9.3 Implementación en Verilog 9: Secuenciales 2 Abstracción de MEFs ❒ Dividir circuito en lógica combinacional y estado (state) ❒ Localizar los enlaces de feedback (loops) ❒ Implementación de elementos de almacenamiento (storage elements) nos da diferentes formas de lógica secuencial Inputs Combinational Logic State Inputs Outputs State Outputs Storage Elements 9: Secuenciales 3 Formas de lógica secuencial ❒ Asincrónica – estados cambian cuandos los inputs cambian (elemento de almacenamiento pueden ser simples alambres of retardos) ❒ Sincrónica – cambios de estados ocurren en todos los elementos de almacenamiento al mismo tiempo (de acuerdo a una senal periodica – el reloj o clock) Clock 9: Secuenciales 4 Elementos de almacenamiento: latches y flip-flops D Q CLK positive edge-triggered flip-flop D CLK Qedge D Q G Qlatch CLK transparent (level-sensitive) latch comportamiento no es el mismo si es que los inputs cambian cuando el clock esta alto 9: Secuenciales 5 Representaciones de maquinas de estados finitos (finite state machines) ❒ Estados: determinado por posibles valores en elementos de almacenamiento ❒ Transiciones: cambios de estado ❒ Reloj (clock): controla cuando los estados pueden cambiar al controlar elementos de almacenamiento ❒ Lógica secuencial ❍ ❍ secuencia traversa una serie de estados basado en secuencia de valores de señales de input (x) 010 001 x=1 111 x=0 x=0 100 x=1 110 9: Secuenciales 6 Diagrama de maquina de estados finitos ❒ Ejemplo: Candado de combinación ❍ 5 estados ❍ 5 auto-transiciones ❍ 6 otras transiciones entre estados ❍ 1 transición de reset (de todos los estados) al estado S1 ERROR closed not equal & new reset S1 closed mux=C1 equal & new not new S2 closed mux=C2 equal & new not new not equal & new not equal & new S3 closed mux=C3 equal & new OPEN open not new 9: Secuenciales 7 Ejemplo: Registro de corrimiento (shift register) ❒ Shift register ❍ input mostrado en arcos de transiciones ❍ valores de output IN mostrado en nodo CLK de estado 0 0 0 0 001 0 OUT3 D Q 110 1 1 101 0 OUT2 D Q 1 010 1 000 D Q 1 100 1 OUT1 111 0 1 1 0 011 9: Secuenciales 8 Ejemplo: Contadores ❒ Contadores ❍ proceden a través de secuencia de estados bien definida en respuesta a enable ❒ Muchos tipos de contadores: binario, BCD, código Gray ❍ ❍ contador de subida de 3 bits: 000, 001, 010, 011, 100, 101, 110, 111, 000, ... contador de bajada de 3-bits: 111, 110, 101, 100, 011, 010, 001, 000, 111, ... 001 000 010 011 100 3-bit up-counter 111 110 101 9: Secuenciales 9 Como convertir diagrama de estados a tabla de transiciones? ❒ Tabla de transiciones: forma tabular de diagrama de estados ❒ Como una tabla de verdad (se especifican todos los outputs para las combinaciones de input) ❒ Ejemplo: contador 001 000 010 011 100 3-bit up-counter 111 110 101 present state 0 000 1 001 2 010 3 011 4 100 5 101 6 110 7 111 next state 001 1 010 2 011 3 100 4 101 5 110 6 111 7 000 0 9: Secuenciales 10 Implementación ❒ Un flip-flop para cada bit de estado ❒ Lógica combinacional basada en codificación C3 0 0 0 0 1 1 1 1 C2 0 0 1 1 0 0 1 1 C1 0 1 0 1 0 1 0 1 N3 N3 0 0 0 1 1 1 1 0 C3 N2 0 1 1 0 0 1 1 0 código en Verilog para mostrar que la función es un input a un D-FF N1 1 0 1 0 1 0 1 0 N1 <= C1’ N2 <= C1C2’ + C1’C2 <= C1 xor C2 N3 <= C1C2C3’ + C1’C3 + C2’C3 <= (C1C2)C3’ + (C1’ + C2’)C3 <= (C1C2)C3’ + (C1C2)’C3 <= (C1C2) xor C3 N2 C3 N1 C3 0 0 1 1 0 1 1 0 1 1 1 1 C1 0 1 0 1 C1 1 0 0 1 C1 0 0 0 0 C2 C2 C2 9: Secuenciales 11 Implementación (cont) ❒ Contador ❍ 3 flip-flops para tener estado ❍ lógica para calcular próximo estado ❍ reloj controla cuando la memoria de los flip-flops cambia • • hay que esperar para que la lógica calcule nuevo valor no hay que esperar mucho para no tener velocidad muy lenta OUT1 D Q OUT2 D Q OUT3 D Q CLK "1" 9: Secuenciales 12 Implementación: Registro de corrimiento ❒ Input determina próximo estado In 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 C1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C2 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 C3 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 N1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 N2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 N3 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 100 0 1 0 0 101 0 0 001 N1 <= In N2 <= C1 N3 <= C2 IN 0 OUT1 D Q 1 1 1 010 1 000 110 D Q 1 1 111 0 0 011 OUT2 OUT3 D Q CLK 9: Secuenciales 13 Ejemplo: Contador mas complejo ❒ Contador Complejo ❍ repite 5 estados en secuencia ❍ secuencia no es una representación numérica binaria ❒ Paso 1: hacer diagrama de transición de estados ❍ contar secuencia: 000, 010, 011, 101, 110 ❒ Paso 2: hacer tabla de transición de estados 000 110 010 101 011 Present State Next State C B A C+ B+ A+ 0 0 0 0 1 0 0 0 1 – – – 0 1 0 0 1 1 0 1 1 1 0 1 1 0 0 – – – 1 0 1 1 1 0 1 1 0 0 0 0 1 1 1 – – – notar condiciones don't care por los estados no usados 9: Secuenciales 14 Ejemplo: Contador mas complejo (cont) ❒ Paso 3: mapas Karnaugh para próximas funciones C+ A B+ C 0 0 0 X X 1 X 1 B A A+ C 1 1 0 X X 0 X 1 B A C 0 1 0 X X 1 X 0 B C+ <= A B+ <= B’ + A’C’ A+ <= BC’ 9: Secuenciales 15 Contadores con estados iniciales ❒ Estados iniciales ❍ durante el inicio, el contador puede estar en un estado sin usar o invalido ❍ el diseñador debe garantizar que eventualmente entre en un estado valido ❍ diseñar para que estados inválidos transiciones a validos 111 111 001 000 001 110 000 100 110 100 010 101 011 010 101 011 9: Secuenciales 16 Contadores con estados iniciales (cont) ❒ Generar tabla de transición de estados con estados iniciales C+ A B+ C 0 0 0 0 1 1 1 1 A B Present State Next State C B A C+ B+ A+ 0 0 0 0 1 0 0 0 1 1 1 0 0 1 0 0 1 1 0 1 1 1 0 1 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 1 1 0 0 A+ C 1 1 0 1 1 0 0 1 A C 0 1 0 0 0 1 0 0 B B 111 001 000 110 100 010 101 011 9: Secuenciales 17 Actividad ❒ Contador up-down de 2-bits (2 inputs) ❍ ❍ dirección: D = 0 para up, D = 1 para down cuenta: C = 0 para parar, C = 1 para contar C=0 D=X 00 C=1 D=0 11 C=1 D=1 01 C=0 D=X C=0 D=X C=1 D=0 C=1 D=0 10 C=1 D=0 C=0 D=X S1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 S0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 N1 0 0 0 1 0 0 1 0 1 1 1 0 1 1 0 1 N0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 9: Secuenciales 18 Actividad (cont) S1 S1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 S0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 N1 0 0 0 1 0 0 1 0 1 1 1 0 1 1 0 1 N0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 C 1 0 1 0 0 1 0 1 S0 C D N1 = C’S1 + CDS0’S1’ + DS0S1 + CD’S0S1’ + D’S0’S1 S1 0 1 1 0 0 1 1 0 1 0 0 1 1 0 0 1 N0 = CS0’ + C’S0 D S0 9: Secuenciales 19 9-Sistemas Secuenciales 9.1 Maquinas de Estados Finitos 9.2 Mealy y Moore FSMs 9.3 Implementación en Verilog 9: Secuenciales 20 Modelo general MEF (o FSM) ❒ Valores almacenados en registros representan el estado actual del circuito: y(n) ❒ Lógica combinacional calcula ❍ ❍ próximo estado, y(n+1): FPE (Función Próximo Estado) • función de estados actuales e inputs outputs: FS (Función Salida) • Mealy: función de estado actual e inputs, z = F(y, x) • Moore: solo función de estado actual, z = F(y) Inputs: x lógica output FS lógica próximo estado: FPE Current State: y(n) Outputs: z Next State: y(n+1) 9: Secuenciales 21 Modelo general MEF (cont) ❒ Estados: y1, y2, ..., yk ❒ Inputs: x1, x2, ..., xm ❒ Outputs: z1, z2, ..., zn ❒ Función transición: FPE(yi, xj) ❒ Función de output: FS(yi) or FS(yi, xj) output logic Inputs Outputs next state logic Next State Current State Next State State Clock 0 1 2 3 4 5 9: Secuenciales 22 Maquinas Mealy vs Moore ❒ Maquinas Mealy tienden a tener menos estados ❍ outputs son diferentes en arcos (n2) no en estados (n) ❒ Maquinas Moore ❍ outputs cambian durante cambios del reloj (siempre un ciclo mas tarde) ❍ en maquinas Mealy, input puede causar cambios en autput de inmediato cuando cambia input – puede causar problemas cuando se conectan multiples maquinas ❒ Maquinas Mealy reaccionan mas rápido ❍ reaccionan con el input– no tienen que esperar el reloj en algunos casos ❍ en maquinas Moore – mas logica puede ser necesaria para decodificar estado en outputs 9: Secuenciales 23 Comparar maquinas Mealy y Moore (cont) inputs ❒ Moore: z = F(y) combinational logic for next state reg logic for outputs outputs state feedback inputs logic for outputs combinational logic for next state ❒ Mealy: z = F(y, x) outputs reg state feedback inputs ❒ Mealy Sincrónica logic for outputs combinational logic for next state outputs reg z = F(y, x) con FF en salida state feedback 9: Secuenciales 24 Especificar outputs para maquina Moore ❒ Output es solo una función del estado ❍ ❍ se especifica en nodos del diagrama de estado Ejemplo: detector de secuencia para 01 o 10 0 1 B/0 D/1 0 reset 0 1 A/0 0 1 1 C/0 1 0 E/1 reset 1 0 0 0 0 0 0 0 0 0 0 input – 0 1 0 1 0 1 0 1 0 1 current state – A A B B C C D D E E next state A B C B D E C E C B D output 0 0 0 0 0 0 1 1 1 1 9: Secuenciales 25 Especificar outputs para maquina Mealy ❒ Output es función de estados e inputs ❍ ❍ especificar output en transición entre estados Ejemplo: Detector de secuencia para 01 o 10 0/0 B 0/0 reset/0 0/1 A 1/1 1/0 reset 1 0 0 0 0 0 0 input – 0 1 0 1 0 1 current state – A A B B C C next state A B C B C B C output 0 0 0 0 1 1 0 C 1/0 9: Secuenciales 26 Maquina Mealy ❒ Maquina Mealy Sincrónica ❍ estados y outputs con registros ❍ evita outputs con ruidos (‘glitches’) ❍ típicamente se implementa en PLDs Inputs output logic Outputs next state logic Current State 9: Secuenciales 27 Ejemplo: maquinas de bebidas ❒ Entrega bebida después que 150 pesos son depositados ❒ Acepta diferentes monedas 50 (N), 100 (D) ❒ No entrega cambio Reset N Coin Sensor D Vending Machine FSM Open Release Mechanism Clock 9: Secuenciales 28 Ejemplo: maquinas de bebidas (cont) ❒ Representación abstracta ❍ listar secuencias típicas: • • • • ❍ Reset tres de cincuenta cincuenta, cien cien, cincuenta dos de cien S0 N S1 dibujar diagrama de estados: • inputs: N, D, reset • output: dar bebida (OPEN) ❍ asumir: D N S3 N S7 [open] • N y D seteadas por un ciclo • cada estado tiene un auto estado para N = D = 0 (no hay moneda) S2 D N S4 [open] S5 [open] D S6 [open] D S8 [open] 9: Secuenciales 29 Ejemplo: maquinas de bebidas (cont) ❒ Minimizar numero de estados – reusar estados si es posible present state 0 Reset 0 50 N 50 N D D 100 100 N+D 150 [open] 150 inputs D N 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 – – next state 0 50 100 – 50 100 150 – 100 150 150 – 150 output open 0 0 0 – 0 0 0 – 0 0 0 – 1 tabla de estados simbólica 9: Secuenciales 30 Ejemplo: maquinas de bebidas (cont) ❒ Codificar estados present state inputs Q1 Q0 D N 0 0 0 0 0 1 1 0 1 1 0 1 0 0 0 1 1 0 1 1 1 0 0 0 0 1 1 0 1 1 1 1 – – next D1 0 0 1 – 0 1 1 – 1 1 1 – 1 state D0 0 1 0 – 1 0 1 – 0 1 1 – 1 output open 0 0 0 – 0 0 0 – 0 0 0 – 1 9: Secuenciales 31 Ejemplo: Implementación Moore ❒ Mapear la lógica Q1 D1 0 0 1 1 0 1 1 1 D X X 1 X Q1 D0 Q1 Open 0 0 1 0 0 1 1 0 1 0 1 1 N D X X 1 X 0 0 1 0 N D X X 1 X 1 1 1 1 0 1 1 1 0 0 1 0 Q0 Q0 Q0 N D1 = Q1 + D + Q0 N D0 = Q0’ N + Q0 N’ + Q1 N + Q1 D OPEN = Q1 Q0 9: Secuenciales 32 Ejemplo: Implementación Moore (cont) ❒ Otra codificación (1 encendido) present state Q3 Q2 Q1 Q0 0 0 0 1 0 0 0 1 1 0 1 0 0 0 0 0 inputs D N 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 - - next state D3 D2 D1 0 0 0 0 0 1 0 1 0 - - 0 0 1 0 1 0 1 0 0 - - 0 1 0 1 0 0 1 0 0 - - 1 0 0 output D0 open 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 D0 = Q0 D’ N’ D1 = Q0 N + Q1 D’ N’ D2 = Q0 D + Q1 N + Q2 D’ N’ D3 = Q1 D + Q2 D + Q2 N + Q3 OPEN = Q3 9: Secuenciales 33 Diagramas de Estados de Mealy y Moore ❒ Moore ❍ outputs asociados con estados N’ D’ + Reset Reset 0 [0] ❒ Mealy ❍ outputs asociados con transiciones 0 N’ D’ N D 50 [0] 100 [0] N’ D’ D/0 50 N’ D’/0 100 N’ D’/0 150 Reset’/1 N/0 N’ D’ N+D 150 [1] N’ D’/0 N/0 N D (N’ D’ + Reset)/0 Reset/0 D/1 N+D/1 Reset’ 9: Secuenciales 34 Ejemplo: Implementación Mealy Reset/0 Reset/0 0 present state inputs Q1 Q0 D N 0 0 0 0 0 1 1 0 1 1 0 1 0 0 0 1 1 0 1 1 1 0 0 0 0 1 1 0 1 1 1 1 – – N’ D’/0 N/0 D/0 50 N’ D’/0 100 N’ D’/0 150 Reset’/1 N/0 D/1 N+D/1 Q1 Open 0 0 1 0 0 0 1 1 D X X 1 X 0 1 1 1 Q0 N D0 D1 OPEN next state D1 D0 0 0 0 1 1 0 – – 0 1 1 0 1 1 – – 1 0 1 1 1 1 – – 1 1 output open 0 0 0 – 0 0 1 – 0 1 1 – 1 = Q0’N + Q0N’ + Q1N + Q1D = Q1 + D + Q0N = Q1Q0 + Q1N + Q1D + Q0D 9: Secuenciales 35 Ejemplo: Implementación Mealy (cont) D0 = Q0’N + Q0N’ + Q1N + Q1D D1 = Q1 + D + Q0N OPEN = Q1Q0 + Q1N + Q1D + Q0D hay que asegurar que OPEN es 0 cuando hay reset – con compuerta AND 9: Secuenciales 36 Actividad ❒ Implementar detector de secuencia (usando Mealy) para 010 o 110 (detector no continuo, requiere secuencia completa) 0/0 0/0 S3 0/0 S1 1/0 S0 0/0 S4 S5 0/1 Next State Present State X=0 X=1 Output X=0 X=1 Reset 0 1 00 01 10 11 S0 S1 S2 S3 S4 S5 S6 0 0 0 0 1 0 1 S1 S3 S5 S0 S0 S0 S0 S2 S4 S6 S0 S0 S0 S0 0 0 0 0 0 0 0 1/0 1/0 1/0 Input Sequence 0/0 S2 1/0 1/0 S6 1/0 0/1 9: Secuenciales 37 Actividad (cont) Input Sequence Next State Present State X=0 X=1 Output X=0 X=1 Reset 0 1 00 01 10 11 S0 S1 S2 S3 S4 S5 S6 0 0 0 0 1 0 1 S1 S3 S5 S0 S0 S0 S0 S2 S4 S6 S0 S0 S0 S0 0 0 0 0 0 0 0 S1 es equivalente a S2 S3 es equivalente a S5 S4 es equivalente a S6 9: Secuenciales 38 MEF Minimizada ❒ Detector de secuencia de 010 o 110 minimizada para estados (detecta secuencia completa) Input Sequence Next State Present State X=0 X=1 Output X=0 X=1 Reset 0+1 X0 X1 S0 S1' S3' S4' 0 0 0 1 S1' S3' S0 S0 S1' S4' S0 S0 0 0 0 0 S0 0/0 0/0 S3 0/0 S1 1/0 S0 1/0 1/0 0/0 S4 S5 0/1 1/0 0/0 Original S2 1/0 X/0 1/0 S6 1/0 0/1 S1’ 0/0 1/0 S4’ S3’ X/0 0/1 1/0 9: Secuenciales 39 MEF Minimizada ❒ Otra solución para el detector de secuencia de 010 o 110 (detector continuo) ❒ Esta versión detecta subsecuencias como secuencias validas (e.g. 01010 se detectaría como dos secuencias) 1 2 1/0 -/0 S0 1/0 S1’ 0/0 S3’ 0/1 9: Secuenciales 40 9-Sistemas Secuenciales 9.1 Maquinas de Estados Finitos 9.2 Mealy y Moore FSMs 9.3 Implementación en Verilog 9: Secuenciales 41 HDL y Lógica Secuencial ❒ Flip-flops ❍ usan relojes (clocks) – tiempos de cambio de estados ❒ FSMs ❍ vista estructural (FFs separados de lógica combinacional) ❍ vista de comportamiento (síntesis de secuenciadores) ❒ Rutas de datos (e.g., ALUs, comparadores) + registros ❍ ❍ uso de operadores aritméticos/lógicos control de elementos de almacenamiento 9: Secuenciales 42 Ejemplo: reducir string de 1s en 1 ❒ Eliminar un 1 de cada string de 1s en el input Moore Mealy zero [0] 1 0 0 0 0/0 one1 [0] 1 zero [0] 1 0/0 1/0 one1 [0] 1/1 two1s [1] 9: Secuenciales 43 Ejemplo: reducir string de 1s en 1 ❒ Verilog: Maquina de Moore asignar estados module reduce (clk, reset, in, out); input clk, reset, in; output out; parameter zero = 2’b00; parameter one1 = 2’b01; parameter two1s = 2’b10; reg out; reg [2:1] state; reg [2:1] next_state; zero [0] // state variables 1 0 always @(posedge clk) if (reset) state = zero; else state = next_state; 0 0 one1 [0] 1 1 two1s [1] 9: Secuenciales 44 Ejemplo: reducir string de 1s en 1 (cont) always @(in or state) case (state) zero: // last input was a zero begin if (in) next_state = one1; else next_state = zero; end one1: // we've seen one 1 begin if (in) next_state = two1s; else next_state = zero; end two1s: // we've seen at least 2 ones begin if (in) next_state = two1s; else next_state = zero; end endcase hay que incluir todas las señales que son determinan el estado el output solo depende del estado always @(state) case (state) zero: out = 0; one1: out = 0; two1s: out = 1; endcase endmodule 9: Secuenciales 45 Verilog para MEF Mealy module reduce (clk, reset, in, out); input clk, reset, in; output out; reg out; reg state; // state variables reg next_state; always @(posedge clk) if (reset) state = zero; else state = next_state; always @(in or state) case (state) zero: // last input was a zero begin out = 0; if (in) next_state = one; else next_state = zero; end one: // we've seen one 1 if (in) begin next_state = one; out = 1; end else begin next_state = zero; out = 0; end endcase endmodule zero [0] 0/0 0/0 1/0 one1 [0] 1/1 9: Secuenciales 46 Verilog para MEF Mealy (otra versión) module reduce (clk, reset, in, out); input clk, reset, in; output out; reg out; reg state; // state variables always @(posedge clk) if (reset) state = zero; else case (state) zero: // last input was a zero begin out = 0; if (in) state = one; else state = zero; end one: // we've seen one 1 if (in) begin state = one; out = 1; end else begin state = zero; out = 0; end endcase endmodule zero [0] 0/0 0/0 1/0 one1 [0] 1/1 9: Secuenciales 47 Resumen MEFs ❒ Modelos para representar circuitos secuenciales ❍ ❍ ❍ abstracción de elementos secuenciales maquinas de estados finitos y diagramas de estados Mealy, Moore y maquinas sincrónicas Mealy ❒ Procedimiento de diseño usando MEFs ❍ ❍ ❍ ❍ generar diagrama de estados generar tabla de transiciones de estados determinar funciones de próximo estado y output implementar lógica combinacional ❒ HDLs 9: Secuenciales 48