Introducción - Digital III - Universidad Nacional de Rosario

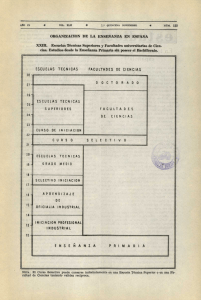

Anuncio

Digital III Módulo 1: Presentación del curso e introducción al diseño de sistemas de microcómputo. Escuela de Ingenierı́a Electrónica Facultad de Ciencias Exactas Ingenierı́a y Agrimensura Universidad Nacional de Rosario Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunas caracterı́sticas de la asignatura Es absolutamente necesaria la correlatividad con Informática II y Digital II. Clases: • Asistir !! (no hay libros de todos los temas) • La mayoría de las clases no son expositivas • Lunes de 20:30 a 23 y miércoles de 19:30 a 23:00 • Las actividades son grupales • Es importante "llevar la materia al día" Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunas caracterı́sticas de la asignatura Se encuentra organizada en cuatro módulos temáticos • Arquitectura de sistemas de microcómputo • Interrupciones e interfaces de Entrada/Salida • Software en sistemas dedicados • Autómatas en VHDL El cursado se compone de ciclos de afianzamiento teórico, realización de trabajos prácticos y la resolución de problemas de ingenierı́a. Estas últimas actividades tienen un carácter integrador, ya que completan o perfeccionan la actividad del módulo anterior. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Evaluación Se presentará un informe la clase siguiente a la última clase de resolución de cada trabajo práctico o problema de ingenierı́a. Dos exámenes parciales teórico prácticos. Cada uno evalúa los conocimientos y habilidades adquiridas durante el desarrollo de dos módulos. Examen Final • Promovido: Examen teórico de los contenidos no evaluados en parciales. • CI: Examen teórico práctico escrito integrador de todos los contenidos del año. • Libre: Rinde el mismo examen de CI. Luego, será evaluado sobre los PI o TP desarrollados el último año de cursado. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Bibliografı́a Los microprocesadores INTEL Barry B. Bray - ISBN: 968-880481-9 Introducción al microprocesador 8086/8088 C. Morgan - ISBN: 968-451-628-2 Página de la asignatura: www.eie.fceia.unr.edu.ar/digital3 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Modulo 1: Introducción a los sistemas de microcómputo Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Modulo 1: Introducción a los sistemas de microcómputo Estudiaremos sistemas embebidos que no poseen sistema operativo. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Modulo 1: Introducción a los sistemas de microcómputo Estudiaremos sistemas embebidos que no poseen sistema operativo. Estos sistemas embebidos microprocesadores. serán implementados con Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Modulo 1: Introducción a los sistemas de microcómputo Estudiaremos sistemas embebidos que no poseen sistema operativo. Estos sistemas embebidos microprocesadores. serán implementados con El microprocesador elegido es el 8086 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El módulo 1 incluye: Un breve repaso acerca de microprocesadores El procesador 8086 • Terminales y sus funciones • Modelo de ejecución • Modelo de memoria • Modos de direccionamiento • Conexión fı́sica de la memoria • Temporización de los buses • Circuito para funcionamiento en modo mı́nimo Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Arquitectura de Von Neumann Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Arquitectura de Von Neumann El modelo de ejecución es muy simple: Buscar en la memoria la primera instrucción. Ejecutarla en la unidad aritmético-lógica. Buscar en la memoria la siguiente instrucción ... Continuar ası́ hasta encontrar una instrucción de finalización del programa o una instrucción de salto Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit A simple view of the instruction cycle: Modelo de ejecución Fetch instruction Execute instruction Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit n The Instruction Cycle (cont’d) con ás cycle: de detalle... A refinedalgo view of them instruction Fetch instruction Decode Fetch operand Execute instruction Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Microprocesador Es un concepto tecnológico. Nace cuando se incluye la unidad de control, la ALU y algunos registros dentro de un único circuito integrado. Recientemente aparece el concepto de microcontrolador, donde también la memoria se integra dentro del mismo chip. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit System Bus Main Memory CPU Microprocesador System Bus Address Bus Control Unit IR PC Data Bus ALU Control Bus Registers CPU Internal CPU Bus La unidad de control es la encargada de hacer ejecutar las instrucciones Petru Eles, IDA, LiTH Petru Eles, IDA, Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Datorarkitektur Fö 1 - 23 Datorarkit Unidad de control The Control Unit (cont’d) Genera la secuencia de señales de control que permiten realizar las distintas operaciones elementales de cada instrucción Status&Cond. Flags IR Control signals internal to the CPU Control unit Control signals on system bus Signals from system bus Clock • • Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Unidad aritmético-lógica A+B A Registers B A B ALU input register ALU input bus ALU A+B ALU output register Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta Fig. 2-2. The data path of a typical von Neumann machine. •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Microprocesador actual Addressing Data Bus control Bus arbitration Coprocessor Typical MicroProcessor Status Interrupts Symbol for clock signal Miscellaneous Φ +5v Symbol for electrical ground Power is 5volts Figure 3-33. The logical pinout of a generic CPU. The arrows indicate input signals and output signals. The short diagonal lines indicate that multiple pins are used. For a specific CPU, a number- Slides will bedel given to tell how many. Curso 2010 de Digital III, FCEyA Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Responde a la arquitectura de Von Neumann y su modelo de ejecución es reg-reg y reg-mem. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Responde a la arquitectura de Von Neumann y su modelo de ejecución es reg-reg y reg-mem. Los registros internos visibles al programador son de uso especı́fico. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Responde a la arquitectura de Von Neumann y su modelo de ejecución es reg-reg y reg-mem. Los registros internos visibles al programador son de uso especı́fico. Es un microprocesador de 16 bits. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Responde a la arquitectura de Von Neumann y su modelo de ejecución es reg-reg y reg-mem. Los registros internos visibles al programador son de uso especı́fico. Es un microprocesador de 16 bits. El bus de datos es de 16 bits. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Responde a la arquitectura de Von Neumann y su modelo de ejecución es reg-reg y reg-mem. Los registros internos visibles al programador son de uso especı́fico. Es un microprocesador de 16 bits. El bus de datos es de 16 bits. El bus de direcciones es de 20 bits, capaz de direccionar 1MByte de memoria. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Responde a la arquitectura de Von Neumann y su modelo de ejecución es reg-reg y reg-mem. Los registros internos visibles al programador son de uso especı́fico. Es un microprocesador de 16 bits. El bus de datos es de 16 bits. El bus de direcciones es de 20 bits, capaz de direccionar 1MByte de memoria. Los espacios de direcciones para memoria y E/S son distintos y accesibles con instrucciones diferentes. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 Responde a la arquitectura de Von Neumann y su modelo de ejecución es reg-reg y reg-mem. Los registros internos visibles al programador son de uso especı́fico. Es un microprocesador de 16 bits. El bus de datos es de 16 bits. El bus de direcciones es de 20 bits, capaz de direccionar 1MByte de memoria. Los espacios de direcciones para memoria y E/S son distintos y accesibles con instrucciones diferentes. La era de la computadoras personales comenzó con el 8086 e inició la familia x86. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El procesador 8086 80C86 Pinouts 80C86 (DIP) TOP VIEW GND 1 MAX 40 VCC (MIN) AD14 2 39 AD15 AD13 3 38 A16/S3 AD12 4 37 A17/S4 AD11 5 36 A18/S5 AD10 6 35 A19/S6 AD9 7 34 BHE/S7 AD8 8 33 MN/MX AD7 9 32 RD AD6 10 31 RQ/GT0 (HOLD) AD5 11 30 RQ/GT1 (HLDA) AD4 12 29 LOCK (WR) AD3 13 28 S2 (M/IO) AD2 14 27 S1 (DT/R)) AD1 15 26 S0 (DEN) AD0 16 25 QS0 (ALE) NMI 17 24 QS1 (INTA) INTR 18 23 TEST CLK 19 22 READY GND 20 21 RESET 80C86 (PLCC, CLCC) TOP VIEW 17/S4 18/S5 D15 16/S3 NC VCC D14 GND D13 D12 D11 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit will not be honored until the end of the the second bus cycle, a byte is supplied 82C59A Interrupt Controller, which idene) of the interrupt. This byte is multiplied a pointer into the interrupt vector lookup l left HIGH will be continually responded ns of the enable bit and sample period. ETURN instruction includes a FLAGS he status of the original interrupt enable he FLAGS. executing a WAIT instruction. The single WAIT instruction is repeatedly executed until the TEST input goes active (LOW). The execution of WAIT does not consume bus cycles once the queue is full. If a local bus request occurs during WAIT execution, the 80C86 three-states all output drivers while inputs and I/O pins are held at valid logic levels by internal bus-hold circuits. If interrupts are enabled, the 80C86 will recognize interrupts and process them when it regains control of the bus. The WAIT instruction is then refetched, and re-executed. Registros visibles al programador T3 T4 TI T1 T2 T3 TABLE 4. 80C86 REGISTER T4 AX AH AL ACCUMULATOR BX BH BL BASE CX CH CL COUNT DX DH DL DATA TYPE VECTOR RRUPT ACKNOWLEDGE SEQUENCE SP STACK POINTER BP BASE POINTER SI SOURCE INDEX DI DESTINATION INDEX INSTRUCTION POINTER IP FLAGSH FLAGSL STATUS FLAG ALT” instruction is executed the process entering the “HALT” state in one of two CODE SEGMENT CS on which mode is strapped. In minimum r issues one ALE with no qualifying bus DS DATA SEGMENT maximum mode the processor issues SS STACK SEGMENT atus on S2, S1, S0 and the 82C88 bus ES EXTRA SEGMENT e ALE. The 80C86 will not leave the a local bus “hold” is entered while in , the processor reissues the HALT indi- Basic System Timing the local bus hold. An NMI or interrupt upts enabled) or RESET will force the Typical system configurations for the processor operating in minimum mode and in maximum mode are shown in Figures ALT” state. 6A- and 6B,del respectively. In minimum mode, MN/MX Curso 2010 de Digital III, FCEyA Slides Módulo 1 correspondientes a lathe clase del depin 8 de marzo- Santiago Roatta is strapped to VCC and the processor emits bus control sig- Write (Semaphore) •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Registros extendidos D-4 Appendix D An Alternative to RISC: The Intel 80x86 ■ 80 x386, 80x486, Pentium 80 x86, 80 x286 31 15 8 7 0 GPR 0 EAX AX AH AL Accumulator GPR 1 ECX CX CH CL Count reg: string, loop GPR 2 EDX DX DH DL Data reg: multiply, divide GPR 3 EBX BX BH BL GPR 4 ESP SP Stack ptr. Base ptr. (for base of stack seg.) Base addr. reg GPR 5 EBP BP GPR 6 ESI SI Index reg, string source ptr. GPR 7 EDI DI Index reg, string dest. ptr. PC CS Code segment ptr. SS Stack segment ptr. (top of stack) DS Data segment ptr. ES Extra data segment ptr. FS Data segment ptr. 2 GS Data segment ptr. 3 IP Instruction ptr. (PC) EIP EFLAGS FLAGS Condition codes 79 0 FPR 0 FPR 1 FPR 2 FPR 3 FPR 4 FPR 5 FPR 6 FPR 7 15 Status 0 Top of FP stack, FP condition codes Figure D.1 The 80x86 has evolved over time, and so has its register set. The original set is shown in black, and the extended set in gray. The 8086 divided the first four registers in half so that they could be used either as one 16-bit register or as two 8-bit registers. Starting with the 80386, the top eight registers were extended to 32 bits and could also be used as general-purpose registers. The floating-point registers on the bottom are 80 bits wide, and although they look like regular registers they are not. They implement a stack, with the top of stack pointed to by the status register. One operand must be the top of stack, and the other can be any of the other seven registers below the top Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Ejemplo de circuito con 8086 Bus Latching and Buffering 8086 HARDWARE OUT In M/IO M/IO RD WR ’244 RD WR OE OUT D ’373 Q In BHE/S7 A19 /S6 -A16 /S3 4 8 AD15 -AD8 BHE A19 -A16 4 G OE OUT D ’373 Q In G 8 A15 -A8 OE OUT D ’373 Q In 8 AD7 -AD0 G 8 A7 -A0 OE ALE OUT D ’245 Q In 8086 G 8 D15 -D8 DIR OUT D ’245 Q In G 8 D7 -D0 DIR DEN DT/R Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •Prev •Next •Last Figure 8: A fully•First buffered 8086 •Go Back •Full Screen •Close •Quit ¿Cómo se accede a la memoria? Real mode (8086) (80286) Logical address Logical address Segment Offset 16 12 Segment 4 Offs 16 16 24 20 Physical address Segmentation 24 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta Physical address •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit ption 80C86 ¿Cómo se accede a la memoria? code, data, extra and stack segments of up to 64K bytes each, with each segment falling on 16-byte boundaries. (See Figure 1). static design. Internal registers, static and require no refresh as gn. This eliminates the minimum tion placed on other microprocesan operate from DC to the specit. The processor clock may be IGH/LOW) and held there indefion is especially useful for system lications. tepped using only the CPU clock. ed as long as is necessary. Single s simple interface circuitry to probringing up your system. s very low frequency operation critical situation, this can provide ation since 80C86 power dissipaperating frequency. As the system is the operating power until, ultiuency, the 80C86 power requiret, (500µA maximum). FFFFFH 64K-BIT CODE SEGMENT XXXXOH STACK SEGMENT + OFFSET SEGMENT REGISTER FILE CS DATA SEGMENT SS DS ES EXTRA SEGMENT 00000H FIGURE 1. 80C86 MEMORY ORGANIZATION the 80C86 processor are partiocessing units. The first is the Bus TABLE 1. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta he second is the Execution Unit •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit TYPE OF DEFAULT ALTERNATE ng up your system. CS low frequency operation l situation, this can provide ince 80C86 power dissipag frequency. As the system operating power until, ultithe 80C86 power requireµA maximum). SS DS ES EXTRA SEGMENT 00000H ¿Cómo se accede a la memoria? 0C86 processor are parting units. The first is the Bus cond is the Execution Unit onal diagram. but for the most part perform ational processors. The bus tions related to instruction etch and store, and address s the basic bus control. The provided by this unit serves nce through improved bus es of the instruction stream ecoding and execution. FIGURE 1. 80C86 MEMORY ORGANIZATION TABLE 1. TYPE OF MEMORY REFERENCE DEFAULT SEGMENT BASE ALTERNATE SEGMENT BASE Instruction Fetch CS None IP Stack Operation SS None SP Variable (except following) DS CS, ES, SS Effective Address String Source DS CS, ES, SS SI String Destination ES None DI OFFSET mechanism allows the BIU BP Used As Base SS CS, DS, ES Effective Register Address efficiently. Whenever there queue, the BlU will attempt greatly reduces “dead-time” All memory references are made relative to base addresses acts as a First-In-First-Out contained in high speed segment registers. The segment U extracts instruction bytes types were chosen based on the addressing needs of proempty (following a branch grams. The segment register to be selected is automatically byte into the queue imme- chosen according to the specific rules of Table 1. All information in one segment type share the same logical attributes EU. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta (e.g. code or data). By structuring memory into re-locatable •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit etched instructions from the Modos de direccionamiento Un modo de direccionamiento es un procedimiento que permite determinar la ubicación de los operandos de una instrucción. Algunos modos de direccionamiento permiten escribir código reubicable y reentrante, y lograr un manejo eficiente de estructuras de datos. Una clasificación general incluye direccionamientos inmediato, directo, indirecto y relativo. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] MOV AX,[DX] Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] MOV AX,[DX] muy mal, no existe !!! Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] MOV AX,[DX] muy mal, no existe !!! MOV [4220h],0 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] MOV AX,[DX] muy mal, no existe !!! MOV [4220h],0 ¿Un byte o una palabra?. MOV BYTE PTR [4220h],0 MOV WORD PTR [4220h],0 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] MOV AX,[DX] muy mal, no existe !!! MOV [4220h],0 ¿Un byte o una palabra?. MOV BYTE PTR [4220h],0 MOV WORD PTR [4220h],0 MOV DH,[SI+2] Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] MOV AX,[DX] muy mal, no existe !!! MOV [4220h],0 ¿Un byte o una palabra?. MOV BYTE PTR [4220h],0 MOV WORD PTR [4220h],0 MOV DH,[SI+2] MOV [BX+SI-2],CX Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Algunos ejemplos MOV AX,0 MOV AX,[0] MOV AX,[BX] MOV AX,[DX] muy mal, no existe !!! MOV [4220h],0 ¿Un byte o una palabra?. MOV BYTE PTR [4220h],0 MOV WORD PTR [4220h],0 MOV DH,[SI+2] MOV [BX+SI-2],CX MOV ES:[DI],AL Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Modos de direccionamiento del 8086 Direccionamiento por registro: MOV CX,DX Direccionamiento inmediato: MOV AL,22H Direccionamiento directo: MOV CX,LIST Direccionamiento indirecto por registro: MOV AX,[BX] Direccionamiento base e ı́ndice: MOV[BX+DI],CL Direccionamiento relativo por registro: MOV AX,[BX+4] Direccionamiento relativo base más ı́ndice: MOV AX,[BX+DI+4] Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit ¿Qué significa mapear un dispositivo? Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit ¿Qué significa mapear un dispositivo? El mapeo de un dispositivo de memoria o E/S consiste en asignarle un rango de direcciones dentro del mapa de memoria o Entrada/Salida donde se pueda acceder a sus registros internos. La arquitectura Intel posee mapas de memoria y E/S separados El Mapa de Memoria es el vı́nculo entre el software y el hardware. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit La memoria fı́sica del procesador 8086 Está organizada en dos bancos para permitir la transferencia de 8 bits o 16 bits. El banco alto o impar corresponde a las direcciones terminadas en uno, y el banco bajo o par a las terminadas en cero. Para seleccionar uno o ambos bancos se emplean la señal BHO y el bit de dirección A0. Es necesario producir señales de escritura separada para cada banco de memoria. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit RAM HM62256 (32K x 8) Direcciones (A0 a A14). Datos (D0 a D7). CS, OE, WR, Vcc.. Es necesario compatibilizar los requerimientos de temporización del procesador y de la memoria. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit RAM HM62256 (32K x 8) Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Circuito (modo mı́nimo) 80C86 VCC VCC MN/MX M/IO INTA 82C8A/85 CLOCK GENERATOR CLK READY RES RD WR RESET RDY DT/R DEN GND WAIT STATE GENERATOR ALE 80C86 CPU GND 1 VCC C1 20 STB GND AD0-AD15 A16-A19 GND OE ADDR ADDR/DATA 82C82 LATCH 2 OR 3 BHE C2 40 C1 = C2 = 0.1µF VCC T OE 82C86 TRANSCEIVER (2) DATA A0 BHE OPTIONAL FOR INCREASED DATA BUS DRIVE EH EL W G HM-6516 CMOS RAM 2K x 8 2K x 8 E G HM-6616 CMOS PROM (2) 2K x 8 2K x 8 CS RD WR CMOS 82CXX PERIPHERALS FIGURE 6A. MINIMUM MODE 80C86 TYPICAL CONFIGURATION Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta VCC •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit OE 82C86 TRANSCEIVER (2) C1 = C2 = 0.1µF DATA A0 BHE OPTIONAL FOR INCREASED DATA BUS DRIVE EH EL W G HM-6516 CMOS RAM 2K x 8 2K x 8 E G HM-6616 CMOS PROM (2) 2K x 8 2K x 8 CS RD WR CMOS 82CXX PERIPHERALS Circuito (modo máximo) FIGURE 6A. MINIMUM MODE 80C86 TYPICAL CONFIGURATION VCC GND MN/MX CLK S0 READY S1 RESET S2 82C84A/85 CLOCK GENERATOR/ RES RDY 80C86 CPU GND LOCK WAIT STATE GENERATOR MRDC NC NC NC STB GND 1 VCC CLK MWTC S0 82C88 S1 BUS AMWC S2 CTRLR IORC IOWC DEN DT/R AIOWC ALE INTA C1 GND AD0-AD15 A16-A19 BHE 20 ADDR/DATA OE ADDR 82C82 (2 OR 3) GND C2 40 C1 = C2 = 0.1µF VCC T OE DATA 82C86 TRANSCEIVER (2) A0 BHE EH EL W G HM-65162 CMOS RAM 2K x 8 2K x 8 E G HM-6616 CMOS PROM (2) 2K x 8 2K x 8 CS RDWR CMOS 82CXX PERIPHERALS FIGURE 6B. MAXIMUM MODE 80C86 TYPICAL CONFIGURATION Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta 3-155 •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit La temporización de bus Cada ciclo de bus ocupa cuatro ciclos de reloj: T1, T2, T3, T4. A 5MHz cada T-state dura 200 nseg, y el ciclo de bus ocupa 800 nseg. Es un bus semi-sı́ncrono, y permite insertar estados de espera denominados Twaits para acceder a memorias o dispositivos de E/S lentos. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit 8086 HARDWARE Ciclo de lectura (simplificado) Bus Timing ONE BUS CYCLE T1 T2 T3 T4 CLK ADDRESS /DATA ALE RD Figure 6: Read Cycle Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit 8086 HARDWARE Ciclo de escritura (simplificado) Bus Timing ONE BUS CYCLE T1 T2 T3 T4 CLK ADDRESS /DATA ALE WR Figure 5: Write Cycle Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Ciclo de bus Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Ciclo de bus T1: Address, ALE, DT/R, M/IO. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Ciclo de bus T1: Address, ALE, DT/R, M/IO. T2: DEN, y RD o WR y los datos en el bus. Al final de T2 se muestrea READY Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Ciclo de bus T1: Address, ALE, DT/R, M/IO. T2: DEN, y RD o WR y los datos en el bus. Al final de T2 se muestrea READY T3: Si es un ciclo de lectura, el bus de datos se muestrea al finalizar T3 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Ciclo de bus T1: Address, ALE, DT/R, M/IO. T2: DEN, y RD o WR y los datos en el bus. Al final de T2 se muestrea READY T3: Si es un ciclo de lectura, el bus de datos se muestrea al finalizar T3 T4: Si es un ciclo de escritura, los datos se transfieren en el flanco de subida de WR. Además, se desactivan todas las señales en preparación para el ciclo siguiente. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit Temporización del bus 80C86 (4 + NWAIT) = TCY T1 T2 T3 (4 + NWAIT) = TCY TWAIT T4 T1 T2 T3 TWAIT T4 CLK GOES INACTIVE IN THE STATE JUST PRIOR TO T4 ALE S2-S0 ADDR/ STATUS BHE, A19-A16 BHE A19-A16 S7-S3 S7-S3 BUS RESERVED FOR DATA IN ADDR/DATA D15-D0 VALID A15-A0 A15-A0 DATA OUT (D15-D0) RD, INTA READY READY READY WAIT WAIT DT/R DEN MEMORY ACCESS TIME WR FIGURE 3. BASIC SYSTEM TIMING Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit 80C86 Waveforms Ciclo de lectura T1 T2 T3 T4 TW (5) TCL2CL1 (1) TCLCL TCH1CH2 (4) CLK (82C84A OUTPUT) (3) (2) TCLCH TCHCL (30) TCHCTV TCHCTV (30) M/IO (17) TCLAV (17) TCLAV (26) TCLDV (18) TCLAX S7-S3 BHE, A19-A16 BHE/S7, A19/S6-A16/S3 TLHLL (22) (23) TCLLH TLLAX (25) ALE (24) TR1VCL (8) TCHLL RDY (82C84A INPUT) SEE NOTE TAVAL (39) VIH VIL TCLR1X (9) (12) TRYLCL (11) TCHRYX READY (80C86 INPUT) (19) TCLAZ AD15-AD0 (10) TRYHCH (16) TDVCL AD15-AD0 DATA IN (32) TAZRL (34) TCLRH (7) TCLDX1 TRHAV (35) RD (30) TCHCTV READ CYCLE (WR, INTA = VOH) TCLRL (33) TRLRH (37) (30) TCHCTV DT/R (29) TCVCTV TCVCTX (31) DEN FIGURE 7A. BUS TIMING - MINIMUM MODE SYSTEM NOTE: Signals at 82C84A are shown for reference only. RDY is sampled near the end of T2, T3, TW to determine if TW machine states are to be inserted. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit 80C86 Waveforms Ciclo de escritura (Continued) T1 T2 (4) TCH1CH2 T4 (5) TCL2CL1 TW CLK (82C84A OUTPUT) (26) TCLDV TCLAX (17) TCLAV TCVCTV (27) TCLDX2 (18) AD15-AD0 AD15-AD0 WRITE CYCLE TW T3 DATA OUT TWHDX (29) (28) (31) TCVCTX DEN (RD, INTA, DT/R = VOH) (29) TCVCTV (38) TWLWH WR TCVCTX TDVCL (19) TCLAZ (31) (6) TCLDX1 (7) POINTER AD15-AD0 TCHCTV (30) TCHCTV (30) DT/R INTA CYCLE (SEE NOTE) (RD, WR = VOH BHE = VOL) (29) TCVCTV INTA (29) TCVCTV TCVCTX (31) DEN SOFTWARE HALT DEN, RD, WR, INTA = VOH INVALID ADDRESS AD15-AD0 SOFTWARE HALT TCLAV (17) DT/R = INDETERMINATE FIGURE 7B. BUS TIMING - MINIMUM MODE SYSTEM NOTE: Two INTA cycles run back-to-back. The 80C86 local ADDR/DATA bus is floating during both INTA cycles. Control signals are shown for the second INTA cycle. Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El 8284A 8284 X1 CLK ÷3 15MHz 8086 5MHz CLK X2 F/C Vcc CSYNC RESET 10k RESET RES 10µF To reset other devices ure 4: 8284A Clock Generator (6th ed, §9.2, pp 314-317). Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit El 8284A Bus Timing 8086 HARDWARE CS from memory devices X1 RDY1 ÷3 15MHz Vcc X2 8284A 10k 10µF RES CLK RESET QAQBQCQDQEQFQGQH 74LS164 CLR SI READY Vcc READY RESET CLK RD WR INTA 8086 Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta Figure 7: Wait states with the •8284A •First •Prev Next •Last •Go Back •Full Screen •Close •Quit ¿Preguntas? Curso 2010 de Digital III, FCEyA - Slides del Módulo 1 correspondientes a la clase del de 8 de marzo- Santiago Roatta •First •Prev •Next •Last •Go Back •Full Screen •Close •Quit