diseño de un demodulador fm basado en la tecnología software

Anuncio

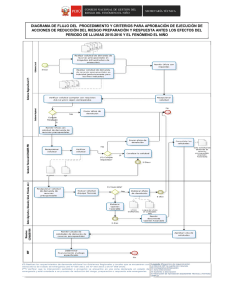

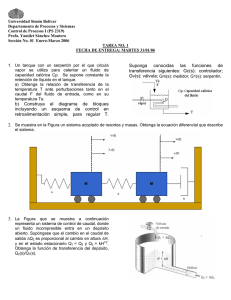

XV Workshop Iberchip, Buenos Aires - Argentina, 25 - 27 de Marzo de 2009 DISEÑO DE UN DEMODULADOR FM BASADO EN LA TECNOLOGÍA SOFTWARE-DEFINED RADIO EN FPGA José Francisco Quenta Cuno,Walter Calienes Bartra, Carlos Silva Cárdenas Grupo de Microelectrónica (GuE) – Sección de Electricidad y Electrónica (SEE) Pontificia Universidad Católica del Perú ^MITXHQWDZFDOLHQHVFVLOYD`#SXFSHGXSH Abstract— This paper describe the design of a broadband FM demodulator base on software-defined radio technology. The demodulator was implemented in a Virtex-II Pro FPGA of the Xilinx Company. I. INTRODUCCIÓN El término de Software Radio fue acuñado por Joe Mitola en 1991 para referirse a las comunicaciones de radio reconfigurables, donde el Hardware puede ser reconfigurado según la aplicación [1]. El presente trabajo muestra el diseño de un demodulador FM siguiendo la filosofía del software-defined radio (SDR). Las señales de FM comercial están presentes en los ambientes urbanos, tienen una modulación bien definida y es relativamente fácil corroborar su correcta recepción. Figura 2. Espectro radioelectrico del canal FM comercial II. En el Perú la banda de frecuencia del servicio de Radiodifusión sonora en Frecuencia Modulada [2] esta comprendida entre las frecuencias de 88 Mhz a 108 Mhz. La excursión máxima de la frecuencia portadora es igual a +/- 75 Khz, mientras que la separación entre canales es de 200 Khz [3]. La figura 1 muestra el espectro de un canal de FM comercial. DESCRIPCIÓN DEL SISTEMA Se ha implementado un demodulador FM comercial basado en la tecnología SDR. La figura 3 muestra el diagrama del sistema completo donde se implementaría el demodulador de FM. Figura 3. Diagrama del receptor basado en SDR A. Diagrama de bloques La figura 4 muestra el diagrama de bloques del demodulador FM implementado sobre una FPGA Virtex-II Pro. Se trata de un sistema que incluye un muestreo pasa banda, un mezclador, un generador de onda (DDS), una etapa de filtros y un demodulador [4]. Figura 1. Espectro de un canal FM Comercial La figura 2 muestra el espectro radioeléctrico del canal de FM comercial. 353 XV Workshop Iberchip, Buenos Aires - Argentina, 25 - 27 de Marzo de 2009 ! Figura 7. diagrama de bloques del DDS Inmediatamente después de realizar el corrimiento en frecuencia a través del mezclador se desea filtrar las señales IQ para reducir la tasa de muestreo y sólo mantener la información relacionada al canal deseado. Se requiere aplicar un filtrado a muestras que ingresan a una tasa de varios millones de muestras por segundo hasta llegar a una tasa del orden de los varios miles de muestras por segundo (con la consecuente reducción del ancho de banda de la señal). En el caso particular que se está analizando debe reducirse una señal de entrada con 20 [MHz] de ancho de banda, muestreada a 44 [MSPS], a una señal de salida de 17 [KHz] [5-8]. Figura 4. Diagrama del demodulador basado en SDR La señal de entrada del sistema para el cual el sistema fue diseñado, es una señal que posee un ancho de banda de 20 Mhz, que se encuentra desde los 88 Mhz hasta los 108 Mhz. Esta señal será muestreada usando el teorema Pasa-Banda. Para este caso la frecuencia de muestreo es de 44 Mhz, con el segundo armónico de esta frecuencia se logra desplazar todo el espectro del canal FM a banda base. En la figura 5 se muestra el proceso de muestreo de la señal FM a una tasa de 44 MSPS. Realizar tal reducción a través de los tradicionales filtros FIR resultaría demasiado costoso. Una alternativa mucho más eficiente para lograr grandes decimaciones es el filtraje en cascada a través de filtros de Hogenauer mas conocidos como filtros “CIC” y filtros de banda media “HBF”. La figura 8 muestra el diagrama de bloques de los filtros en cascada que se implementaron. Figura 5. Muestreo de la señal FM El DDS (Digital Direct Synthesizer) es el bloque encargado de generar las señales seno y coseno para que el mezclador seleccione el canal deseado. La figura 7 muestra el diagrama de bloques del DDS que se implemento usando la propiedad de simetría de cuarto de onda de las señales senoidales [4]. Figura 8. Diagrama de bloques de los filtros en cascada Ya dentro del sistema digital, el mezclador se encarga de realizar el desplazamiento de frecuencia (llevar la señal a banda base) mediante la descomposición en señales I-Q (in phase, quadrature phase). La figura 6 muestra el proceso de conversión a banda base luego de pasar la señal por el bloque mezclador. Hasta ahora se ha presentado la etapa de corrimiento en frecuencia y los distintos tipos de filtros que pueden emplearse para dejar en banda base la señal del canal de interés. Sin embargo, evidentemente, esto equivale tan sólo a seleccionar una porción del espectro electromagnético, pero aún no permite recuperar la información original codificada en la portadora. Para lograr esto se requiere implementar una última etapa de demodulación. Esta etapa se encarga de recuperar la información originalmente emitida. La figura 9 muestra el diagrama de bloques del demodulador basado en un conversor de coordenadas cartesianas a polares (CORDIC) y un derivador[7]. Figura 6. Proceso de conversión a banda base Figura 9. Digrama de bloques del dmodulador 354 XV Workshop Iberchip, Buenos Aires - Argentina, 25 - 27 de Marzo de 2009 importante recordar que los módulos que se diseñaron podrían ser utilizados para realizar otros tipos de demodulaciones. Estando tan sólo limitado por las capacidades de computación disponible y de la etapa de entrada RF. B. Implementacion y Simulacion El proceso de descripción se esta realizado con el programa ISE 8.1 proporcionado por la compañía Xilinx. Este programa nos permite, mediante código VHDL, implementar los distintos bloques que componen un nuestro dispositivo, permitiéndonos sintetizar el código comprobando en todo momento que este pueda funcionar en la FPGA. Además el programa permite ver el costo de implementación que van a tener los distintos bloques del demodulador a la hora de consumir los recursos de la FPGA. IV. [1] [2] Para el proceso de simulación de los bloques se usará el software ModelSim XE 6.0d proporcionado por la compañía Mentor Graphics. Para la simulación del sistema completo se usara el software System Generator de la compañía Xilinx. [3] [4] La implementación se realizó en la tarjeta de desarrollo XUP Virtex-II Pro Development System. El sistema ocupo 920 Slices, 700 Flip-flops y 2 Multiplicadores embebidos. [5] [6] III. CONCLUSIONES Si bien en este trabajo se presento el diseño de un demodulador de FM comercial usando la tecnología SDR, es [7] [8] 355 REFERENCIAS T. Walter, “Software Defined Radio: Origins, Drivers and International Perspectives” Wiley. 2002 Ministerio de Transportes y Comunicaciones, Perú. “Plan Nacional de Atribución de Frecuencias (PNAF)”. Ministerio de Transportes y Comunicaciones, Perú. Normas Técnicas de Radiodifusión. HOSKING, Rodger H. “Digital Receiver Handbook: Basic of Software Radio”. 4ta. ed. New Jersey: PENTEK 2003 XILINX IPCENTER. “Cascaded Integrator-Comb Filter.” http://www.xilinx.com/ipcenter/ ALTERA LITERATURE. “Understanding CIC Compensation Filters” http://www.altera.com/literature/an/an455.pdf?GSA_pos=6&WT.oss_r= 1&WT.oss=CIC ANDRAKA CONSULTING GROUP. “DSP with FPGAs” http://www.andraka.com/dsp.htm Meyer, Uwe. “DSP with FPGAs”. 3ra. Edición, Florida: Springer. 2007