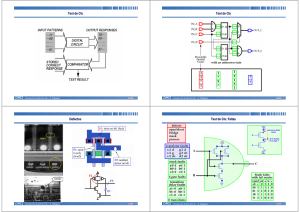

BIST: Built-in Self Test Arquitectura BIST a nivel de CI Generación

Anuncio

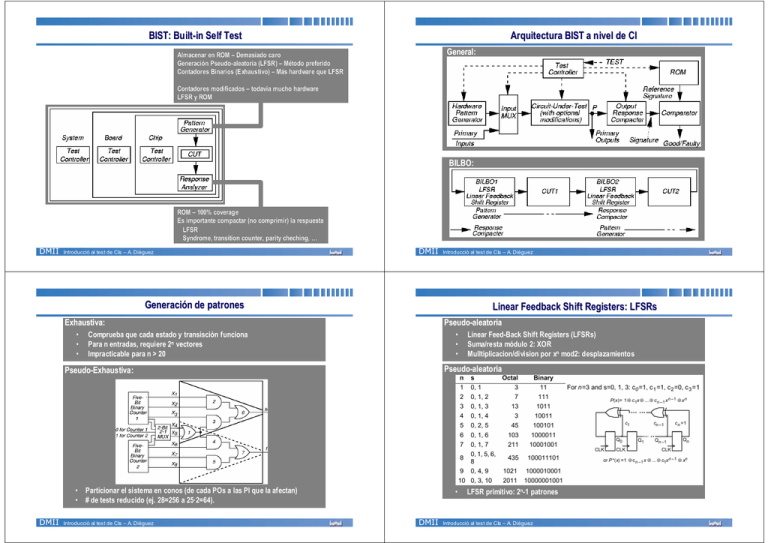

BIST: BuiltBuilt-in Self Test Arquitectura BIST a nivel de CI General: Almacenar en ROM – Demasiado caro Generació Generaci ón Pseudo Pseudo-- aleatoria (LFSR) – Método preferido Contadores Binarios (Exhaustivo Exhaustivo)) – Más hardware que LFSR Contadores modificados – todavia mucho hardware LFSR y ROM BILBO: ROM – 100% coverage Es importante compactar (no comprimir comprimir)) la respuesta LFSR Syndrome, transition counter, parity cheching cheching,, … DMII Introducció al test de CIs – A. Diéguez DMII Introducció al test de CIs – A. Diéguez Generació Generación de patrones Linear Feedback Shift Registers: LFSRs Exhaustiva:: Exhaustiva • • • Pseudo--aleatoria Pseudo Comprueba que cada estado y transisción funciona Para n entradas, requiere 2n vectores Impracticable para n > 20 • • • Pseudo--aleatoria Pseudo Pseudo--Exhaustiva Pseudo Exhaustiva:: • Particionar el sistema en conos (de cada POs a las PI que la afectan) • # de tests reducido (ej. 28=256 a 25·2=64). DMII Introducció al test de CIs – A. Diéguez Linear Feed-Back Shift Registers (LFSRs) Suma/resta módulo 2: XOR Mulltiplicacion/division por xn mod2: desplazamientos • DMII LFSR primitivo: 2n-1 patrones Introducció al test de CIs – A. Diéguez Linear Feedback Shift Registers Linear Feedback Shift Registers Cada polinomio se puede generar con 2 tipos de LFSRs (externo o interno): 1 x x2 LFSR tipo 1 (externo) x4 x3 x4 P (x) = 1 + x3 + x4 x x2 1 LFSR tipo 2 (interno) x3 Cada LFSR tiene asociados 2 polinomios (natural y recíproco): LFSR tipo 1 (externo) x4 x3 1 x2 Recíproco x P*(x) = xn·P(1/x)= 1 + x + x4 LFSR tipo 2 (interno) 1 x2 x3 x4 Recíproco x DMII Introducció al test de CIs – A. Diéguez DMII Introducció al test de CIs – A. Diéguez Linear Feedback Shift Registers: Signature LFSRs: LFSRs: Aná Análisis de firma (signature) P(x) = 1 + x + x3 + x5 Natural externo Recíproco interno P*=xn·P(1/x) Inputs Initial State 1·x7 1 0·x6 0 0·x5 0 0·x4 0 1·x3 1 0·x2 0 1·x1 1 0·x0 0 X0 0 1 0 0 0 1 1 1 1 1·x0 Resto: X1 0 0 1 0 0 0 0 1 0 0·x1 1+ X2 X3 X4 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 1 0 0 0 1 1 1 0 1·x 2 1·x3 0·x4 x2 + x3 Q(x) = x + x3 + x7 DMII Introducció al test de CIs – A. Diéguez DMII Introducció al test de CIs – A. Diéguez x5 + x3 + x + 1 x2 + 1 x7 + x3 +x x 7 + x5 + x3 + x2 x5 + x2 + x +x+1 x5 + x3 x3 + x2 +1 BIST: Aliasing Pattern abc 000 001 010 011 100 101 110 111 Transition Count LFSR Syndrome DMII Good 0 1 0 0 0 1 1 1 3 001 4 Responses a sa1 f sa1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 Signatures 3 0 101 001 6 8 Introducció al test de CIs – A. Diéguez MISR: MultipleMultiple-Input Signature Register b sa1 0 0 0 0 1 1 1 1 1 010 4 Aliasing T. Count Aliasing LFSR Aliasing Synd. DMII BuiltBuilt-in Logic Block Observer (BILBO) Introducció al test de CIs – A. Diéguez BuiltBuilt-in Logic Block Observer (BILBO) Simultáneamente: · FF D · Generador de patrones · Compactador de respuesta · Cadena de scan DMII Introducció al test de CIs – A. Diéguez DMII B1B2 = ’00’ – serial scan mode B1B2 = ’01’ – test pattern generation mode B1B2 = ’10’ – parallel load mode B1B2 = ’11’ – response compaction mode Introducció al test de CIs – A. Diéguez