PDF Full-Text

Anuncio

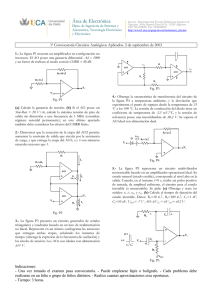

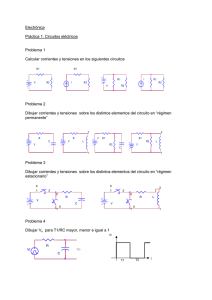

IEEE LATIN AMERICA TRANSACTIONS, VOL. 5, NO. 8, DECEMBER 2007 557 Un amplificador operacional equilibrado E. M. Spinelli, Member IEEE, y M. A. Mayosky, Senior IEEE Resumen— Se presenta un amplificador operacional completamente equilibrado, que opera sobre señales de modo común y de modo diferencial. A diferencia de los amplificadores operacionales completamente diferenciales estándar, en los cuales su comportamiento de modo común está fijado por un lazo interno, el amplificador propuesto permite analizar y diseñar tanto la respuesta de modo diferencial de un circuito como su respuesta de modo común. El dispositivo puede implementarse en forma monolítica o utilizando amplificadores operacionales estándar. Su estructura puede reconocerse en diversos circuitos completamente diferenciales (F-D: “Fully-Differential”) clásicos, lo cual permite analizarlos en un nuevo contexto, así también como diseñar nuevos circuitos de aplicación, asegurando tanto su respuesta de modo común como de modo diferencial. Se presentan algunas aplicaciones en el análisis de circuitos FD clásicos y el diseño e implementación de un oscilador F-D que oscila en modo común y en modo diferencial a dos frecuencias independientes. Palabras clave — Amplificador operacional, procesamiento analógico, amplificadores diferenciales. L I. INTRODUCCIÓN os circuitos completamente diferenciales (F-D: “FullyDifferential Circuits”) son muy utilizados actualmente por a su alta inmunidad a perturbaciones de modo común y por su mayor excursión de la señal. En efecto, un circuito FD admite, para la misma tensión de alimentación, el doble de excursión que su contraparte single-ended (S-E). Esto último es particularmente importante en equipos alimentados a baterías, donde la tensión de alimentación es un recurso escaso a preservar. Por otra parte, los circuitos F-D pueden conectarse en forma directa a los convertidores analógicos digitales actuales de alta resolución, que en su mayoría tienen entradas de tipo diferencial; resultando así circuitos de acondicionamiento simples y elegantes [1]. Existen dispositivos comerciales para la implementación de circuitos F-D como los FDOA: “Fully-Differential Operational Amplifiers” [2], pero sólo permiten implementar topologías del tipo inversor. Si se requiere un amplificador noinversor, por ejemplo para conservar una alta impedancia de Este trabajo ha sido parcialmente financiado por los subsidios CONICET PIP-5551 y ANPCyT PICT 11-14111. E. M. Spinelli trabaja en el Laboratorio de Electrónica Industrial Control e Instrumentación (LEICI), Facultad de Ingeniería, Universidad Nacional de La Plata (UNLP) y en el Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET). CC 91, (1900) La Plata, Argentina (correo e.: spinelli@ ieee.org). M. A. Mayosky pertenece al LEICI y a la Comisión de Investigaciones Científicas de la Provincia de Buenos Aires (CICPBA). entrada, se debe utilizar un FDDA: “Fully Differential Difference Amplifier”. Estos dispositivos amplifican la diferencia entre dos señales diferenciales y proporcionan una mayor flexibilidad de diseño [3,4]. Tanto el FDAO como el FDDA presentan una limitación: operan sobre señales de modo diferencial mientras que su respuesta de modo común es determinada por un lazo de realimentación interno (CMFB: “Common Mode Feedback”), el cual no es accesible para el diseñador de aplicaciones. Este lazo interno puede interactuar con la red de realimentación externa dando lugar a problemas de estabilidad [5]. El diseño de circuitos F-D se realiza usualmente partiendo de un prototipo S-E. Es decir, se diseña un circuito S-E utilizando técnicas clásicas y luego se lo transforma en F-D replicando el circuito S-E tomando el común (masa) como eje de simetría [6]. Como puede advertirse, esta estrategia contempla exclusivamente la respuesta de modo diferencial del circuito F-D, (que coincidirá con la del prototipo S-E), pero nada asegura acerca de la respuesta de modo común. Esta última puede resultar inapropiada o incluso inestable [6]. Existe un método, basado en una descripción en variables de estado, que permite diseñar tanto la respuesta de modo común como de modo diferencial de un circuito F-D [7], pero el mismo se aparta de las técnicas habitualmente utilizadas por los diseñadores de circuitos analógicos. En este trabajo se propone un método de análisis y diseño de circuitos F-D que se basa en definir un amplificador operacional equilibrado (FBOA: “Fully-Balanced Operational Amplifier”). La técnica propuesta, que contempla tanto la respuesta de modo común como de modo diferencial, permite analizar circuitos F-D existentes, así también como diseñar nuevas aplicaciones. II. EL AMPLIFICADOR OPERACIONAL EQUILIBRADO Un esquema del amplificador operacional propuesto se muestra en la Fig.1. El mismo posee dos entradas equilibradas (una inversora y otra no-inversora) y una salida equilibrada. Las tensiones de modo diferencial (MD) y de modo común (MC) en la entrada inversora se denotan como (viD-, viC-) y las correspondientes a la entrada no-inversora como (viD+, viC+). Las tensiones de salida son (voD, voC). (viD+ , viC+) (voD , voC) (viD- , viC-) Fig.1. Símbolo utilizado para representar el FBOA. 558 IEEE LATIN AMERICA TRANSACTIONS, VOL. 5, NO. 8, DECEMBER 2007 A diferencia del FDAO y del FDDA, que amplifican exclusivamente tensiones de modo diferencial, el FBOA propuesto amplifica tanto las señales de modo común como las de modo diferencial. La relación entre sus entradas y salidas están dadas por: voD = A ( viD+ − viD- ) (1) voC = A ( viC+ − viC- ) comparación, amplificación y realimentación. R1 R2 R2 R1 Un amplificador operacional está concebido para operar realimentado y su ganancia es idealmente infinita. Esto implica: viD+ = viD- (2) viC+ = viC- Es decir que el conocido concepto de “tierra virtual” puede aplicarse para ambos modos, proporcionando un camino simple para el análisis de circuitos F-D. A. Implementación del FBOA. El FBOA puede construirse como un circuito integrado dedicado, pero también puede implementarse fácilmente utilizando amplificadores operacionales convencionales (S-E) conectándolos según se muestra la Fig.2. Es simple demostrar que este circuito funciona verificando la ecuación (1). (viD+ , viC+) (voD , voC) (viD- , viC-) Fig. 2. Implementación del FBOA utilizando amplificadores operacionales convencionales. La estructura presentada en la Fig.2 puede reconocerse en diversos circuitos F-D clásicos, los cuales, como se mostrará a continuación, pueden analizarse utilizando el concepto de FBOA. III. ANÁLISIS DE CIRCUITOS F-D. El método de análisis consiste en, dado un circuito F-D, identificar los FBOA y las realimentaciones del circuito; caracterizarlas y posteriormente analizar el comportamiento para cada modo (MC y MD) por separado. Como se mostró anteriormente, el concepto de tierra virtual puede aplicarse tanto para MD como para MC, lo cual permite resolver fácilmente circuitos basados en A.O. realimentados. A. Ejemplo de análisis. En la Fig.3 (a) se presenta el conocido amplificador F-D de dos A.O. , el cual compone la etapa de entrada del aun más conocido amplificador de instrumentación de tres A.O. [1]. Este circuito puede redibujarse considerando que los dos A.O. componen un FBOA (ver Fig.2.). El circuito resultante, que se muestra en la Fig.3(b), es totalmente equivalente al primero, pero permite identificar más claramente los bloques de (a) R2 R2 (b) Fig. 3. (a) Amplificador F-D. con dos A.O. (b) Circuito equivalente utilizando un FBOA, donde pueden reconocerse claramente los bloques de comparación, amplificación y realimentación. La red de realimentación es un atenuador F-D que presenta una ganancia βD para señales de modo diferencial y una ganancia βC para señales de modo común. Las mismas están dadas por: ⎛ R1 ⎞ βD = ⎜ ⎟ ; βC = 1 ⎝ R1 + 2 R2 ⎠ (3) Se observa que esta red atenúa las tensiones de MD mientras que presenta una ganancia unitaria para tensiones de MC. Considerando que el circuito de la Fig.3.(b) corresponde a una configuración no-inversora, resultan los circuitos equivalentes para MC y MD que se indican en la Fig. 4 (a) y Fig.4 (b) respectivamente. viD voD R1/2 viC voC R2 (a) (b) Fig. 4. (a) Circuito equivalente para tensiones de modo común y (b) para tensiones de modo diferencial del circuito de la Fig.3. A partir de estos circuitos se pueden obtener las ganancias de modo cerrado de modo diferencial GDD=voD/viD y la de modo común GCC=voC/voC [1], las cuales están dadas por: GDD = 1 + 2 R2 R1 GCC = 1 (4) Un resultado no tan obvio y difícil de advertir en el circuito de la Fig. 3.(a), puede desprenderse fácilmente del circuito de MC de la Fig.4 (b): si bien la ganancia diferencial del amplificador puede ser mucho mayor que la unidad, los A.O deben se estables para ganancia unitaria; de lo contrario el circuito no será estable para tensiones de MC [8]. Este inconveniente suele presentarse frecuentemente en la implementación de amplificadores de instrumentación de gran ancho de banda. SPINELLI AND MAYOSKY : A FULLY-BALANCED OPERATIONAL AMPLIFIER IV. DISEÑO DE CIRCUITOS F-D. La técnica de diseño propuesta para circuitos F-D es similar a las habitualmente utilizadas para circuitos singleended. La misma consiste en reemplazar los A.O. por FBOA y en considerar tanto las realimentaciones de MD como las de MC. Como ejemplo de aplicación y para mostrar la posibilidad de diseñar en forma independiente la dinámica de modo común y de modo diferencial, se presenta a continuación el diseño de un oscilador. Como primer paso se diseña el oscilador S-E. En este caso se optó por un oscilador de doble integrador que se muestra en la Fig.5. Ri RG RC1 Ci Ri 559 La red de realimentación β1 presenta una ganancia β1D para tensiones de modo diferencial y una ganancia β1C para tensiones de modo común. Si se considera que los resistores RC no cargan apreciablemente al atenuador β1, las ganancias de realimentación quedan dadas por: ⎛ ⎞ RB1 β1D = ⎜ ⎟ ; β1C = 1 ⎝ RB1 + 2 RA1 ⎠ Como la ganancia de realimentación de MD es distinta a la correspondiente al MC, el circuito presentará, de acuerdo a (5), dos frecuencias de oscilación: una de modo diferencial foD y otra de modo común foC, cuyos valores son: Ci f oD = RC2 β2 f oC β1 La frecuencia de oscilación de este circuito queda determinada por la realimentación β1, al cual está dada por: (5) La segunda realimentación β2 se incluye para ubicar los polos ligeramente en el semiplano derecho para asegurar así el arranque del oscilador. El circuito de la Fig.5 no incluye control de amplitud, la cual quedará determinada por nolinealidades propias del circuito. El segundo paso consiste en reemplazar los A.O. por FBOA, y utilizar redes F-D para implementar las realimentaciones β1, β2 resultando el circuito de la Fig.6. RG Ri (7) RG RC1 = 2π RiCi Ri = 18.5kΩ ; Ci = 100nF ; RA1 = 910Ω ; (8) RB1 = 220Ω ; RA2 = 3.3kΩ ; RB2 = 3kΩ ; RC1 = 20kΩ ; RC2 = 770kΩ; FBOA: 2xLF353. RG RC1 fo = 2π RiCi β1 Ri RB1 RG RB1 + 2 RA1 RC1 2π RiCi Para este ejemplo se adoptaron: Fig.5. Oscilador single-ended de doble integración. RG (6) Ci Ri Ci Ci Ri Ci resultando: f oD ≅ 28Hz ; (9) V. RESULTADOS EXPERIMENTALES Para validar la técnica propuesta se construyó el oscilador diseñado en el punto previo y se comprobó que el mismo oscila en MC y en MD a frecuencias muy próximas a las predichas por (7). En la Fig.7 se muestran las tensiones en las salidas yH, yL del circuito y en la Fig.8 se presentan las tensiones de salida de modo común yC y de modo diferencial yD, donde se pueden observar más claramente las oscilaciones de MC y de MD. yH yL f oC ≅ 86Hz . yH (V) 0.2 0.0 RC RC RC RC -0.2 RB2 RA RA RB1 RA1 RA1 yL 0.2 0.0 β2D ; β2C β1D ; β1C Fig.6. Oscilador equilibrado que resulta de transformar el prototipo singleended de la Fig.5. Nótese la implementación F-D de los integradores. -0.2 0 10 20 30 40 50 60 Tiempo (ms) 70 80 90 100 Fig.7. Tensiones obtenidas en las salidas yH, yL del oscilador equilibrado. 560 IEEE LATIN AMERICA TRANSACTIONS, VOL. 5, NO. 8, DECEMBER 2007 yD (V) REFERENCIAS 0.3 [1] 0.0 [2] -0.3 yC (V) [3] 0.05 [4] 0.00 -0.05 0 10 20 30 40 50 60 Tiempo (ms) 70 80 90 100 [5] Fig.8. Tensiones de modo diferencial yD y de modo común yC en la salida del oscilador. [6] VI. CONCLUSIONES Definiendo un amplificador operacional equilibrado, el cual amplifica tensiones de modo común y de modo diferencial, el análisis y el diseño de circuitos completamente diferenciales puede hacerse de manera simple, de una forma muy similar a las utilizadas habitualmente para trabajar con circuitos single-ended. El método propuesto permite analizar y diseñar tanto la respuesta de modo diferencial como la de modo común. Esto permite asegurar la estabilidad del circuito, su respuesta de modo diferencial así también como una dinámica de modo común apropiada. A modo de validación, se diseñó y se evaluó experimentalmente un oscilador con salida equilibrada que presenta frecuencias de oscilación de modo común y de modo diferencial independientes entre sí. [7] [8] R. Pallas Areny and J. Webster, Analog Signal Processing, Wiley, New York, 1999. J. Karki, “Fully Differential Amplifiers,” Analog Applications Journal, Texas Instrument Incorporated, August 2000. Disponible en www.ti.com. E. Sackinger and W. Guggenbuhl, “A Versatile Building Block: The CMOS Differential Difference Amplifier,” IEEE Journal of Solid-State Circuits, Vol. 22, No.2, pp.287-294, Abril, 1987. H. Alzaher and M. Ismail, “A CMOS Fully Balanced Differential Difference Amplifier and Its Applications,” IEEE Transactions on Circuit and Systems II, Vol.48, No. 6, pp.614-620, Junio 2001. A. Tauro, C. Marzocca, C.T. Francesco and A. Di Giandomenico, “Common mode stability in fully differential voltage feedback CMOS amplifiers,” Proceedings of the 10th IEEE International Conference on Electronics, Circuits and Systems ICECS 2003, vol. 1, Sharjah, United Arab Emirates, Diciembre. 2003, pp. 288 – 291. O. Casas, and R. Pallas-Areny, “Basics of Analog Differential Filters,” IEEE Transactions on Instrumentation and Measurement, Vol. 45, No 1, pp.275-279. Feb., 1996. E. Spinelli, M. Mayosky and R. Mantz, “Independent Differential-Mode and Common-Mode Design of Fully-Differential Analog Filters,” IEEE Transactions on Circuit and Systems II. Vol. 53, No. 7, pp. 572-576. July 2006. R. White, “Phase Compensation of the Three Op Amp Instrumentation Amplifier,” IEEE Transactions on Instrumentation and Measurement, Vol. 36, No. 3, 842-844. Septiembre. 1987. Enrique Mario Spinelli (SM’98, M’2002) Nació en Balcarce, Argentina, en 1964. Recibió el título de Ingeniero en 1989, el de Magister en 2000 y su título de Doctor en 2005, todos estos estudios en la Universidad Nacional de La Plata (UNLP). Desde 1990 pertenece al Laboratorio de Electrónica Industrial Control e Instrumentación (LEICI) donde trabaja en temas de Instrumentación y Procesamiento Analógico de Señales. Actualmente es Profesor Adjunto en el Área Control en la Facultad de Ingeniería de la UNLP y es Investigador del Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET) desde 2004. Sus principales temas de interés son la Instrumentación Biomédica y el Procesamiento Analógico de Señales. Miguel Angel Mayosky (M’95, SM’98) Nació en La Plata en 1960. Recibió su título de Ingeniero en la Universidad Nacional de La Plata (UNLP) en 1983 y su título de Doctor en la Universidad Autónoma de Barcelona en 1990. Actualmente es Profesor Titular en el Área Control en la Facultad de Ingeniería de la UNLP e Investigador de la Comisión de Investigaciones Científicas dela Provincia de Buenos Aires (CICPBA). Sus temas de investigación actuales son los sistemas de procesamiento en tiempo real, sistemas de control, redes neuronales y arquitecturas de computadoras embebidas. El Dr. Mayosky es presidente del capítulo argentino de la sociedad de Inteligencia Computacional de la IEEE.