MIPS: Modelo de programación

Anuncio

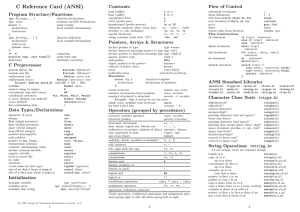

(I Pa rt e ) M I PS: M ode lo de progra m a c ión MIPS: Microprocessor without Interlocked Pipeline Stages Trabajaremos como MIPS Son similares a las desarrolladas en los años 80 Cerca de 100 millones de procesadores MIPS se fabricaron en el 2002 Utilizados por NEC, Nintendo, Cisco, Silicon Graphics, Sony, 1400 1300 Other SPARC 1200 Hitachi SH 1100 PowerPC 1000 Motorola 68K MIPS 900 IA-32 800 ARM 700 600 500 400 300 200 100 0 1998 Ing. JoséAlberto Díaz García 1999 2000 2001 2002 2 1. Simplicidad favorece la regularidad Mantenga todas las instrucciones de un tamaño simple Siempre se necesita de operandos de tres registros para en las operaciones aritméticas 2. Lo pequeño es más rápido Tiene solamente 32 registros 3. Un buen diseño hace buenos compromisos Compromisos entre proveer mayores direcciones e instrucciones constantes y mantener las instrucciones del mismo largo. 4. Hacer la parte común rápida El direccionamiento relativo al PC en los saltos condicionales Direccionamiento inmediato para operadores constantes Ing. JoséAlberto Díaz García 3 Configuración básica de una máquina Registros de trabajo Bus de Datos Memoria principal Bus de Direcciones Procesador Bus de control Ing. JoséAlberto Díaz García 4 Ing. JoséAlberto Díaz García 5 Name $zero $at $v0-$v1 $a0-$a3 $t0-$t7 $s0-$s7 $t8-$t9 $k0-$k1 $gp $sp $fp $ra Register number 0 1 2-3 4-7 8-15 16-23 24-25 26-27 28 29 30 31 Usage the constant value 0 reserved for assembler values for results and expression evaluation arguments temporary registers saved registers more temporary registers reserved for Operating System kernel global pointer stack pointer frame pointer return address Cada registro se puede utilizar por su nombre o por su número Ing. JoséAlberto Díaz García 6 FIGURE 2.11 What is and what is not preserved across a procedure call. If the software relies on the frame pointer register or on the global pointer register, discussed in the following subsections, they are also preserved. Copyright © 2009 Elsevier, Inc. All rights reserved. Ing. JoséAlberto Díaz García 7 FIGURE 2.10 The values of the stack pointer and the stack (a) before, (b) during, and (c) after the procedure call. The stack pointer always points to the top of the stack, or the last word in the stack in this drawing. Copyright © 2009 Elsevier, Inc. All rights reserved. Ing. JoséAlberto Díaz García 8 FIGURE 2.12 Illustration of the stack allocation (a) before, (b) during, and (c) after the procedure call. The frame pointer ($fp) points to the fi rst word of the frame, often a saved argument register, and the stack pointer ($sp) points to the top of the stack. The stack is adjusted to make room for all the saved registers and any memory-resident local variables. Since the stack pointer may change during pro gram execution, its easier for programmers to reference variables via the stable frame pointer, although it could be done just with the stack pointer and a little address arithmetic. If there are no local variables on the stack within a procedure, the compiler will save time by not setting and restoring the frame pointer. When a frame pointer is used, it is initialized using the address in $sp on a call, and $sp is restored using $fp. This information is also found in Column 4 of the MIPS Reference Data Card at the front of this book. Copyright © 2009 Elsevier, Inc. All rights reserved. Ing. JoséAlberto Díaz García 9 Usos de la memoria principal FIGURE 2.13 The MIPS memory allocation for program and data. These addresses are only a software convention, and not part of the MIPS architecture. The stack pointer is initialized to 7fff fffchex and grows down toward the data segment. At the other end, the program code ( text ) starts at 0040 0000hex. The static data starts at 1000 0000hex. Dynamic data, allocated by malloc in C and by new in Java, is next. It grows up toward the stack in an area called the heap. The global pointer, $gp, is set to an address to make it easy to access data. It is initialized to 1000 8000hex so that it can access from 1000 0000hex to 1000 ffffhex using the positive and negative 16-bit offsets from $gp. This information is also found in Column 4 of the MIPS Reference Data Card at the front of this book. Copyright © 2009 Elsevier, Inc. All rights reserved. Ing. JoséAlberto Díaz García 10 Ing. JoséAlberto Díaz García 11 Registros y sus aplicaciones FIGURE 2.14 MIPS register conventions. Register 1, called $at, is reserved for the assembler (see Section 2.12), and registers 26 27, called $k0 $k1, are reserved for the operating system. This information is also found in Column 2 of the MIPS Reference Data Card at the front of this book. Copyright © 2009 Elsevier, Inc. All rights reserved. Ing. JoséAlberto Díaz García 12 32 bits R0 R1 R2 R30 R31 32 registros para propósito general PC = 0x0000001C 0x00000000 0x00000004 0x00000008 0x0000000C 0x00000010 0x00000014 0x00000018 0x0000001C 0xfffffff4 0xfffffffc 0xfffffffc REGISTROS MEMORIA 4GB Max (generalmente 64MB-1GB) Ing. JoséAlberto Díaz García 13 ¿Qué es Big Endian? Ing. JoséAlberto Díaz García 14 Mas de la organización de memoria Dos puntos de vista de la memoria: 232 bytes con direcciones 0, 1, 2, , 232-1 230 4-byte words* con direcciones 0, 4, 8, , 232-4 Ambos puntos de vista utilizan direccionamiento por medio de Bytes No todas las arquitecturas lo requieren El direccionamiento por palabra debe ser múltiplo de 4 (alineado) 8 bits 0x00000000 0x00000001 0x00000002 0x00000003 32 bits 0x00000000 0x00000004 0x00000008 0x0000000C Ing. JoséAlberto Díaz García 0 1 2 3 15 FIGURE 2.18 Illustration of the five MIPS addressing modes. The operands are shaded in color. The operand of mode 3 is in memory, whereas the operand for mode 2 is a register. Note that versions of load and store access bytes, halfwords, or words. For mode 1, the operand is 16 bits of the instruction itself. Modes 4 and 5 address instructions in memory, with mode 4 adding a 16-bit address shifted left 2 bits to the PC and mode 5 concatenating a 26-bit address shifted left 2 bits with the 4 upper bits of the PC. Copyright © 2009 Elsevier, Inc. All rights reserved. Ing. JoséAlberto Díaz García 16 Ing. JoséAlberto Díaz García 17 Ing. JoséAlberto Díaz García 18