Tema 4 PROCESADORES SEGMENTADOS

Anuncio

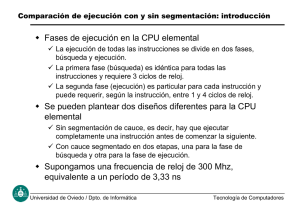

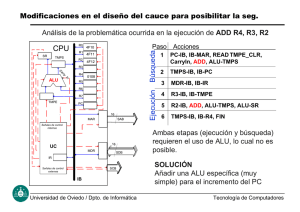

Arquitectura de Computadores Tema 4 PROCESADORES SEGMENTADOS 1. Arquitecturas RISC y CISC. 2. Unidad de Control monociclo y multiciclo. 3. Segmentación. 3.1. Ruta de datos del MIPS R2000. 3.2. Control segmentado. 3.2.1. Riesgos de la segmentación. 3.2.2. Riesgos estructurales. 3.2.3. Riesgos por dependencia de datos. 3.2.4. Riesgos de control 3.3. Segmentación en los operadores aritmético-lógicos. 4. Supersegmentación. Tema 4: Procesadores Segmentados 1 1. Arquitecturas RISC y CISC. ¾ El Juego de Instrucciones es una de las decisiones más importantes que debe tomar el diseñador. • • • • • Nº de instrucciones. Duración (en ciclos de reloj). Tamaño (RI). Nº operandos. Tipo. ¾ Hablemos del tipo. ¾ En los primeros computadores había pocas instrucciones con 1 o 2 modos de direccionamiento. ¾ En 1964 Wilkes introduce la microprogramación. • Las señales de control se almacenan en una memoria pequeña y rápida Î Memoria de Control. • Se simplifica la circuitería. • Los juegos de intrucciones se hacen cada vez más complejos. • Las instrucciones se acercan a las de los lenguajes de alto nivel. Sw Hw • Tendencia a incluir + instrucciones, + potentes y + modos de direccionamiento. • Arquitectura CISC (Complex Instruction Set Computers). • Ej: VAX Æ 200 instruc. y 12 modos de direcc. • Acabó siendo un freno a la velocidad del computador. Tema 4: Procesadores Segmentados 2 ¾ Años 70 Æ Cambio de filosofía. • Estudio de la frecuencia de ejecución de las instrucciones. • Se ejecutan más a menudo las más simples (transferencias, sumas, incrementos). • Se vuelve a juegos de intrucciones más sencillos con pocos modos de direccionamiento. Sw Hw • • • • • Se puede implementar con Control Cableado (+ rápido). Arquitectura RISC (Reduced Instruction Set Computers). Aumenta la complejidad de los compiladores. PRINCIPIO BÁSICO: ejecutar una instrucción por ciclo de reloj. Requieren memorias muy rápidas (cachés). ¾ Ejemplos: • CISC: Intel 80x86, Motorola 680x0 • RISC: MIPS Rx000, Motorola Power-PC, Sun SPARC. ¾ Tendencias: • Híbridos que llevan lo mejor de cada uno. • No hay una línea divisoria clara. Tema 4: Procesadores Segmentados 3 2. Unidad de Control monociclo y multiciclo. ¾ TIEMPO DE CICLO DEL RELOJ (TCLK): duración del periodo de reloj del sistema. (F = 1 / TCLK Mhz) • Las señales de control se activan y desactivan en sincronía con los pulsos del reloj. nivel alto flanco de bajada flanco de subida nivel bajo periodo (TCLK) Señal de reloj ¾ Nº DE CICLOS POR INSTRUCCIÓN: Tejec. instr. / TCLK • Tiempo de ejecución de una instrucción en ciclos de reloj. • Según se implemente la UC, una instruc. se ejecutará en uno o más ciclos de reloj. ¾ UNIDAD DE CONTROL MONOCICLO: • Cada instrucción se ejecuta en un ciclo de reloj. • PROBLEMA: El tiempo de ciclo de ejecución de instrucción se debe adaptar al de la instruc. más larga. • Todas las instruc. tardan lo mismo, aunque no lo necesiten. • Desaprovecha recursos Hw. del procesador (ocioso). TCLK Tema 4: Procesadores Segmentados 4 ¾ UNIDAD DE CONTROL MULTICICLO: • Hay instrucciones que no utilizan todas las etapas o su fase de ejecución dura menos. • IDEA: Descomposición en etapas de la ejecución de la instruc. (Busqueda instruc., operandos, etc.) • Cada etapa se ejecuta en un ciclo de reloj. • CICLO DE RELOJ: Tan largo como la etapa de instruc. más larga. • Varios tipos de instruc. en función de las etapas que utilizan. • Cada instruc. se ejecutará en tantos ciclos como etepas tenga (según su complejidad). • Lo normal es que las UC sean Multiciclo. • Permite mejorar las prestaciones del procesador usando técnicas como la SEGMENTACIÓN. CONTROL MONOCICLO TCLK TODAS LAS INSTRUCCIONES CONTROL MULTICICLO INSTRUCCIONES CLASE I INSTRUCCIONES CLASE II INSTRUCCIONES CLASE III INSTRUCCIONES CLASE IV TCLK Tema 4: Procesadores Segmentados 5 3. Segmentación. ¾ La ejecución de una instrucción pasa por varias etapas: 1. Búsqueda de Instrucción. 2. Decodificación. 3. Búsqueda de Operandos. 4. Ejecución. 5. Almacenamiento de Resultados. ¾ En un procesador NO segmentado las instrucciones se ejecutan secuencialmente. Operación de un procesador secuencial 1 2 3 4 5 6 7 ... Búsqueda1 Decodifica1 B.Operandos1 Ejecución1 Almacena1 Búsqueda2 Decodifica2 ... ¾ En un procesador SEGMENTADO cuando una instruc. termina por una etapa, esa etapa la ocupa la siguiente instruc. Operación de un procesador segmentado de 5 etapas 1 2 3 4 5 6 7 Búsqueda1 Búsqueda2 Búsqueda3 Búsqueda4 Búsqueda5 ... ... ... Decodifica1 Decodifica2 Decodifica3 Decodifica4 Decodifica5 ... ... ... B.Operandos1 B.Operandos2 B.Operandos3 B.Operandos4 B.Operandos5 ... ... ... Ejecución1 Ejecución2 Ejecución3 Ejecución4 ... ... ... ... Almacena1 Almacena2 Almacena3 ¾ Es como en las cadenas de montaje o los túneles. Tema 4: Procesadores Segmentados 6 ¾ Tras un intervalo de tiempo se termina de ejecutar una instrucción en cada ciclo de reloj. ¾ NOTA: No se reduce el tiempo de ejecución de la instrucción. ¾ Mejora la PRODUCTIVIDAD: Nº instruc. por unidad de tiempo. ¾ Se reduce el TIEMPO MEDIO DE EJECUCIÓN de las instrucciones. Tmedio _ ejec. = Tejec. _ todas _ las _ instruc. N º _ instruc. ¾ En un procesador segmentado ideal, la velocidad se multiplicaría por el nº de etapas en que está segmentado (x5 en el ejemplo). ¾ No va a ser así: • Las etapas no están equilibradas. 260 ms 50 50 60 50 50 50 INSTRUCCIÓN 1 50 ..... NO SEGMENTADO INSTRUCCIÓN 2 300 ms 60 60 60 60 60 SEGMENTADO 60 60 60 60 60 • La segmentación involucra gasto (TEJEC. ETAPA SEG > TEJEC. ETAPA NO SEG.). 325 ms 65 Tema 4: Procesadores Segmentados 65 65 65 65 65 65 65 65 65 7 ¾ ACELERACIÓN: Mejora en tiempo de ejecución de una máquina segmentada frente a la misma no segmentada. A= Tmedio _ sin _ seg . Tmedio _ con _ seg . = 260 =4 65 ¾ Veamos cómo se implementa una UC segmentada y cómo sería la ruta de datos en la ejecución de una instrucción. Tema 4: Procesadores Segmentados 8 3.1. Ruta de datos del MIPS R2000. ¾ Ruta de datos sin segmentar: Add 4 M U X Add BANCO DE REGISTROS registro de lectura 1 registro de Salida 1 lectura 2 MEMORIA DE INSTRUCCIONES cp Dirección de lectura instrucción M U X 16 registro de Salida 2 escritura dato de escritura extensión de signo despl. izq. 2 UAL Cero M U X 32 Resultado MEMORIA DE DATOS Dirección de lectura lectura Dirección dato de escritura dato de escritura Ruta de datos para la arquitectura MIPS ¾ Instrucciones y datos se desplazan de izda. a dcha., salvo: • Guardar resultado en registros. • Se cambia el CP (saltos). Elegir con el MUX, CP+4 (instruc. de 32 bits) Æ No hay salto. Dir. salto calculada en la fase de ejecución Æ Salto. ¾ La UAL se utiliza también para calcular la dirección de memoria donde leer/escribir un dato. Tema 4: Procesadores Segmentados 9 ¾ La ejecución de una instrucción se puede dividir en varias etapas. ¾ En el MIPS R2000 se divide en 5 etapas. ¾ Ello implica dividir la ruta de datos en 5 secciones. ¾ Cada una corresponderá a una etapa de la segmentación. Búsqueda de la instrucción Búsqueda registros y decodificación de la instrucción Ejecución y cálculo de la dirección de salto Acceso a memoria Guardar el resultado Add 4 M U X Add BANCO DE REGISTROS registro de lectura 1 MEMORIA DE INSTRUCCIONES CP UAL registro de Salida 1 lectura 2 Dirección de lectura instrucción despl. izq. 2 M U X 16 registro de Salida 2 escritura dato de escritura extensión de signo 32 Cero M U X Resultado MEMORIA DE DATOS Dirección de lectura lectura Dirección dato de escritura dato de escritura Ruta de datos para la arquitectura MIPS donde se observan las etapas de ejecución de las instrucciones Tema 4: Procesadores Segmentados 10 ¾ Funcionamiento de la segmentación en el MIPS R2000. • A la MEMORIA DE INSTRUCCIONES sólo se accede en la 1ª etapa de ejecución. • Puede ser compartida en la ejecución de otras instrucciones. Cuando la 1ª se encuentre en las otras 4 etapas. • Pero en el siguiente ciclo de reloj se perderá la 1ª instrucción. La MEMORIA DE INSTRUCCIONES se usará para obtener la siguiente instrucción a ejecutar. Para el resto de sus etapas no estará disponible. • Es necesario tener un REGISTRO TEMPORAL que guarde la instruc. para la siguiente etapa. • Para el resto de etapas ocurrirá lo mismo. • La ruta de datos contendrá una serie de registros temporales al final de cada etapa de segmentación. • Todas las instruc. avanzan durante cada ciclo de reloj de un registro al siguiente. Etapa 5 Búsqueda de instrucción Búsqueda de registros y decodificación Ejecución y cálculo dirección de salto Acceso a memoria Guardar el resultado Memoria de instrucciones Banco de registros (lectura) UAL Memoria de datos Registros temporales Etapa 4 Registros temporales Etapa 3 Registros temporales Etapa 2 Registros temporales Etapa 1 Banco de registros (escritura) Esquema simplificado de la ruta de datos junto con los registros de segmentación • El banco de registros aparece replicado. Se usa para lectura en la etapa 2. Se usa para escritura en la etapa 5. Lecturas y escrituras pueden realizarse a la vez. Tema 4: Procesadores Segmentados 11 3.2. Control segmentado. ¾ Veamos cómo se implementa una UC segmentada. ¾ En un procesador segmentado hay varias instruc. ejecutándose a la vez y usando la misma ruta de datos. ¾ IMPLEMENTACIÓN DEL CONTROL: • Actualizar todas las señales de control en cada etapa de la segmentación. • Señales diferentes para cada etapa. • Señales diferentes para cada instrucción. ¾ ¿CÓMO? • Incluir la información de control en los registros de segmentación. • Se crea en la etapa de decodificación y se guarda en el reg. correspondiente. • Esta información avanza por los registros de segmentación. • Así, las señales de control serán usadas por el procesador en la etapa adecuada. • Por eso hablamos de registros temporales. • Circuitería extra que causa un retardo en el tiempo de ejecución de cada etapa. Tema 4: Procesadores Segmentados 12 3.2.1. Riesgos de la segmentación. ¾ Idealmente, la segmentación produce una aceleración xN (N=nº etapas). ¾ Sabemos que hay factores que reducen esta aceleración: • Circuitería extra del control segmentado. • Ciclo de reloj = al de la etapa más larga. ¾ Existen otros factores que la disminuyen Î RIESGOS (hazards). ¾ Impiden que se ejecute la siguiente instrucción durante el ciclo de reloj que tiene asignado. ¾ TIPOS: • RIESGOS ESTRUCTURALES: Conflictos por uso de recursos del procesador por varias instruc. Varias etapas intentan usar a la vez un elemento de la ruta de datos. Ej: La UAL no puede hacer 2 sumas a la vez si no tiene 2 sumadores. • RIESGOS POR DEPENDENCIA DE DATOS: Cuando una instruc. depende de los resultados de una anterior. Si se ejecutan a la vez los resultados serán incorrectos. • RIESGOS DE CONTROL: Cuando una instruc. cambia el contenido del CP (saltos). Las instrucciones siguientes no deberían haberse iniciado. ¾ Estos riesgos pueden provocar la detención de la segmentación. Tema 4: Procesadores Segmentados 13 ¾ CAUSA: ejecutar varias instrucciones del mismo programa a la vez. ¾ Con la detención no se paran todas las instrucciones. ¾ Normalmente las posteriores a la que detiene la segmentación. ¾ Las anteriores continúan, pero no se buscarán nuevas instruc. Tema 4: Procesadores Segmentados 14 3.2.2. Riesgos estructurales. ¾ Al segmentar hay que replicar recursos para permitir todas las posibles combinaciones de instrucciones. ¾ Si en alguna combinación hay conflicto por recursos Î RIESGO ESTRUCTURAL. ¾ EFECTO: Se para una de las instruc. hasta que la unidad requerida esté disponible. ¾ La replicación de todos los elementos funcionales puede ser muy costosa. ¾ Si no se presentan con frecuencia estos riesgos, puede merecer la pena NO evitarlos. ¾ En el MIPS R2000 no existen, porque replica UFO’s: • Memoria (instruc. y datos). • Registros (lectura y escritura). ¾ Ejemplo: Procesador con 1 sóla MEM. para datos e instruc. • Dos etapas necesitan la memoria en el mismo ciclo de reloj para: Buscar la siguiente instruc. (BI) y Cargar un dato en el banco de registros (instruc. LW). Tema 4: Procesadores Segmentados 15 3.2.3. Riesgos por dependencia de datos. ¾ Cuando se cambia el orden de acceso a los operandos con relación al orden que se seguiría sin segmentación. ¾ Ejemplo: ADD $1, $2, $1 ($1Å $1+$2) SUB $4, $3, $1 ($4Å $3+$1) B.I. B.op. Ejec. Esc. Mem. Esc. Regs. Ejec. Guarda $1 Esc. Mem. ADD B.I. B.op. Esc. Regs. SUB Lee $1 Si no se toman precauciones, SUB leerá un valor erróneo de $1. ¾ TIPOS DE DEPENDENCIAS: • RAW (READ AFTER WRITE): Leer un dato antes de que tenga el resultado correcto. Sea la secuencia de instrucciones: ...... i, j, ...... Si se altera el orden, j leerá un valor todavía no modificado. Ver ejemplo anterior. Tema 4: Procesadores Segmentados 16 • WAR (WRITE AFTER READ): Escribir un dato antes de que se haya leído. Sea la secuencia de instrucciones: ...... i, j, ...... i lee objeto que j modifica. Si se altera el orden, i lee el modificado y no el original. Ej.: Procesador con tiempo de etapa de búsqueda de operandos variable según modo de direccionamiento empleado. SUB $1, a+100($2), $3 ( $1Å ([a]+(100+$2))-$3 ) ADD $2, $4, $5 ($2Å $4+$5) Si ADD actualiza $2 antes de que SUB lo lea, SUB leerá un valor erróneo. • WAW (WRITE AFTER WRITE): Cambiar el orden de escritura de los datos. Sea la secuencia de instrucciones: ...... i, j, ...... i escribe un dato en el mismo sitio que j. Si se altera el orden, no se guardará el valor que interesa (i), sino el anterior (j). Ej.: Procesador con tiempo de etapa de ejecución variable según complejidad de la instrucción. DIV.F $1, $4, $5 (División en coma flotante) ADD $1, $2, $3 (Suma de enteros) Si ADD actualiza $1 antes de que DIV.F termine, al final quedará un valor erróneo. ¾ SOLUCIONES: • Detención de la segmentación. • Anticipación. • Reordenación de código. Tema 4: Procesadores Segmentados 17 ¾ DETENCIÓN DE LA SEGMENTACIÓN. • Inserción de ciclos de espera. • La solución más sencilla, pero la menos eficiente. • Conocida como INSERCIÓN DE BURBUJAS. Primero se detecta el riesgo. Luego se detienen las instrucciones (se insertan burbujas) hasta que se resuelve el riesgo. • Ejemplo: ADD $1, $2, $1 SUB $4, $1, $3 Guarda $1 aquí ADD MEM. INSTRUC REGS. (lect.) U A L MEM. DATOS REGS. (escr.) Lee $1 aquí MEM. INSTRUC SUB BURBUJA BURBUJA U A L REGS. (lect.) BURBUJA MEM. DATOS REGS. (escr.) FASES BI DEC/BO EJ ESC. MEM. ESC. REG. ADD $1,$2,$1 SUB $4,$1,$3 ADD $1,$2,$1 BURBUJA ADD $1,$2,$1 BURBUJA BURBUJA MOV ... SUB $4,$1,$3 DIV ... MOV ... SUB $4,$1,$3 ADD $1,$2,$1 DIV ... MOV ... SUB $4,$1,$3 ADD $1,$2,$1 t1 t2 t3 Tema 4: Procesadores Segmentados t4 t5 t6 t7 t8 DIV ... MOV ... SUB $4,$1,$3 t9 TIEMPO 18 • ¿Cómo se implementa? Por SW: ⇒ El compilador detecta esta situación. ⇒ Inserta tantas operaciones NOP como sea necesario. ADD $1, $2, $1 NOP NOP NOP SUB $4, $1, $3 Por HW: ⇒ La detección del riesgo la hace la propia CPU. ⇒ Debe llevar la cuenta de los registros o posiciones de memoria que son destino. ⇒ ¿Cómo? Î Técnica de SCOREBOARDING (marcador). ⇒ Para los registros se añade un bit a cada uno. ⇒ Se pone a “1” al detectar que se va a usar como destino. ⇒ Se pone a “0” al escribirlo. Tema 4: Procesadores Segmentados 19 ¾ ANTICIPACIÓN (FORWARDING). • Consiste en llevar los datos a los registros de entrada de la UAL antes o al tiempo que se llevan al destino. • Hay una realimentación en la UAL. • El Hw detecta que el resultado de la operación anterior va a ser fuente de la actual. • La UC no se espera a que se escriba en el reg. destino, sino que se lo pasa a la UAL. Etapa 5 Búsqueda de instrucción Búsqueda de registros y decodificación Ejecución y cálculo dirección de salto Acceso a memoria Guardar el resultado Memoria de instrucciones Banco de registros (lectura) UAL Memoria de datos Registros temporales Etapa 4 Registros temporales Etapa 3 Registros temporales Etapa 2 Registros temporales Etapa 1 Banco de registros (escritura) Esquema simplificado de la ruta de datos con Anticipación • Ejemplo: ADD SUB AND XOR OR $1, $2, $1 $2, $6, $1 $3, $4, $1 $4, $5, $1 $5, $7, $1 FASES BI DEC/BO EJ ESC. M EM. ESC. REG. ADD $1,$2,$1 t1 SUB $2,$6,$1 AND $3,$4,$1 XOR $4,$5,$1 OR $5,$7,$1 ADD $1,$2,$1 SUB $2,$6,$1 AND $3,$4,$1 XOR $4,$5,$1 OR $5,$7,$1 ADD $1,$2,$1 SUB $2,$6,$1 AND $3,$4,$1 XOR $4,$5,$1 OR $5,$7,$1 ADD $1,$2,$1 SUB $2,$6,$1 AND $3,$4,$1 XOR $4,$5,$1 ADD $1,$2,$1 SUB $2,$6,$1 AND $3,$4,$1 t2 Tema 4: Procesadores Segmentados t3 t4 t5 t6 t7 TIEMPO 20 • También se pueden anticipar los datos leídos de Memoria a la UAL. Etapa 5 Búsqueda de instrucción Búsqueda de registros y decodificación Ejecución y cálculo dirección de salto Acceso a memoria Guardar el resultado Memoria de instrucciones Banco de registros (lectura) UAL Memoria de datos Registros temporales Etapa 4 Registros temporales Etapa 3 Registros temporales Etapa 2 Registros temporales Etapa 1 Banco de registros (escritura) Anticipación de los resultados leídos de memoria • Ejemplo: $5, x ($5 Å [x]) $4, $5, $3 $6, $5, $3 $1, $3, $7 LD ADD OR ADD FASES BI DEC/BO EJ ESC. MEM. ESC. REG. LD $5,x ADD $4,$5,$3 OR $6,$5,$3 LD $5,x ADD $4,$5,$3 LD $5,x BURBUJA LD $5,x t1 t2 t3 t4 ADD $1,$3,$7 OR $6,$5,$3 ADD $1,$3,$7 ADD $4,$5,$3 OR $6,$5,$3 ADD $1,$3,$7 ADD $4,$5,$3 OR $6,$5,$3 LD $5,x ADD $4,$5,$3 t5 t6 t7 TIEMPO • Aún así, en este caso, hay que introducir una burbuja. Tema 4: Procesadores Segmentados 21 ¾ REORDENACIÓN DE CÓDIGO. • Consiste en cambiar el orden de las instrucciones sin que afecte en la ejecución del programa. • La puede hacer a mano el programador. • Lo normal es que la haga el compilador. • Ejemplo: Se desea hacer el siguiente cálculo en un lenguaje de alto nivel: a=x-y b=z+w Un primer código en ensamblador sería el siguiente: LD LD SUB ST LD LD ADD ST $2, x $3, y $1, $2, $3 $1, a $5, z $6, w $4, $5, $6 $4, b ($2 Å [x]) ($3 Å [y]) Dependencia de datos en $3 ([a] Å $1) ($5 Å [z]) ($6 Å [w]) Dependencia de datos en $6 ([b] Å $4) Suponiendo que disponemos de anticipación de datos (UAL y MEM), la reordenación que elimina dependencias sería: LD LD LD SUB LD ST ADD ST $2, x $3, y $5, z $1, $2, $3 $6, w $1, a $4, $5, $6 $4, b ($2 Å [x]) ($3 Å [y]) ($5 Å [z]) Desaparece dependencia en $3 ($6 Å [w]) ([a] Å $1) Desaparece dependencia en $6 ([b] Å $4) Tema 4: Procesadores Segmentados 22 3.2.4. Riesgos de control. ¾ Se producen al no conocerse la dirección de bifurcación al ejecutar una instruc. que cambia el CP hasta que no la calcula la propia instruc. ¾ Mientras, se están ejecutando otras instrucciones en paralelo. ¾ Si hay que saltar, no sirven. ¾ Ejemplo: IF A=B THEN C=C+1 ELSE C=C-1 ENDIF ¾ SOLUCIONES: • • • • Detención de la segmentación. Ejecución Especulativa. Bifurcación Retardada. Predicción de Saltos. ¾ DETENCIÓN DE LA SEGMENTACIÓN (BURBUJAS). • Un procesador poco sofisticado pararía la segmentación hasta conocer la dirección de salto. • Poco eficiente. ¾ EJECUCIÓN ESPECULATIVA (PREDICT NOT TAKEN). • Se “especula” que no se va a saltar y, si se salta, se descartarán las instruc. que no sirvan. • Un poco mejor. Tema 4: Procesadores Segmentados 23 ¾ PREDICCIÓN DE SALTOS (BRANCH PREDICTION). • Se intenta predecir qué instrucción se ejecutará según la historia anterior. • Cuando se conoce la dirección de salto se comprueba si se ha acertado en la predicción: Acierto: se continúa, con el consiguiente ahorro de tiempo. Fallo: se descartan las instruc. ejecutadas y se inicia la rama real. • Consigue altas probabilidades de acierto. • Basa su éxito en la clara “asimetría” en el resultado de las instruc. de bifurcación condicional (bucles). • ¿Cómo se implementa? Con una memoria caché denominada BTB (Branch Target Buffer). Cuando el procesador ejecuta un salto, guarda información del mismo en la BTB. Cuando vuelve a encontrarse con ese salto, consulta la información guardada y “estima” hacia dónde irá el flujo del programa esta vez. Cuanto mayor sea la BTB, mayor cantidad de bifurcaciones se podrán predecir. PC INSTRUCCIÓN BTB PC INSTRUCCIÓN PC PREDICHO 0x00000028 0x00000034 0x0000001C 0x0000001C SALTO PREDICHO REALIZADO (SI/NO) 0 1 . . . . . . . . . 0x0000005C 0x000000FF 0x00000A3C 0x0000001C 1 0 = NO: Actualizar BTB y proceder normalmente SI: Usar PC predicho • Es la técnica más empleada en los procesadores actuales. Tema 4: Procesadores Segmentados 24 ¾ BIFURCACIÓN RETARDADA (DELAY SLOT). • Otra técnica, más económica, para aprovechar el hueco de las bifurcaciones condicionales. • Consiste en aplicar la REORDENACIÓN DE CÓDIGO para rellenar el hueco con instruc. útiles (compilador o programador). • ESTRATEGIAS: Utilizar instruc. anteriores a la bifurcación: ⇒ Es la mejor solución cuando hay instrucciones independientes para reordenar. ⇒ Problema: No siempre se pueden encontrar instruc. para rellenar el hueco. Utilizar las instruc. a las que se bifurca: ⇒ Es un caso de predicción de salto que sólo será útil si se bifurca. Utilizar las instruc. siguientes a la bifurcación: ⇒ Es el otro caso de predicción de salto que sólo será útil si NO se bifurca. • Según el tipo de procesador, el delay slot será de 1 o varias instruc. • EJEMPLO 1: Procesador con delay slot = 2. Programa original LD etiq: ADD ADD SUB BEQ LD $2, x $1, $2, $3 $4, $5, $6 $7, $8, $9 $6, $3, etiq (Si $6=$3 salta a etiq) $3, y Programa con bifurcación retardada LD etiq: ADD BEQ ADD SUB LD $2, x $1, $2, $3 $6, $3, etiq $4, $5, $6 $7, $8, $9 $3, y • EJEMPLO 2: Idem. Programa original LD etiq: ADD SUB BEQ LD $2, x $1, $2, $3 $4, $5, $6 $6, $3, etiq (Si $6=$3 salta a etiq) $3, y Tema 4: Procesadores Segmentados Programa con bifurcación retardada LD etiq: ADD BEQ SUB NOP LD $2, x $1, $2, $3 $6, $3, etiq $4, $5, $6 $3, y 25 3.3. Segmentación en los operadores aritmético - lógicos. ¾ Para mejorar las prestaciones de un procesador, también se puede segmentar la UAL. ¾ Vamos a ver el caso de un SUMADOR EN COMA FLOTANTE para nos positivos. Exponente B A Nº en coma flotante COMPARADOR Y SELECTOR Mayor exponente Otra mantisa Mantisa del número menor Desplazador a la derecha Diferencia de exponentes Nº de desplazamientos Para igualar exponentes Suma de mantisas SUMADOR Cálculo del número de ceros a la izquierda Mantisa Para normalizar Ej: 0.0010110 × 2 9 RESTADOR Desplazador a la izquierda 9–2=7 0.10110.... × 2 7 Mantisa normalizada Exponentes corregidos RESULTADO SUMADOR EN COMA FLOTANTE SIN SEGMENTAR Tema 4: Procesadores Segmentados 26 ¾ Se puede dividir en 5 operaciones independientes, que corresponderán a las etapas de la segmentación: • ETAPA 1: Resta de exponentes y selección del dato con menor exponente. • ETAPA 2: Ajuste a la derecha de la mantisa con menor exponente, hasta igualar exponentes. • ETAPA 3: Suma de mantisas. • ETAPA 4: Obtención del nº de ceroa a la izquierda. • ETAPA 5: Normalización, desplazando la mantisa suma a la izda. y decrementando el exponente. A E B M E Registros M Lógica Nivel 1 COMPARADOR Y SELECTOR Mayor exponente Otra mantisa Mantisa del número menor ETAPA 1 Diferencia de exponentes Registros Desplazador a la derecha Nº de desplazamientos Lógica Nivel 2 ETAPA 2 Registros SUMADOR Lógica Nivel 3 ETAPA 3 Registros Cálculo del número de ceros a la izquierda Lógica Nivel 4 ETAPA 4 Registros RESTADOR Desplazador a la izquierda Exponentes corregidos Lógica Nivel 5 ETAPA 5 Mantisa normalizada RESULTADO SUMADOR DE COMA FLOTANTE SEGMENTADO EN 5 ETAPAS Tema 4: Procesadores Segmentados 27 4. Supersegmentación. ¾ Se aumenta el nº de etapas de la segmentación. ¾ Se ejecuta más de una etapa por ciclo de reloj. Máquina segmentada: Instrucción 1 cr 1 cr 2 cr 3 cr 4 etapa1 etapa2 etapa3 etapa4 etapa1 etapa2 etapa3 etapa4 etapa1 etapa2 etapa3 etapa4 etapa1 etapa2 etapa3 etapa4 etapa1 etapa2 etapa3 Instrucción 2 Instrucción 3 Instrucción 4 Instrucción 5 cr 5 cr 6 cr 7 cr 8 etapa4 Máquina supersegmentada: Instrucción 1 se1 se2 se3 se4 se5 se6 se7 se8 Instrucción 2 Instrucción 3 Instrucción 4 Instrucción 5 se1 se2 se3 se4 se5 se6 se7 se8 se1 se2 se3 se4 se5 se6 se7 se8 se1 se2 se3 se4 se5 se6 se7 se8 se1 se2 se3 se4 se5 se6 se7 se8 se = subetapa cr = ciclo de reloj ESQUEMA DE UNA SEGMENTADA FRENTE A UNA MÁQUINA SUPERSEGMENTADA ¾ Se completan varias instrucciones por ciclo de reloj. ¾ “Idealmente” mejoran las prestaciones. • Aumentan los riesgos. • Un procesador supersegmentado no tiene por qué ser mejor que uno segmentado. Tema 4: Procesadores Segmentados 28