MEMORIAS Y LÓGICA PROGRAMABLE

Anuncio

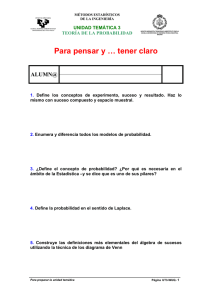

MEMORIAS Y LÓGICA PROGRAMABLE CONCEPTOS BÁSICOS eman ta zabal zazu LDD 2007-08 1 Memorias • Almacenan gran cantidad de información (datos). • Esquema lógico básico: DIR p MEM p 2 *n DAT n DAT n Señales de control eman ta zabal zazu LDD 2007-08 2 Tipos de memoria: 1. Acceso aleatorio (por la dirección): ° Memorias de lectura y escritura: RAM + Estáticas + Dinámicas ° Memorias de sólo lectura: ROM (ROM, PROM, EPROM, EEPROM, FLASH)) ° Redes programables: PLA, PAL, PLD etc... 2. Acceso por contenido: memorias asociativas. eman ta zabal zazu LDD 2007-08 3 Algunas definiciones: • Dirección : – Para guardar un dato – Para disponer/leer un dato • Tamaño o capacidad: Por ejemplo: 1k x 8, 8k – Tamaño del dato(palabra) : 8 bit – Número de datos (palabras) :1k eman ta zabal zazu LDD 2007-08 4 Algunas definiciones: • Tiempo de acceso: tiempo que transcurre desde que se inicicia una operación de lectura/escritura hasta que dicha operación finaliza: se dispone del dato/se ha escrito el dato. • Ciclo de lectura/escritura: Tiempo mínimo que ha de transcurrir entre dos operaciones de lectura/escritura consecutivas (operación + tiempo de espera) eman ta zabal zazu LDD 2007-08 5 Memorias RAM : • Nombre: memorias de acceso aleatorio (random access memory). • Memorias de lectura y escritura. • La información es volátil. • Dos tipos : – RAM estática (SRAM) – RAM dinámica (DRAM) eman ta zabal zazu LDD 2007-08 6 1. RAM estática • Esquema lógico: DIR p RAM 2p x n n DAT out n DAT in CS.L RD/(WR.L) eman ta zabal zazu LDD 2007-08 7 1. RAM estática • Ciclo de lectura: dirección RD/(WR.L) CS.L DAT Dato leído out tiempo de acceso eman ta zabal zazu LDD 2007-08 8 1. RAM estática • Ciclo de escritura: dirección RD/(WR.L) CS.L DAT in Dato a escribir Tiempo de acceso eman ta zabal zazu LDD 2007-08 9 2. RAM dinámica: • Memoria de mayor capacidad de almacenamiento • Celda básica: un condensador • Necesario: refresco (refresh) eman ta zabal zazu LDD 2007-08 10 2. RAM dinámica • Esquema lógico: p/2 DIR DRAM p 2 xn Din n Dout n RAS.L CAS.L RD/(WR.L) eman ta zabal zazu LDD 2007-08 11 2. RAM dinámica: • Ciclo de lectura: dirección fila columna RAS.L CAS.L RD/(WR.L)) DAT out dato ciclo completo de lectura eman ta zabal zazu LDD 2007-08 12 2. RAM dinámica: • Ciclo de escritura: dirección fila columna RAS.L CAS.L RD/(WR.L) dato DATin ciclo completo de escritura eman ta zabal zazu LDD 2007-08 13 Memorias ROM: • Nombre: read only memory. • Memorias de sólo lectura. • La información es permanente. eman ta zabal zazu LDD 2007-08 14 Memorias ROM: • Esquema lógico: ROM DIR p 2p x n CS.L n DAT out RD.L eman ta zabal zazu LDD 2007-08 15 Memorias ROM: • Ciclo de lectura: dirección RD.L CS.L Dato leído DATout tiempo de acceso eman ta zabal zazu LDD 2007-08 16 Tipos de memorias ROM: • • • • • ROM PROM EPROM EEPROM FLASH eman ta zabal zazu LDD 2007-08 17 Lógica programable: • Redes programables: – PROM, PAL. PAL, ... • PLDs – Incluyen componentes secuenciales – Pueden emplearse para implementar tanto la parte combinacional como secuencial de un sistema eman ta zabal zazu LDD 2007-08 18 Alternativas para implementar un sistema digital: Digital Logic Standard Logic TTL 74xx CMOS 4xxx Progammable Logic (FPLDs) PLDs FPGAs Full Custom ASICs Microproce ssor & RAM CPLDs Gate Arrays Standard Cell eman ta zabal zazu LDD 2007-08 19 Características de las tecnologías: Full Custom VLSI Design Speed, Density, Complexity, Market Volume needed for Product ASICs CPLDs FPGAs PLDs Engineering Cost, Time to Develop Product eman ta zabal zazu LDD 2007-08 20 Breve historia: • Inicialmente se usaban simples PLDs: PLAs/ PALs: Redes AND + OR. Implementan Sumas de términos producto (SOP) • Notación abreviada para indicar entradas de puertas AND/OR. • Sustituyen diseños TTL eman ta zabal zazu LDD 2007-08 21 Ejemplo PLA: eman ta zabal zazu LDD 2007-08 22 Situación actual: • Actualmente CPLDs y FPGAs de gran densidad, velocidad y coste relativamente bajos. • Permiten diseños de complejidad media/alta desarrollados en tpos menores (semanas frente a meses). Frecuencias de operación típicas: 50-400MHz. • ASICs/Fullcutom: generan diseños con frecuencias de operación altas (retardos menores), un consumo de área menor, y menor coste/unidad. • Pero los costes iniciales de los ingenieros de diseño son mucho mayores. eman ta zabal zazu LDD 2007-08 23 CPLDs y FPGAs: Estructura matricial: Repetición de un bloque de lógica combinacional programable (LE) + Elemento secuenciales (Biestables) + Red de interconexión programable + Bus especial para señal de reloj (clock skew) eman ta zabal zazu LDD 2007-08 24 Ejemplos de PLDs : eman ta zabal zazu LDD 2007-08 25 Arquitectura ALTERA MAX 7000 • Es una CPLD equivalente a 600 / 20.000 puertas • Configuración mediante programación de memoria tipo EEPROM (mantiene la configuración sin alimentación) una • Constan de 32 a 256 macroceldas agrupadas en LABs: Logic Array Blocks •Estructuras de E/S tipo buffer tri-estado programables: entrada, salida, bidireccionales. eman ta zabal zazu LDD 2007-08 26 Arquitectura ALTERA MAX 7000 LAB Local Array Parallel Logic Expanders (from other macrocells) Global Clear This respresents a multiplexer controlled by the configuration program Global Clock Programmable Register PRN ProductTerm Select Matrix Q D Clock/ Enable Select To I/O Control Block ENA CLRN Clear VCC Select Shared Logic Expanders eman ta zabal zazu 36 Signals from PIA To PIA 16 Expander Product LDD 2007-08 27 Arquitectura ALTERA MAX 7000 Input/GCLK1 Input/OE2/GCLK2 Input/OE1 Input/GCLRn 6 Output 6-16 I/O Pins 6 Output 6- LAB A 16 I/O Macrocells Control 1-16 6Block 3 16 Macrocells 17-32 1 616 I/O Control 6- Block 6-16 I/O Control Block 6- LAB C Macrocells 33-48 3 16 6-16 3 1 6-16 6-16 I/O Pins 6 PIA 6- 6 3 6-16 6 6-16 I/O Pins LAB B LAB D 6- Macrocells 49-64 I/O Control 6- Block 6-16 I/O Pins 6 eman ta zabal zazu LDD 2007-08 28 Arquitectura ALTERA FLEX 10K • Es una CPLD equivalente a 10.000 /250.000 puertas • Configuración : escritura en una memoria SRAM (NO mantiene la configuración sin alimentación, en sistemas reales se usa una PROM auxiliar) • La lógica combinacional se implementa mediante LE que contienen SRAM de 16x1. •Los LEs se agrupan en LABs: Logic Array Blocks. Puede haber de 72 a 1520 LABs. eman ta zabal zazu LDD 2007-08 29 Arquitectura ALTERA FLEX 10K •Los LEs se agrupan en LABs: Logic Array Blocks. Puede haber de 72 a 1520 LABs. DATA1 DATA2 DATA3 DATA4 Look-Up Table (LUT) Carry In Cascade Register Bypass In Carry Chain Cascade Chain Programmable Register PRN D Q To FastTrack Interconnect ENA CLRN To LAB Local Interconnect LABCTRL1 LABCTRL2 Clear/Preset Logic Chip-Wide Reset Clock Select LABCTRL3 LABCTRL4 eman ta zabal zazu Carry Out Cascade Out LDD 2007-08 30 Arquitectura ALTERA FLEX 10K (LABs) Dedicated Inputs & Global Signals Row Interconnect 6 4 4 Logic Block Array (LAB) 16 Carry-In and Cascade-In 2 4 LE1 4 LE2 4 LE3 4 LE4 4 LE5 4 LE6 4 LE7 4 LE8 8 2 8 4 24 Column-to-Row Interconnect 16 8 Carry-Out and Cascade-Out eman ta zabal zazu LDD 2007-08 31 Arquitectura ALTERA FLEX 10K •Existen también una estructuras de memoria de 2048 bits: los EABs •Los elementos de E/S son buffer tri-estado programables + un registro de 1 bit opcional IOE IOE IOE IOE IOE IOE IOE IOE I/O Element (IOE) IOE IOE IOE IOE Row IOE IOE Local Interconnect EAB Logic Element (LE) IOE IOE Row IOE IOE Logic Array EAB Logic Array Block (LAB) IOE IOE IOE IOE IOE IOE IOE IOE IOE IOE eman ta zabal zazu LDD 2007-08 Embedded Array Block (EAB) 2K Bits RAM 32 Arquitectura XILINX 4000 • Es una familia de FPGA de 2.000 a 180.000 puertas • Configuración : escritura en una memoria SRAM (NO mantiene la configuración sin alimentación) • Constan de unos Bloques Lógicos Configurables: CLBs en una estructura matricial con una red de interconexión programable. • Cada CLB incluye: – 3 SRAM (LUTs) – 2 biestables • Los drivers de E/S: IOB son programables de tipo tri-estado, con registro opcional. • Los dispositivos constan de 100 a 3.000 CLBs. eman ta zabal zazu LDD 2007-08 33 Arquitectura XILINX 4000 C1 • • • C4 4 H1 G4 G3 G2 G1 DIN/H2 SR/H0 EC S/R Control Look-Up Table (LUT) Register Bypass EC RD Look-Up Table (LUT) YQ SD D Q Programmable Register 1 Y Register Bypass F4 F3 F2 F1 K S/R Control Look-Up Table (LUT) SD D Q EC RD XQ Programmable Register 1 (Clock) X eman ta zabal zazu LDD 2007-08 34 Aplicaciones de PLDs: • Han sustituido los diseños realizados hace algunos años mediante CI • Procesado digital de señal (DSP) • Aplicaciones de multimedia • Comunicaciones de alta velocidad • Sistemas de redes • Implementación de protocolos de bus • ........... eman ta zabal zazu LDD 2007-08 35 Última generación de PLDs: • Mayor tamaño y prestaciones • Nuevas estructuras internas que permiten diseños más complejos en un área menor • Tensiones de alimentación menores: 1.5 V a 3 V • Módulos de altas prestaciones: – Multiplicadores de alta velocidad (DSP) – Microprocesadores tipo RISC – ...... eman ta zabal zazu LDD 2007-08 36