Bibliografía: William Stallings Computer Organization and

Anuncio

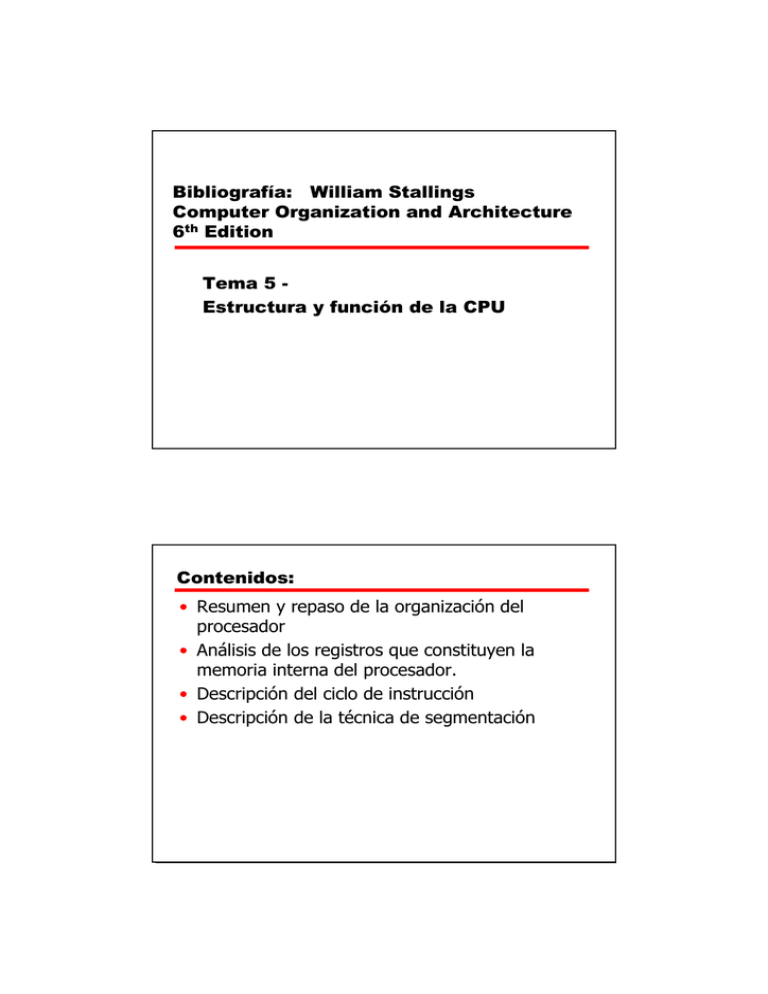

Bibliografía: William Stallings Computer Organization and Architecture 6th Edition Tema 5 Estructura y función de la CPU Contenidos: • Resumen y repaso de la organización del procesador • Análisis de los registros que constituyen la memoria interna del procesador. • Descripción del ciclo de instrucción • Descripción de la técnica de segmentación Estructura de la CPU • CPU debe: —Captar instrucciones de la memoria —Interpretar instrucciones ( decodificar) —Captar datos ( leer de memoria o de un mòdulo E/S) —Procesar datos —Escribir datos ( en la memoria o en modulo de E/S) • Para esto la CPU necesita: —Recordar la direccion de la ultima instruccion, para captar la siguiente —Almacenar instrucciones y datos temporalmente mientras una instruccion se ejecuta —El procesador necesita una pequeña memoria interna. La CPU y el Bus del sistema Estructra Interna de la CPU Organización de los registros • La CPU debe tener algún espacio de trabajo (almacenamiento temporario) • Llamados registros • Su número y función varía entre diseños de procesadores. • Esto es una de las mayores decisiones de diseño • En el nivel más alto de la jerarquía de memorias • Pueden ser de dos tipos: — Registros visibles para el usuario: permiten al programador de ensamblador minimizar las referencias a memoria principal por medio de su uso. — Registros de control y de estado: son utilizados por la unidad de control para el control del funcionamiento de la CPU y por programas privilegiados del sistema operativo para controlar la ejecucion. Registros visibles para el usuario (I) • Puede ser referenciado por medio del lenguaje de máquina que ejecuta la CPU. • Categorías: —Propósito general —Datos —Direcciones —Códigos de condición Registros de Propósito General: (I.I) • Pueden ser utilizados por el programador para diversas funciones. • Puede contener el operando para cualquier código de operación( ortogonal a la operación) • Existen restricciones: específicos para operaciones de coma flotante y operaciones de pila • En algunos casos pueden usarse para funciones de direccionamiento • En otros hay una separación total o parcial entre registros de datos y regitros de direcciones. Registros visibles para el usuario. (I) • Registros de datos (I.2) —Para contener datos —No pueden emplearse en el calculo de una dirección de operando. • Registros de dirección (I.3) —Punteros de segmento: En una maquina con direccionamiento segmentado, contiene la dirección de base del segmento. —Registros de índice: Se usan para direccionamiento indexado, y pueden ser autoindexados. —Puntero de pila : Si existe direccionamiento a pila visible al usuario, la pila en memoria y y este registro apunta a la cabecera. Registros de uso general: • Cuestiones de diseño a estudiar: • 1) Usar registros de uso completamente general —Incrementa la flexibilidad y las opciones del programador —Incrementa el tamaño de instrucción y la complejidad. • 2) o Usar registros especializados —Instrucciones más cortas y rápidas —Limita la flexibilidad del programador —La tendencia va en este sentido. Registros de uso general: Cuestiones de diseño a estudiar: • 3) Cuántos registros de uso general se deben incluir? • Esto afecta el diseño del repertorio de instrucciones • Número ópimo entre 8 - 32 • Menos registros = más referencias a memoria • Más registros no reducen notablemente las referencias a memoria • Una aproximación distinta en algunos sistemas RISC: uso de cientos de registros. Registros de uso general: Cuestiones de diseño a estudiar: • 4) Cuán largos? • Registros de direcciones: tan grandes como para albergar la dirección más grande • Registros de datos: deben ser capaces de contener valores de la mayoría de tipos de datos. • Algunas máquinas permiten que dos registros contiguos sean usados como uno sólo para contener valores de doble longitud. —C programación —double int a; —long int a; Registros visibles para el usuario: Registros de códigos de condición (I.4) • Son al menos parcialmente visibles para los usuarios (“indicadores “ o “Flags”). • Conjuntos de bits individuales fijados por el hardware de la CPU: —ejemplo: resultado de la última operación fue cero • Pueden leerse por referencia implícita, mediante programas —ejemplo: Jump if zero • No pueden ser alterados por el programador • Los bits de código de condición se reúnen en uno o más registros. • Normalmente forman parte de un registro de control Registros de control y de estado • La mayoría de ellos en la mayor parte de las maquinas no son visibles para el usuario. • Maquinas diferentes tendrán diferentes organizaciones de registro y terminología. • Son esenciales 4 registros para la ejecución de una instrucción: • Contador de Programa (Program Counter, PC) • Registro de instrucción (Instruction Register, IR) • Registro de dirección de memoria (Memory Address Register, MAR) • Registro intermedio de memoria (Memory Buffer Register, MBR) • Revisión: Cómo funcionan todos ellos ? Registros de control y de estado • La CPU los emplea para controlar su funcionamiento • Son esenciales cuatro registros para la ejecución de una instrucción: • PC: Contiene la dirección de la instrucción a captar • IR: contiene la instrucción captada más recientemente • MAR: contiene la dirección de una posición de memoria • MBR: contiene la palabra de datos a escribir en memoria, o la palabra leída más recientemente. Registros de control y de estado • La CPU actualiza el contador de programa después de cada captación de instrucción. • Siempre apunta a la siguiente instrucción a ejecutar. • Una inst. de bifurcación también modificará el contenido de PC. La inst. captada se carga en IR, donde son analizados el código de operación y los campos de operando. • Se intercambian datos con la memoria por medio de MR y de MBR. • En un sistema con organización de bus, MAR se conecta directamente al bus de direcciones y MBR directamente al bus de datos. • Los registros visibles por el usuario intercambian repetidamente datos con MBR. Estos 4 se usan para la transferencia de datos entre CPU y la memoria. Registros de control y de estado • Dentro del procesador, los datos se ofrecen a la ALU. • Esta puede acceder al MBR y a los registros visibles por el usuario. • La ALU puede tener registros intermedios adicionales Palabra de estado del programa • Todos los diseños de CPU incluyen registros con información de estado. • Es un conjunto de bits (PSW: Program Status Word) • Contiene códigos de condición. • Signo: Contiene el bit de signo del resultado de la última operación aritmética • Cero: Puesto a uno cuando el resultado es 0. • Acarreo: Puesto a uno si si una operación da lugar a un acarreo. • Igual: Puesto a uno si el resultado de una comparación lógica es la igualdad. • Desbordamiento • Interrupciones habilitadas/inhabilitadas • Supervisor: Indica si la CPU funciona en modo supervisor o usuario. Modo Supervisor • Modo núcleo • Permite la ejecución de instrucciones privilegiadas • Usado por el sistema operativo • No está disponible para usuarios de programas Otros registros • Puede haber registros señalando a: —Un bloque de memoria que contenga información adicional (e.j. Bloques de control de procesos) —Registro de vector de interrupción. —Registros para el control de operaciones de E/S. • El diseño de CPU y el diseño del sistema operativo están estrechamente ligados-> la organización de los registros se adapta al S.O. • Decisión clave de diseño es la distribución de la información de control entre registros y memoria. Habitual compromiso entre coste y velocidad. Ejemplos de organización de registros Ejemplos de organización de registros • Motorola: Quiso un repertorio de instrucciones muy regular. • Sin registros de uso especial. • Su interés por la eficiencia del código los condujo a dividir los registros en dos componentes funcionales • Intel: Cada uno de los registros tiene un uso especial. • Algunos se emplean para uso general. • Tiene 4 registros de datos de 16 bits. • No hay una filosofía universalmente aceptada sobre la mejor forma de organizar los registros de la CPU. Ciclo de instrucción Ciclo de instrucción • Un ciclo incluye los siguientes sub_ciclos: • Captación: Llevar la siguiente instrucción de la memoria a la CPU. • Ejecución: Interpretar el código de operación y llevar a cabo la operación indicada • Interrupción: Si las interrupciones están habilitadas y ha ocurrido una interrupción salvar el estado del proceso actual y atender la interrupción. Ciclo de instrucción indirecto El ciclo indirecto • La ej. de una instrucción-->puede involucrar a uno o más operandos en memoria. • Cada operando requiere un acceso a memoria. • Si se usa direccionamiento indirecto serán necesarios accesos a memorias adicionales • La captación de direcciones indirectas puede considerarse como un sub-ciclo de instrucción más • Alterna la captación con la ejecución de instrucciones Diagrama de estados del ciclo de instrucción Flujo de datos • Son esenciales 4 registros para la ejecución de una instrucción: • Contador de Programa (Program Counter, PC): —Contiene la dirección de la instrucción a captar • Registro de instrucción (Instruction Register, IR) —Contiene la instrucción captada mas recientemente • Registro de dirección de memoria (Memory Address Register, MAR) —Contiene la dirección de una posición de memoria • Registro intermedio de memoria (Memory Buffer Register, MBR) —Contiene la palabra de datos a escribir en memoria o la palabra leída mas recientemente. Flujo de datos (Instrucción de captación ) • Depende del diseño de la CPU. En general: • Captación: —Se lee una instrucción de la memoria. —El PC contiene la dirección de la instrucción siguiente —Esta dirección se lleva a MAR —Se coloca en el bus de dirección —La unidad de control requiere una lectura de memoria —Resultado se pone en el bus de datos, se copia en MBR y se lleva a IR —Mientras tanto el PC se incrementa en 1 Flujo de datos (Diagrama de Captación) Flujo de datos (Concluida la Captación) • La UC examina los contenidos de IR • Determina si contiene un campo de operando que use direccionamiento indirecto • Si es así se lleva a cabo un ciclo indirecto —Los N bits más a la derecha de MBR se transfieren a MAR —La unidad de Control solicita una lectura de memoria —El resultado (dirección del operando deseado) se mueve a MBR Flujo de datos (Ciclo indirecto) Flujo de datos (Ejecución) • Puede tomar muchas formas • Depende de cuál de las diversas instrucciones maquina esté en IR • Puede incluir —Lectura o escritura de memoria o E/S —Entrada o salida —Transferencia de datos entre registros —Invocación a la ALU Flujo de datos (Ciclo Interrupción) • Simple y Predecible • Contenido actual de PC salvado para permitir que la CPU reanude su actividad • Contenido de PC se transfiere a MBR • La posición de memoria especial (ej. Puntero de pila) se carga en MAR desde UC • MBR será escrito en memoria • PC se carga con la dirección de la rutina de interrupción • Siguiente instrucción (primera del manejador de interrupciones) puede ser captada Flujo de datos (Ciclo de Interrupción) Estrategia de segmentación de instrucciones • Mayores prestaciones de CPU: —- Aprovechando circuitos mas rápidos ( progresos de la tecnología). — Avances en la organización de la CPU • Similar al uso de una cadena de montaje en una fábrica. • Proceso de segmentación de cauce: en un extremo se aceptan nuevas entradas, antes de que algunas entradas anteriores aparezcan como salidas. • Subdivisión de procesamiento en dos etapas: —Captación de instrucción —Ejecución de instrucción Pipeline de instrucciones con dos etapas Precaptación • El tiempo de ejecución en que no se accede a memoria principal->podría utilizarse para captar la sgte. inst. en paralelo • La ejecución no accede generalmente a memoria principal • Puede captar la siguiente instrucción durante la ejecución de la instrucción corriente • Se llaman instrucciones de precaptación o solapamiento de la captación ( fetch overlap) • Este proceso acelerara la ejecución de instrucciones. Incremento de performance • Si captación y ejecución fueran de = duración-> • Tiempo del ciclo de instrucción se reduciría a la mitad. • Velocidad duplicada de ejecución es poco probable: —Captación es en general más corta que la ejecución – Deberá esperar algún tiempo antes de vaciar su bufffer —Cualquier bifurcación o salto significa que la instrucción precaptada no sea la instrucción requerida. —Captación debe esperar la dirección de la siguiente instrucción desde la etapa de ejecución. • Agregar mayores niveles para incrementar la performance. Segmentación de cauce (Pipelining) • Considerar la siguiente descomposición del procesamiento: • Captación de instrucción (Fetch Instruction, FI) • Decodificación de la instrucción (Decode Instruction, DI) • Calculo de operandos (Calculate Operands, CO) (i.e. EAs): Calcular la EA de c/operando. • Captación de operandos ( Fetch Operands, FO) • Ejecución de instrucciones (Execute Instruction, EI) • Escritura de resultados (Write Operand, WO) • Sobreposicionamiento de estas operaciones Diagrama de tiempos del pipeline Cauce de instrucciones • Factores que limitan las prestaciones: • Si las seis etapas no son de igual duración->habrá espera en ciertas etapas • La instrucción de bifurcación condicional: —Puede invalidar varias captaciones de instrucción • Otro evento impredecible: —Llegada de una interrupción • Otra situación: —La etapa CO (Calcular Operandos) puede depender del contenido de un registro que podría verse alterado por una instrucción previa que aun esta en el cauce —Conflictos con registros y memoria Cauce de instrucciones • El diagrama supone que todas las etapas pueden funcionar en paralelo. • Se supone que no hay conflictos de memoria. • Por ejemplo las etapas FI, FO y WO requieren acceso a memoria. • El diagrama implica que todos estos accesos pueden tener lugar simultáneamente pero en la realidad no sucede así. • No obstante el valor deseado puede estar en la caché, o las etapas FO o WO pueden ser nulas. • Los conflictos de memoria en general, no reducirán la velocidad del cauce. Efecto de una bifurcación condicional Efecto de una bifurcación condicional •Se supone que la instrucción 3 es una bifurcación condicional a la instrucción 15. Hasta que no se ejecuta la instrucción no hay forma de saber que instrucción vendrá a continuación. •El cauce carga la siguiente instrucción secuencialmente ( la 4 ) y continua. Aquí se produce un salto. •Éste no se determina hasta el final de la unidad de tiempo 7. En ese momento el cauce debe limpiarse de instrucciones que no son útiles. Durante la unidad de tiempo 8, la instrucción 15 entra en el cauce. Ninguna instrucción termina durante las unidades 9 a la 12 •Esta es la penalización en las prestaciones sufrida por no haber podido prever el salto. Cauce de instrucciones de una CPU con seis etapas Segmentación y performance • Factores que frustran este patrón sencillo de diseño de altas prestaciones • 1) En c/ etapa del cauce: gasto extra debido a la transferencia de datos de buffer a buffer, y a la realización de varias funciones de preparación y distribución. Esto puede prolongar sensiblemente el tiempo de ejecución total de una instrucción aislada. • Importante cuando las instrucciones secuenciales son lógicamente dependientes: a causa de un uso abundante de bifurcaciones, o debido a dependencias de acceso a memoria. Segmentación y performance • 2) La cdad de lógica de control necesaria para manejar dependencias de memoria y de registros y para optimizar el uso del cauce aumenta enormemente con el número de etapas. • Eso puede lleva a una situación donde la lógica para controlar el paso entre etapas sea más compleja que las etapas controladas. • Conclusión: Es una poderosa técnica para aumentar las prestaciones pero requiere un diseño cuidadoso si se quieren obtener resultados óptimos con una complejidad razonable. Factores de aceleración en segmentación de cauces: en funcion del nro de inst. Que se ejecutan sin saltos (a) En función del nro. de instrucciones que se ejecutan sin saltos. En el limite (n-> ∞) la velocidad se incrementa k veces. (b) Se aproxima al nro. de instr. que pueden introducirse en el cauce sin saltos. Cuanto > es el nro. de etapas del cauce, > es su potencial para conseguir aceleración. A tener en cuenta: Los beneficios potenciales de etapas adicionales en el cauce se contrarrestan por los incrementos en coste, los retardos entre etapas y la necesidad de vaciar el cauce. Procesamiento de interrupciones • Es un servicio que se proporciona para apoyar al sistema operativo. • Permite que un programa de aplicación sea suspendido • -- Se atiendan una gran variedad de causas de interrupción • ---Reanudado más tarde Procesamiento de Interrupciones en el Pentium II • Interrupciones: se generan por una señal de hardware y pueden ocurrir en momentos aleatorios de la ejecución. — Enmascarables — No enmascarables • Excepciones: se genera desde el software y es provocada por la ejecución de una instrucción. — Detectadas por el procesador — Programadas: Por instrucciones especificas que las generan (INTO, INT 3, INT, y BOUND) • Tabla de vectores de interrupción — Cada tipo de instrucción tiene asignado un número — Que sirve para indexar en la tabla — 256 vectores de interrupción de 32 bits — Cada uno es la direccion de la rutina de servicios de interrupcion del nro correspondiente • 5 clases de prioridades Gestión de Interrupciones en el Pentium II • Un transferencia a una rutina de interrupción: Usa la pila del sistema para almacenar el estado del procesador. Se produce una secuencia de eventos: — Si hay un cambio del nivel de privilegio: contenidos actuales se introducen en la pila — El valor actual del registro EFLAGS (indica el estado del procesador) se introduce en la pila — Indicadores de Interrupciones (IF) y de trampa (TF) se ponen a 0. — Los contenidos actuales del puntero de segmento de código (CS) y de puntero de instrucción (IP o EIP) se introducen en la pila — Código de error se introduce en la pila — Los contenidos del vector de interrupción se captan y cargan en los registros CS e IP o EIP. — La ejecución continua por la rutina de servicio de interrupción. — Se ejecuta una instrucción IRET: provoca que los valores almacenados en la pila sean restblecidos. — La ejecución se reanuda a partir del punto de interrupción.