Sistema modular para generación de imágenes en tiempo

Anuncio

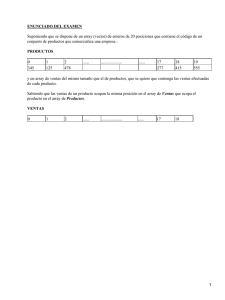

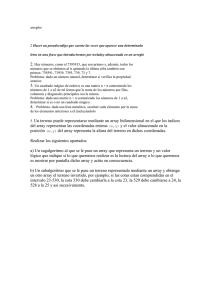

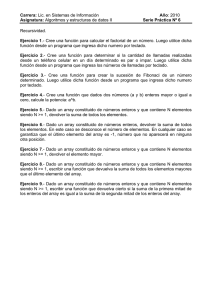

Montevideo, 27-29 de setiembre de 2006 IBERSENSOR 2006 Modular System for Real Time Image Generation with Ultrasound Arrays J. Camacho*, C. Fritsch, M. Parrilla, A. Ibáñez Instituto de Automática Industrial (CSIC) La Poveda (Arganda), 28500 Madrid (Spain) (*) Jorge Camacho, +34 91 871 19 00, [email protected] Abstract Obtaining real time images with ultrasonic arrays require complex electronic systems, mainly because of the large quantity of active elements, high frequency of ultrasound signals, high voltage used during emission and demanding signal processing and beam-forming functions. For research purposes, as well as for Non Destructive Testing (NDT) and Medicine applications, a very flexible equipment regarding hardware configuration and algorithm implementation is required. This is not usually available on commercial equipment. In this work we present the development of a modular and scalable system for real time imaging with ultrasonic arrays, flexible enough for implementing new excitation, signal processing and beam-forming techniques for NDT and Medicine applications. Keywords: Ultrasound Hardware, Ultrasound Beamforming, Phased Array, SAFT, Progressive Focusing Correction. Introducción En la actualidad existen distintas técnicas para la obtención de imágenes con arrays ultrasónicos pero todas ellas constan básicamente de cinco etapas: 1) Excitación de los elementos del array, 2) Adquisición de las señales de cada elemento, 3) Composición de los haces o de la imagen, 4) Procesamiento de señal y 5) Representación Gráfica. Según la técnica que se utilice, los esquemas de excitación y composición son diferentes (ej. Phased-Array, SAFT, etc.) variando los requerimientos del sistema en función de la técnica utilizada. La excitación se realiza mediante la generación de pulsos o trenes de pulsos de alta tensión para cada uno de los elementos del array de manera independiente. Controlando el instante de excitación de cada elemento se logra deflectar y focalizar el haz ultrasónico en el medio, lo cual permite en sucesivos disparos generar un barrido en la zona de interés (técnica Phased-Array). Variando la deflexión se genera un barrido sectorial, mientras que cambiando el grupo de elementos activos en cada disparo se genera un barrido lineal. En la técnica SAFT uno o varios elementos del array son excitados simultáneamente generando en el medio un frente de ondas no focalizado, lo cual se repite para elementos distintos en cada disparo. En cualquiera de estas técnicas pueden utilizarse códigos binarios durante la excitación, con el fin de mejorar la relación señal-ruido o para separar en recepción las señales generadas con cada elemento. Las discontinuidades en la densidad del medio generan ondas acústicas reflejadas que son ISBN: 9974-0-0337-7 convertidas nuevamente por el mismo array en señales eléctricas (modo Pulso-Eco), o captadas por un segundo array (modo Pitch&Catch). Las señales generadas por cada elemento del array son amplificadas y digitalizadas de forma independiente por circuitos electrónicos dedicados, que incorporan funciones como la compensación automática de ganancia y el filtrado analógico de señal. Una vez digitalizadas, las señales de cada elemento deben componerse para obtener una línea focalizada de la imagen. Por ejemplo, en la técnica PhasedArray se suman de forma coherente para obtener una única traza correspondiente a un determinado ángulo de deflexión con focalización en uno o más puntos de esa dirección. Para focalizar en múltiples puntos es necesario retardar el inicio de la adquisición de cada elemento y variar el instante de muestreo de cada señal a lo largo de la adquisición en tiempo real. En la técnica SAFT se almacenan las señales recibidas por todos los elementos y se componen una vez realizada la excitación de todos los elementos del array. Para cualquier técnica utilizada es necesario cierto procesamiento de señal en tiempo real que incluye, entre otros, filtros Pasa-Banda, Detectores de envolvente y Reductores de datos. La representación gráfica de la imagen se realiza en general en un computador externo con una interfaz de usuario que permite tanto tomar medidas sobre la imagen adquirida como cambiar los parámetros de funcionamiento del sistema. El sistema presentado en este trabajo implementa todas las funcionalidades descritas anteriormente de manera flexible y modular, lo cual permite utilizar 1/6 Montevideo, 27-29 de setiembre de 2006 IBERSENSOR 2006 distintos esquemas de excitación, procesamiento y generación de la imagen en tiempo real. Está dividido en tarjetas que controlan la emisión, recepción y procesamiento de 32 elementos del array, con la posibilidad de conectar varias de estas tarjetas para manejar arrays de mayor tamaño. 1 Arquitectura Para lograr un sistema modular fue necesario definir una arquitectura, identificar bloques funcionales y buscar una implementación física que permitiera la sustitución de estos bloques al cambiar los requerimientos. Elegimos AMPLIA [1] como la arquitectura del sistema por ser altamente modular, escalable y diseñada específicamente para sistemas de ultrasonido. E/S EXTERNAS - Pulsers, Conversores A/D, Encoders, etc. PC MÓDULO N UCI INTERFAZ PC - PC104 - USB .... MÓDULO 0 BUS AMPLIA - 32 bits Datos + 8 bits Control - BUS Bidireccional y Segmentado Figura 1 – Esquema de la arquitectura AMPLIA. En AMPLIA (Figura 1) se define una Unidad de Control e Interfaz (UCI), un Bus de 32 bits de datos y Módulos Genéricos. La UCI implementa la comunicación con el ordenador externo mediante algún bus estándar (Actualmente PC104 o USB). Tiene la capacidad de almacenar secuencias de comandos para ser ejecutados sin intervención del ordenador externo, posee una memoria para almacenar los resultados de la adquisición y puede manejar distintas fuentes de disparo (Interno, Externo, Base de Tiempos y Encoder). Los Módulos AMPLIA se interconectan mediante un BUS bidireccional y segmentado de 32 bits de datos y 8 bits de control. La cantidad de módulos está limitada a 256 únicamente por la capacidad de direccionamiento del sistema, ya que al ser un bus segmentado no presenta problemas de carga. Además de comunicarse entre sí mediante el BUS AMPLIA, los módulos pueden contar con entradas y salidas externas (Pulsers, Conversores A/D, Encoders, etc.). El funcionamiento de un sistema AMPLIA está dividido en dos fases: 1) Configuración, en la cual se envían comandos desde la UCI hacia los módulos con el fin de configurar los parámetros de operación, y 2) Procesamiento, donde los módulos ISBN: 9974-0-0337-7 entregan a la UCI los resultados de la adquisición. En este último caso cada módulo genera señales externas (ej. Pulsers) y procesa en tiempo real tanto los datos externos (ej. Conversores AD) como los generados por el módulo anterior, para luego transferirlos al módulo siguiente hasta llegar a la UCI. Esta arquitectura en pipeline permite el procesamiento de datos en tiempo real a la frecuencia del reloj maestro del sistema (Típicamente 40 MHz). Para este sistema se definieron dos tipos de módulos AMPLIA: 1) Módulos Digitalizadores y 2) Módulos Base. Los Módulos Digitalizadores incorporan la emisión, recepción y procesamiento para 8 elementos del array. Están implementados físicamente por dos tarjetas, una analógica con la electrónica de excitación y recepción para cada elemento, y una digital que controla la generación de pulsos de excitación y realiza la conversión AD y el procesamiento de las señales. Para la técnica Phased-Array realiza el beam-forming de las 8 señales del módulo y compone el resultado con la señal entregada por el módulo anterior antes de entregar el resultado al módulo siguiente. Para la técnica SAFT almacena las señales de cada elemento para ser transferidas y procesadas por el ordenador externo. Cada Módulo Base se conecta a 4 Módulos Digitalizadores formando en una misma tarjeta un subsistema completo de 32 elementos. Para PhasedArray cada Módulo Base realiza el beam-forming de la señal generada por sus 4 Módulos Digitalizadores con la señal conformada de los 32 elementos del siguiente Módulo Base en la cadena de procesamiento. Además implementa funciones comunes a sus 4 módulos, como son el filtrado digital, detección de envolvente, reducción de datos y generación de la curva de ganancia. Físicamente el sistema está implementado con 3 tipos de tarjetas: 1) Analógicas, 2) Digitales y 3) Tarjetas Base. Esta última contiene la electrónica que implementa el Módulo Base y provee de conectividad a 4 tarjetas analógicas y 4 tarjetas digitales que conforman los 4 Módulos Digitalizadores (Figura 2). De esta manera cada Tarjeta Base con sus módulos conectados forma un subsistema completo analógico-digital de 32 elementos. Para aumentar la cantidad de elementos activos del sistema se conectan sobre una tarjeta de interconexión (TARMA) hasta 6 Tarjetas Base, con lo cual se obtiene un sistema de 192 canales. Es 2/6 Montevideo, 27-29 de setiembre de 2006 posible interconectar varias tarjetas TARMA para manejar arrays de mayor tamaño (p. ej. arrays 2D). TARJETA BASE ELECTRÓNICA DIGITAL MÓDULO BASE MÓDULO DIGITALIZADOR TARJETA DIGITAL TARJETA ANALÓGICA MÓDULO DIGITALIZADOR TARJETA DIGITAL TARJETA ANALÓGICA MÓDULO DIGITALIZADOR TARJETA DIGITAL TARJETA ANALÓGICA MÓDULO DIGITALIZADOR TARJETA DIGITAL TARJETA ANALÓGICA BUS AMPLIA BUS ANALÓGICO CONECTORES HACIA EL ARRAY Figura 2 – Esquema de una tarjeta base de 32 canales. Las señales analógicas de cada Tarjeta Base se unen en una Tarjeta Frontal que posee el conector para el array. Esta Tarjeta Frontal puede conectar las señales de cada Tarjeta Base directamente a los elementos correspondientes en el array o incorporar una electrónica de multiplexado que permita seleccionar distintos elementos cuando la cantidad de elementos del array es superior a la cantidad de canales del sistema. Para el prototipo construido se fabricó una tarjeta con una relación de multiplexado de 128 a 32, lo cual permite utilizar un array de 128 elementos con una sola Tarjeta Base de 32 canales para realizar Barrido Lineal (apertura activa de hasta 32 elementos), técnicas de apertura dispersa, pitchcatch, etc. 2 Tarjeta Analógica Cada una de estas tarjetas contiene la electrónica analógica necesaria para excitar y recibir señales de 8 elementos del array. Los pulsers o circuitos de excitación son capaces de generar pulsos, trenes de pulsos, escalones (steps) o picos (spikes) de hasta 200V de amplitud, tiempos de subida y bajada menores a 5ns. Cada pulser está formado por un par de transistores MOSFET de potencia en ISBN: 9974-0-0337-7 IBERSENSOR 2006 configuración PUSH-PULL, controlados por dos señales digitales con niveles lógicos CMOS_3.3V. Para la recepción de las señales se utilizaron amplificadores de bajo ruido con ganancia variable entre 0 y 55dB, y se implementaron filtros analógicos para limitar el ancho de banda del sistema entre 350kHz y 20MHz (Figura 3). Cuando se trabaja en modo Pulso-Eco es necesario proteger la entrada de los amplificadores contra la alta tensión generada por los pulser. En general se utiliza un limitador de tensión formado por un par de diodos y una resistencia serie, lo cual tiene la desventaja de consumir corriente durante la excitación. Para este sistema se diseñó un circuito de protección activa basado en un transistor MOSFET de deplexión, que actúa como una llave analógica controlada por la tensión de entrada. De esta manera, cuando la tensión de entrada supera un umbral fijado en -3V la llave se abre protegiendo los amplificadores, y se cierra durante la recepción de las señales que en ningún caso superan este umbral. La ventaja de este circuito es que durante la generación del pulso de alta tensión el transistor presenta muy alta impedancia eliminando el consumo de corriente que presenta el limitador de diodos, y la baja impedancia durante la recepción reduce la pérdida de señal e introduce muy poco ruido. Una de las medidas realizadas fue el nivel de ruido a la entrada de cada canal. Para ello se midió el ruido RMS a la salida de los amplificadores, a máxima ganancia y con la entrada sin conectar. Figura 3 – Transferencia promedio medida sobre los amplificadores (sin filtro anti-aliasing). La banda pasante en -3dB es 0.37-77 MHz, y en -6dB es 0.24-85 MHz. Dividiendo este valor entre la ganancia del sistema se puede estimar el ruido equivalente a la entrada y teniendo en cuenta la máxima excursión de la señal se calcula la máxima SNR a la entrada del sistema. El valor medio obtenido para los 32 elementos del prototipo construido fue de 78 dB. 3/6 Montevideo, 27-29 de setiembre de 2006 También se midió el cross-talk entre elementos adyacentes conectando un transductor monoelemento de 8 MHz en un canal y adquiriendo con todos los canales. El valor medio obtenido para canales adyacentes fue de -34 dB. IBERSENSOR 2006 internamente se obtienen los dos relojes complementarios con los cuales se registran los datos del conversor. Para absorber las diferencias de tiempo debidas al ruteo de las señales en la tarjeta es necesario ajustar la fase de los relojes internos para registrar las señales en el momento óptimo. Figura 4 – Fotografía de una Tarjeta Analógica, de dimensiones 97 x 43 mm. Para generar las señales de control a los pulser se implementó en la FPGA un bloque de excitación capaz de generar pulsos, trenes de pulsos o códigos binarios de hasta 16 bits (configurables e independientes para cada elemento). La resolución en el ancho de los pulsos es de 6.25 ns y el período mínimo 12.5ns lo cual permite excitar transductores de hasta 40 MHz. El instante de inicio de la excitación es programable para cada elemento con una resolución de 6.25ns. El PCB para esta tarjeta fue realizado en 6 capas para reducir al máximo el ruido externo, utilizando planos de tierra en todas las capas. Los componentes fueron colocados para minimizar las dimensiones de la tarjeta, y en el trazado de las señales se tuvieron en cuenta consideraciones de ruido y cross-talk entre canales. Para la técnica SAFT se implementó en la FPGA de cada módulo la lógica que permite almacenar hasta 4096 muestras (100 µs) de cada uno de los elementos del array. Al finalizar la adquisición se transfieren al ordenador externo que, tras obtener las señales correspondientes a todos los disparos, realiza la composición de la imagen. 3 Tarjeta Digital Para la técnica Phased-Array cada FPGA realiza la composición del haz en recepción para cada uno de sus 8 elementos, y compone, en tiempo real, el resultado con la señal entregada por el módulo anterior. Para la composición se implementó, además de la focalización fija, la técnica de Corrección Focal Progresiva (FocPro) [2], que permite focalizar en recepción a lo largo de toda la adquisición con un error en el instante de muestreo menor a medio ciclo de reloj (3.125 ns). Esta técnica implica modificar, en tiempo real, el instante de adquisición de cada muestra para ajustar los tiempos de vuelo de la onda ultrasónica desde cada elemento a cada uno de los focos. Como el instante de muestreo real no puede ser modificado de forma independiente para cada canal debido a que cada conversor AD digitaliza 4 canales con un mismo reloj, las señales muestreadas a 40MHz son interpoladas por 4 dentro de la FPGA para lograr una resolución en el muestreo de 6.25 ns. La técnica FocPro minimiza la cantidad información necesaria para definir una ley focal codificando cada corrección en la adquisición con 1 bit y variando la cantidad de muestras entre focos, asegurando siempre un error acotado en el instante de muestreo Para focalizar a distancias muy cercanas al array, sin perder resolución, se implementó un algoritmo de apertura dinámica que permite aumentar la cantidad de elementos activos a medida que avanza la adquisición. Cada Tarjeta Digital contiene la electrónica de digitalización y procesamiento para 8 elementos del array. Se utilizó un dispositivo de lógica programable (FPGA XILINX Spartan3 X3S1000) donde se implementa la lógica de excitación, adquisición, apertura dinámica, apodización, beamforming, almacenamiento y comunicación AMPLIA de cada módulo. Este tipo de dispositivos aporta una gran flexibilidad al sistema ya que pueden ser fácilmente reconfigurados para implementar diferentes técnicas de inspección y procesamiento de señal. Cuentan con una memoria RAM interna de 384 kbits que cubre los requerimientos de almacenamiento tanto para la técnica Phased-Array como para la técnica SAFT. Para la digitalización de las señales se utilizaron conversores cuádruples de 12bits y 40MHz con salida serie diferencial (LVDS). La interfaz serie reduce significativamente la cantidad de señales digitales en la tarjeta, lo cual es necesario para lograr el nivel de integración buscado. La principal desventaja de este tipo de interfaz es la elevada tasa de transferencia de bits, en este caso 480 Mbps (12 bits a 40 Msps con lectura en doble flanco), lo cual requiere un diseño cuidadoso de la lógica de adquisición dentro de la FPGA. Cada conversor AD genera un reloj de 240 MHz que indica con sus dos flancos (DDR) el instante en que es válido cada uno de los 12 bits de cada muestra. Dicho reloj se conecta a entradas dedicadas en la FPGA e ISBN: 9974-0-0337-7 4/6 Montevideo, 27-29 de setiembre de 2006 En un barrido angular cada disparo corresponde a un ángulo de deflexión distinto, y por lo tanto tiene asociadas una ley focal en emisión y una en recepción. Cada ley focal en emisión está compuesta por los retardos aplicados a los N elementos del array, y cada ley focal en recepción está compuesta por N retardos iniciales que determinan la posición del primer foco. Para poder generar una imagen completa sin la intervención del ordenador externo, se pueden almacenar en cada FPGA hasta 256 leyes focales para los 8 elementos de cada módulo. A partir del primer foco en recepción se utilizan los códigos de corrección focal. Debido a que la memoria que almacena los códigos de corrección focal para la técnica FocPro está limitada a 16384 códigos, se puede configurar el sistema para que varias líneas angularmente próximas utilicen un mismo conjunto de códigos de corrección focal, pero distinta ley focal El PCB de esta tarjeta fue realizado en 6 capas debido a la alta densidad de señales. Para lograr el tamaño de placa buscado se utilizó para la FPGA un encapsulado BGA (Ball Grid Array) que provee una alta densidad de pines. Para el ruteo de señales se tomaron como principales criterios, minimizar el cross-talk entre pistas y reducir la emisión electromagnética que puede introducir ruido en la etapa analógica del sistema. IBERSENSOR 2006 coeficientes programables, y permite eliminar ruido y señales de baja frecuencia después del beamforming. El detector de envolvente realiza la rectificación de onda completa y suaviza la señal mediante un filtro de media móvil adaptado a la frecuencia central del transductor. El reductor de datos provee una reducción de (N+2):2, con N configurable, y funciona entregando en orden de aparición, el máximo y el mínimo de la señal en cada uno de los intervalos definidos por el factor de reducción N, lo que asegura la detección de todos los picos. En cada Módulo Base se implementó también el control de ganancia para los amplificadores, con la posibilidad de variar la misma de forma arbitraria durante la adquisición programando una memoria dedicada de 2048 posiciones (Compensación Atenuación-Distancia). Cada Tarjeta Base posee los conectores para 4 Tarjetas Analógicas y 4 Tarjetas Digitales, implementando el BUS AMPLIA entre módulos. Ademas posee 2 conectores hacia el array, uno para trabajar en modo Pulso-Eco y otro para conectar el array de recepción en el modo Pitch&Catch. Cada Tarjeta Analógica cuenta con llaves analógicas que permiten seleccionar el modo de operación. Además cada uno de estos conectores posee 4 líneas digitales para controlar los multiplexores que pueden estar presentes en la Tarjeta Frontal. El PCB de esta tarjeta también fue realizado en 6 capas, ya que en el trazado de las líneas analógicas hacia el array es necesario minimizar el cross-talk intercalando tierra entre señales y separando las mismas en distintas capas del impreso. Figura 5 – Fotografía de una Tarjeta Digital, de dimensiones 68 x 43 mm. Figura 6 – Fotografía de una Tarjeta Base, de dimensiones 250 x 100 mm. 4 Tarjeta Base 5 Tarjeta de multiplexado La tarjeta base posee también una FPGA (Xilinx Spartan3 X3S1000) que implementa funciones comunes a los 4 Módulos Digitalizadores que controla. Además, realiza el beam-forming de sus 4 módulos con el resultado del Módulo Base anterior en el caso de Phased-Array. Se implementaron en el Módulo Base 3 bloques de procesamiento de señal: 1) un Filtro Pasa-Banda, 2) un Detector de Envolvente y 3) un Reductor de Datos. El filtro pasa-banda es un FIR de 63 ISBN: 9974-0-0337-7 Para el prototipo construido se diseñó una Tarjeta Frontal con capacidad de multiplexar los 32 canales activos del sistema sobre un array de 128 elementos, lo cual permite realizar barridos lineales y aperturas dispersas. Los multiplexores están controlados por la Tarjeta Base mediante 4 líneas de control incluidas en el conector analógico. El PCB de esta placa fue realizado en 8 capas, debido a la gran cantidad de señales, todas ellas 5/6 Montevideo, 27-29 de setiembre de 2006 analógicas, que necesitan ser apantalladas para minimizar el cross-talk y reducir el ruido del sistema. IBERSENSOR 2006 recepción a lo largo de toda la adquisición, minimizando la cantidad de memoria necesaria para almacenar las leyes focales. En la Figura 9 se comparan dos imágenes de una probeta industrial adquiridas con un solo foco en recepción contra una tercera obtenida con la técnica ProFoc. El sistema es capaz de adquirir en tiempo real y sin la intervención del ordenador externo, imágenes de hasta 256 líneas. Se realizaron pruebas sobre distintas probetas industriales y un phantom médico, y los resultados obtenidos son ampliamente satisfactorios. Figura 7 – Fotografía de una Tarjeta Frontal Multiplexada, de dimensiones 200 x 130 mm. 6 Software El software de control y visualización fue realizado en lenguaje C++ para sistemas operativos Microsoft Windows® de 32 bits. Está dividido en 3 capas: 1) Drivers de Bajo Nivel, 2) Funciones de Hardware y 3) Funciones de Interfaz de Usuario. La primera incluye las rutinas de comunicación con la interfaces PC104 y AMPLIA, y se encarga de transferir a la UCI el programa a ejecutar. Las Funciones de Hardware traducen los valores de la adquisición definidos por el usuario en los parámetros físicos del sistema. La capa de más alto nivel implementa la interfaz de usuario, formada por funciones de entrada de datos y funciones de visualización de resultados en tiempo real. Figura 9 – Imágenes de una pieza de acero con 2 grupos de 3 taladros transversales separados 5mm. Las imágenes superiores se obtuvieron utilizando un solo foco en recepción a 20 mm (izqda) y 40 mm (dcha) de profundidad. La imagen inferior se obtuvo utilizando la técnica de focalización progresiva (FocPro). Agradecimientos Este trabajo ha sido realizado en el marco del proyecto DPI2004-06470 del Mº de Educación y Ciencia. Referencias Figura 8 - Imagen del software de Control y Visualización [1] C. Fritsch, T. Sánchez, D. Jiménez: AMPLIA: Una Arquitectura Modular para el Procesamiento y Despliegue de Imagen Acústica, Revista de Acústica (ISBN: 84-87985-03-3), vol 31, 2000. [2] J. Camacho, M. Parrilla, C. Fritsch: Dynamic Focusing for Medical Echography, Ibersensor 2006, 27-29 Sept. 2006, Montevideo, Uruguay. 7 Resultados Se construyó un prototipo de 32 canales activos y capacidad de multiplexado de 32 a 128 elementos, capaz de funcionar en modo Full Phased Array en tiempo real o registrando las señales de cada elemento para su procesamiento offline. Se implementó la técnica de Corrección Focal Progresiva, que permite focalizar el haz en ISBN: 9974-0-0337-7 6/6