SPI - BUCOMSEC - Comunicaciones y Seguridad

Anuncio

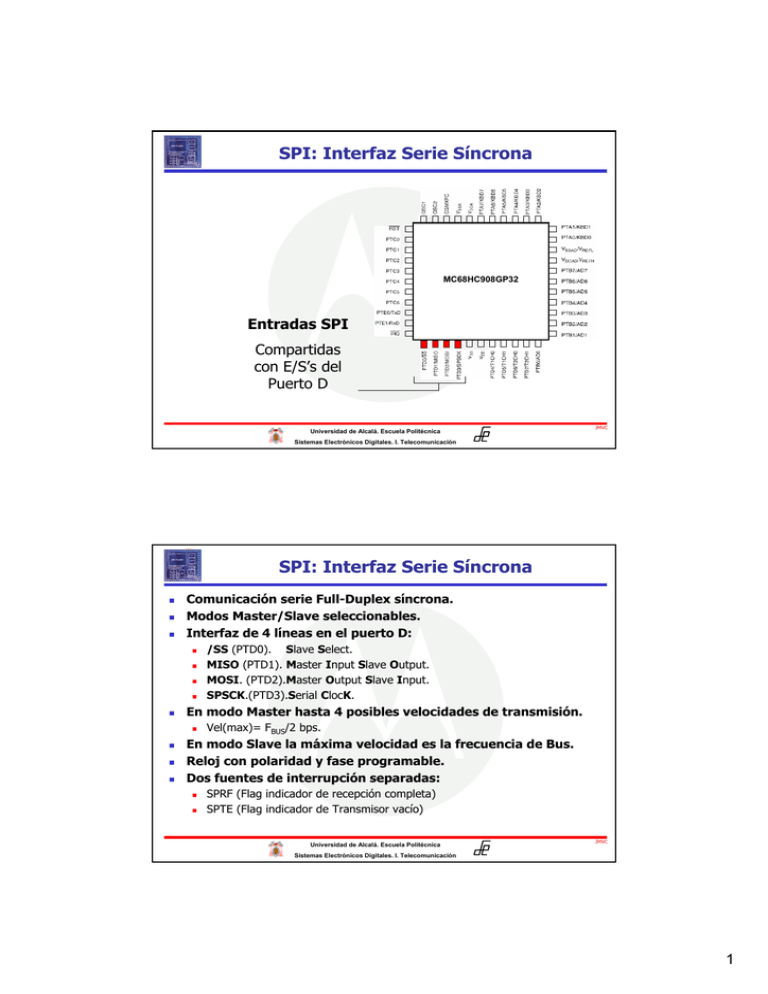

SPI: Interfaz Serie Síncrona MC68HC908GP32 Entradas SPI Compartidas con E/S’s del Puerto D Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación SPI: Interfaz Serie Síncrona Comunicación serie Full-Duplex síncrona. Modos Master/Slave seleccionables. Interfaz de 4 líneas en el puerto D: En modo Master hasta 4 posibles velocidades de transmisión. /SS (PTD0). Slave Select. MISO (PTD1). Master Input Slave Output. MOSI. (PTD2).Master Output Slave Input. SPSCK.(PTD3).Serial ClocK. Vel(max)= FBUS/2 bps. En modo Slave la máxima velocidad es la frecuencia de Bus. Reloj con polaridad y fase programable. Dos fuentes de interrupción separadas: SPRF (Flag indicador de recepción completa) SPTE (Flag indicador de Transmisor vacío) Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación 1 SPI: Funcionamiento HC08 Slave HC08 Master BUS interno BUS interno SPDR TRANSMIT 1 0 1 DATA 0 1 REGISTER 0 1 0 RECIVE 1 0 1DATA 0 1REGISTER 0 1 0 SHIFTDESPLAZAMIENTO REGISTER REGISTRO x1 x 0 x 1 x 0 x 1 x0 SPDR REGISTRO DESPLAZAMIENTO MISO x 0x 1 1x 0x 1x 0x 1x 0x 1x 0x MOSI MOSI Registro de Recepción de Datos SPDR PIN CONTROL LOGIC M Control de Reloj SPTIE Registro de Transmisión de Datos SPDR SPSCK SPRIE S SS 0 0 VDD SS SPTE SPRF 0 1 01 JMVC Universidad de Alcalá. Escuela Politécnica Sistemas Electrónicos Digitales. I. Telecomunicación SPCR: Registro de Control del SPI READ: SPRIE DMAS SPMSTR CPOL CPHA SPWOM SPE SPTIE WRITE: RESET: 0 1 0 0 0 CPOL=1. Activo el nivel alto. CPOL=0. activo el nivel bajo. CPHA=1. Selecciona el primer flanco activo al comienzo de la transmisión del bit MSB. CPHA=0. Selecciona el primer flanco activo en mitad del bit MSB (medio ciclo más tarde). SPWOM. Modo Wire-OR pines SPI 1 CPHA. Fase de la señal de reloj 0 SPRIE. Habilitación de interrupciones del Receptor. DMAS. Bit selección DMA (Sólo en CPU,s con DMA). SPMSTR. Salección modo Master/Slave. CPOL. Polaridad de la señal de reloj 0 SPWOM=1, salida Wired-OR de los pines SPSCK, MOSI, MISO. SPWOM=0, salida normal push-pull. SPE. Habilita el SPI. SPTIE. Habilitación de interrupciones del Transmisor. Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación 2 SPSCR: Registro de Estado-Control del SPI READ: SPRF OVRF ERRIE MODF SPTE MODFEN SPR1 SPR0 WRITE: RESET: 0 0 SPR1:0 0 Baud rate Divisor Si SPTIE=1, se genera una interrupción cuando el registro de recepción se llena. Se borra leyendo el registro SPSCR, seguido del registro de datos SPDR, del SPI. 0 0 0 1 8 ERRIE=1. Los flag,s OVRF y MODF activan una petición de interrupción. ERRIE=0. Los flag,s OVRF y MODF no activan interrupción. 1 0 32 1 1 128 2 Indica que un nuevo dato ha entrado en el registro receptor, y aún no ha sido leído el anterior. Se borra leyendo el registro SPSCR, seguido del registro de datos SPDR, del SPI. Si el SPI se configura en modo Master, MODF=1 cuando el pin /SS se pone a nivel bajo. Si el SPI se configura como Slave, MODF=1 cuando el pin /SS se pone a nivel alto durante la transmisión. SPTE. Flag indicador de Transmisor vacío. 1 MODF. Flag indicador de fallo de modo. 0 OVRF. Flag de desbordamiento. 0 ERRIE. Habilitación interrupción por error en el SPI 0 SPRF. Flag indicador de Receptor lleno. 0 Si SPTIE=1, se genera una interrupción cuando el registro transmisor de datos está vacío. No de debe escribir en SPDR hasta que esté flag esté activo. MODFEN. Habilita la detección de fallo de modo. SPR1:SPR0. Selección de la velocidad de transmisión. Vt = CGMOUT/2·BD [bps] Nota: FBUS = CGMOUT/2 Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación SPI: Esquema interno Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación 3 SPI: Formato de transmisión CPHA=0 Si CPHA=0 el primer flanco de reloj captura el MSB. El Slave ha de tener el dato válido antes de este flanco. El Slave inicia su transmisión con el flanco de bajada de /SS. El pin /SS ha de desactivarse-activarse por cada byte transmitido. JMVC Universidad de Alcalá. Escuela Politécnica Sistemas Electrónicos Digitales. I. Telecomunicación SPI: Formato de transmisión CPHA=1 Si CPHA=1, el Master comienza a sacar el dato por MOSI con el primer flanco de la señal de reloj. El Slave utiliza el primer flanco de reloj para iniciar su transmisión. La señal /SS ha de permanecer a nivel bajo durante la transmisión. Este modo es el preferido cuando hay un solo Master y un Slave. Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación 4 SPI: Formato de transmisión Temporización pin /SS en función de CPHA CPHA=0 CPHA=1 Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación SPI: Inicialización Master-Slave Inicializar la frecuencia del reloj Configurar el reloj Bit SMPSTR (en SPSCR) Activar las interrupciones (opcional) Bits CPOL y CPHA (en SPSCR) Seleccionar el modo master/slave Bits SPR1, SPR0 (en SPSCR) Bits SPTIE y SPRIE (en SPCR) Activar el SPI master Activar el SPI slave Universidad de Alcalá. Escuela Politécnica JMVC Sistemas Electrónicos Digitales. I. Telecomunicación 5