EJERCICIOS DE TEORIA DE CONTROL AUTOMATICO

Anuncio

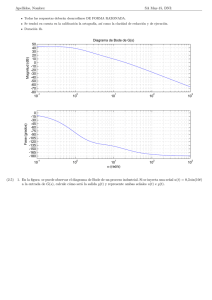

1 EJERCICIOS DE TEORIA DE CONTROL AUTOMATICO DISEÑO DE CONTROLADORES EN DOMINIO FRECUENCIAL 100 100 / 15 = . Se desea diseñar un controlador PD ( s + 3) ( s + 1) ( s + 5) (1 + s / 3) (1 + s ) (1 + s / 5) para que el sistema resultante en bucle cerrado cumpla lo siguiente: P9. Sea el sistema: G ( s ) = - Error en régimen permanente ante escalón menor o igual al 10%. - Sobreoscilación igual al 25% - Tiempo de subida menor o igual a 0.5 segundos Solución: En primer lugar calculamos la ganancia necesaria para satisfacer el error en régimen permanente: e rp escalón = 1 ≤ 0.1 ( 10% ) ⇒ K p ≥ 9 1+ K p Si denominamos K c a la ganancia que aportará el controlador: K p = 100 / 15 K c ≥ 9 ⇒ K c ≥ 1.35 Dibujamos el diagrama de Bode del sistema de partida, incluyendo la ganancia necesaria para satisfacer las especificaciones del error en régimen permanente, es decir con una ganancia conjunta K p ≥ 9 ⇒ K pdB ≥ 19dB . Se trata de la curva que aparece en azul en la gráfica de la página siguiente. A continuación, vemos el margen de fase necesario de acuerdo con la sobreoscilación especificada: SO% ≈ 1.6 (60 o − M f ) ⇒ M f ≈ 44.3 o Asimismo, de acuerdo con el tiempo de subida especificado, la frecuencia de corte aproximada debería estar entorno a: ωc ≈ π 2 ts ≥ 3.14 rad / s Podemos ver que la frecuencia de corte de partida se encuentra aproximadamente a 5 rad/s, con lo cual estaríamos cumpliendo las especificaciones relativas al tiempo de subida. Sin embargo, vemos que el margen de fase que quedaría a esa frecuencia de corte es prácticamente cero. De hecho, podemos calcularlo con precisión, para salir de dudas acerca de su valor: arg(G ( jw)) w=5 = [− arg(1 + jw / 3) − arg(1 + jw) − arg(1 + jw / 5)] w=5 = −182 o Luego vemos que, si no añadimos nada, el sistema en BC sería inestable. Necesitamos un aporte de fase de unos 46.3 o a la frecuencia de 5 rad/s. Luego un PD parece, efectivamente, una buena opción: C ( s ) = K c (1 + Td s) Si colocamos la “frecuencia de esquina” del PD media década antes de la frecuencia de corte: 1 = 10 −0.5 5 = 1.58 rad / s Td Al sumar gráficamente las curvas de magnitud, resultaría la curva dibujada en verde, obteniéndose una frecuencia de corte de unos 9 rad/s, ciertamente más a la derecha del mínimo exigido. Para ver si interesa reducir dicha frecuencia de corte, aproximándola más a la mínima deseada, bastaría con ver si a la frecuencia de 9 rad/s el margen de fase es insuficiente. En apariencia, a la vista de la curva de fase dibujada M.Vargas 2006 2 EJERCICIOS DE TEORIA DE CONTROL AUTOMATICO DISEÑO DE CONTROLADORES EN DOMINIO FRECUENCIAL en verde, dicho margen está cercano a los 45º, suficiente para lo que me piden. Para estar seguros del valor de margen de fase que resulta, calculemos la fase analíticamente a la frecuencia de 9 rad/s: arg(C ( jw) G ( jw)) w=9 = [arg(1 + jw / 1.58) + arg(G ( jw))] w=9 = −136.13 o con lo que resulta un margen de fase: M f ≈ 43.8 o Podríamos considerar que este margen de fase está aceptablemente próximo al deseado y dar por concluido el problema. Sin embargo, podemos plantearnos afinar un poco más el diseño del PD para conseguir un resultado algo mejor. Para ello, habría que intentar evitar que la frecuencia de corte se desplace tan a la derecha al introducir el PD. Bastaría con colocarla a una distancia menor de la media década antes. Por ejemplo, veamos qué ocurre colocándola en: 1 = 4 rad / s Td Con ello resultarían las curvas de magnitud y fase que aparecen en rojo. De acuerdo con la nueva gráfica de magnitud, la nueva frecuencia de corte se sitúa en los 6 rad/s, si calculamos la fase comprobamos que el margen de fase es incluso menor: M f ≈ 42 o En realidad, si buscamos analíticamente el valor de la magnitud a 6 rad/s, vemos que el corte con 0dB no se produce exactamente ahí, sino algo más atrás: C ( jw) G ( jw) w=6 = −2.34dB , C ( jw) G ( jw) w=5 = 0.24dB , Luego, la frecuencia de corte estará más cerca de 5 rad/s que de 6 rad/s. Si hacemos el cálculo del margen de fase a 5 rad/s: M f ≈ 48 o Con lo que, finalmente, conseguiremos cumplir todas las especificaciones. La expresión final del controlador es: C ( s ) = 1.35 (1 + s / 4) Por último, cabe indicar que este segundo intento de diseño, consistente en desplazar la “frecuencia de esquina” del PD a la derecha, no siempre tiene por qué dar un resultado mejor que el que se tenía. Ello es debido a que mientras más a la derecha esté el PD menor es el aporte de fase que se consigue con él. M.Vargas 2006