Sistemas secuenciales

Anuncio

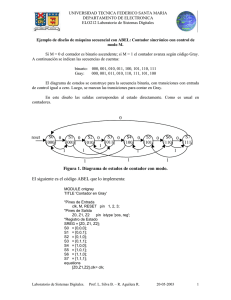

Electrónica Tema 6 Tema 1 Circuitos Secuenciales Fundamentos de semiconductores 1 Lógica secuencial Un circuito secuencial es aquel cuyas salidas dependen no sólo de las entradas actuales, sino también de las secuencias de entradas anteriores. El histórico de las secuencias de entradas anteriores se representa por el concepto de “estado”. 2 Lógica secuencial El estado de un circuito secuencial es un conjunto de variables que contienen toda la información acerca del comportamiento pasado del circuito, para determinar el comportamiento futuro del mismo. Un circuito con n variables de estado, tiene 2n estados posibles. 3 Lógica secuencial Los cambios de estado ocurren normalmente en ciertos instantes sincronizados por una señal de reloj. state changes occur here (a) CLK tH tL tper period = tper frequency = 1 / tper duty cycle = tH / tper state changes occur here (b) CLK_L tL tH tper Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e duty cycle = tL / tper 4 Lógica secuencial • Circuitos secuenciales con realimentación – Usan bucles para conseguir un efecto de “memoria”. – Bloques secuenciales: latches y biestables (flipflops). 5 Latches y Flip-Flops Los Latches y los Flip-Flops son los bloque básicos de los circuitos sencuenciales. Flip-Flop: Dispositivo secuencial que muestrea las entradas y cambia las salidad en ciertos instantes de tiempo determinados por una señal de reloj. Latch: Dispositivo secuencial que muestrea la entradas continuamente y cambia las salidas en cualquier momento. 6 Latches Latch S-R (Set-Reset) R (a) Q QN S S R 0 0 0 1 1 0 1 1 Q QN last Q last QN 0 1 0 1 0 0 (b) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (a) S Q S Q S Q R QN R Q R QN (b) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (c) 7 Latches Latch S-R con lógica inversa Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (a) S_L or S R_L (b) Q QN S_L R_L Q QN 0 0 1 1 0 1 1 0 1 1 0 1 (c) S Q R Q 0 1 last Q last QN or R 8 Latches Latch S-R con Enable Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (a) (b) S S R C Q QN Q 0 0 1 0 1 1 1 0 1 C QN R 1 1 1 x x 0 last Q last QN 1 0 0 1 1 (c) S Q C Q R 1 last Q last QN 9 Latches Latch J-K Es igual que un latch S-R, pero ahora la combinación de entrada “11” es válida, produciendo un cambio en el estado. “00”: Q last Q “01” : Q ‘0’ “10” : Q ‘1’ “11” : Q last QN 10 Latches Latch D D Q C QN (a) (b) C D Q QN 1 0 0 1 D Q 1 1 1 0 C Q 0 x last Q last QN (c) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e 11 Flip-Flops Flip-Flop D disparado por flanco Se construye con dos latches D Master-Slave Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (a) (b) D D C CLK Q QM D Q Q C Q QN (c) Q QN 0 0 1 1 1 0 D CLK x 0 last Q last QN x 1 last Q last QN D Q CLK 12 Q Flip-Flops Flip-Flop D disparado por flanco con Enable (a) (b) D EN CLK D EN D CLK CLK (c) Q Q Q QN Q QN 0 1 0 1 1 1 1 0 x 0 x x 0 last Q last QN x x 1 last Q last QN D Q EN CLK last Q last QN 13 Q Flip-Flops Flip-Flop T (Toggle) : Cambia su estado mediante una entrada T. Si T=1 cambia de estado, si T=0 no cambia de estado. Ejercicio. Usando un Flip-Flop D, diseñar: 1. Un Flip-Flop T 2. Un Flip-Flop T con Enable 14 Flip-Flops Flip-Flop T (b) (a) D 1 Q Q J T CLK QN Q Q Q Q QN CLK T K Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e EN T D CLK (a) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e Q Q EN T Q QN J Q Q Q QN CLK K (b) 15 Análisis de máquinas de estado síncronas • Máquina de estados: Nombre genérico para un circuito secuencial con realimentación. • Síncrona: Todos los elementos de almacenamiento responden a la misma señal de reloj. Los cambios de estado sólo ocurren en los flancos de reloj. 16 Estructura de una máquina de estados Máquina Mealey Next State = F(Current State, Input) Output = G(Current State, Input) inputs Next-state Logic excitation State Memory F current state Output Logic outputs G clock input clock signal Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e 17 Estructura de una máquina de estados Máquina Moore Next State = F(Current State, Input) Output = G(Current State) inputs Next-state Logic excitation State Memory F current state Output Logic outputs G clock input clock signal Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e 18 Ecuaciones características • Usadas para describir formalmente el comportamiento de los circuitos secuenciales. • Q* denota el próximo valor de Q. Por ejemplo, para un Flip-Flop D: Q* = D Ejercicios: a) Flip-Flop D con Enable, b) Latch S-R (asumiendo que S⋅R = 0) 19 Ecuaciones características 1. Flip-Flop D con Enable: Q* = EN⋅D+ EN´⋅Q 2. Latch S-R: Q* = S+R´⋅Q 20 Análisis de máquinas de estados con biestables D 1. Determinar las funciones F (Próximo Estado) y G (Salida). 2. Construir una tabla de Estado/Salida. 3. Dibujar un Diagrama de Estado que muestre gráficamente la información de la tabla. 21 Tabla de transición Ecuaciones de excitación: Expresan el valor de Di como una función del estado y entradas actuales. Qi* = Di Ecuaciones de transición: Expresan el valor del próximo estado como una función del estado y entradas actuales 22 Ejemplo Next-state Logic F State Memory Output Logic G output input MAX excitation EN EN D0 EN′ D CLK Q Q0 Q Q0 Q0′ D1 Q1 D CLK Q Q1 Q Q1′ clock signal CLK Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e current state 23 Ejemplo Ecuaciones de excitación: D0 = Q0⋅EN´+ Q0´⋅EN D1 = Q1⋅EN´+Q1´⋅Q0 ⋅EN+Q1⋅Q0´⋅EN Ecuaciones de transición: Q0* = Q0⋅EN´+ Q0´⋅EN Q1* = Q1⋅EN´+Q1´⋅Q0 ⋅EN+Q1⋅Q0´⋅EN 24 Ejemplo Tabla de transición (a) (b) EN (c) EN EN Q1 Q0 0 1 S 0 1 S 0 1 00 00 01 A A B A A, 0 B, 0 01 01 10 B B C B B, 0 C, 0 10 10 11 C C D C C, 0 D, 0 11 11 00 D D A D D, 0 A, 1 Q1∗ Q0∗ S∗ Table 7-2 Transition, state, and state/output tables for the state machine in Figure 7-38. S∗, MAX 25 Ejemplo Diagrama de Estado EN = 0 EN = 0 (MAX = 0) A EN = 1 (MAX = 0) B (MAX = 0) EN = 1 EN = 1 (MAX = 1) (MAX = 0) D EN = 0 (MAX = 0) EN = 1 (MAX = 0) C EN = 0 (MAX = 0) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e 26 Ejemplo Diagrama de Estado para una Máquina Moore EN = 0 EN = 0 A EN = 1 MAXS=0 B MAXS=0 EN = 1 EN = 1 D MAXS=1 EN = 0 EN = 1 C MAXS=0 EN = 0 Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e 27 Análisis de máquinas de estados 1. Determinar las ecuaciones de excitación para los flipflops. 2. A partir de las ecuaciones de excitación, obtener las ecuaciones de transición. 3. Construir la tabla de transición. 4. Determinar las ecuaciones de salida. 5. Determinar la tabla de Estado/Salida. 6. Dibujar el diagrama de estados. 28 Diseño de máquinas de estados 1. 2. 3. 4. 5. 6. 7. 8. Construir la tabla de Estado/Salida. Minimizar el número de estados. Escoger un conjunto de variables y asignar combinaciones a los estados. Crear la tabla de Transición/Salida. Escoger un tipo de flip-flop. Construir la tabla de excitación y derivar las ecuaciones. Obtener las ecuaciones de salida. Dibujar el diagrama lógico. 29 Diseño de máquinas de estados Ejemplo • Diseñar una máquina de estados síncrona con dos entradas A y B, y una única salida Z. La salida Z es 1 si y sólo si: 1. A ha tenido el mismo valor en los dos ciclos de reloj anteriores. 2. B es 1 desde la última vez que se cumplió la primera condición. 30 Diseño de máquinas de estados Ejemplo AB (a) Meaning Initial state S 00 01 AB (b) 11 10 INIT Meaning Z Initial state 0 S 00 01 11 10 Z INIT A0 A0 A1 A1 0 0 0 11 10 Z 0 0 0 1 ... Got a 0 on A A0 ... Got a 1 on A A1 ... S∗ S∗ AB (c) Meaning Initial state Got a 0 on A Got a 1 on A Got two equal A inputs S 00 01 11 10 Z 0 0 0 1 INIT A0 A0 A1 A1 A0 OK OK A1 A1 A1 OK S∗ AB (d) Meaning Initial state Got a 0 on A Got a 1 on A Got two equal A inputs S 00 01 INIT A0 A0 A1 A1 A0 OK OK A1 A1 A1 OK A0 A0 OK OK S∗ 31Hall, Inc. Copyright © 2000 by Prentice Digital Design Principles and Practices, 3/e Diseño de máquinas de estados Ejemplo (a) AB Meaning Initial state Got a 0 on A Got a 1 on A Got two equal A inputs S 00 01 11 10 Z 0 0 0 1 INIT A0 A0 A1 A1 A0 A1 OK A0 OK A0 A1 OK A1 OK OK ? OK OK ? (b) AB Meaning Initial state S 00 INIT A0 A1 A0 A0 OK0 A0 OK0 A0 Got a 0 on A Got a 1 on A Two equal, A=0 last OK0 Two equal, A=1 last OK1 01 11 S∗ (c) Initial state Got a 0 on A Got a 1 on A Two equal, A=0 last Two equal, A=1 last S 00 01 11 10 Z INIT A0 A0 A1 A1 A0 A1 OK0 A0 OK0 OK0 A0 OK0 A1 OK1 OK1 A1 OK1 A1 0 0 0 1 1 OK0 OK1 S∗ Z A1 A1 A1 OK1 A1 OK1 0 0 0 1 1 S∗ AB Meaning 10 (d) AB Meaning S 00 01 11 10 Z INIT A0 A0 A1 A1 A0 A1 OK0 A0 OK0 A0 A1 OK1 A1 OK1 Two equal, A=0 last OK0 OK0 OK0 OK1 A1 Two equal, A=1 last OK1 A0 OK0 OK1 OK1 0 0 0 1 1 Initial state Got a 0 on A Got a 1 on A S∗ Copyright © 2000 by Prentice Hall, Inc. 32 Digital Design Principles and Practices, 3/e Diseño de máquinas de estados Minimización de estados • • Eliminar estados equivalentes. Dos estados S1 y S2 son equivalentes si, para todas y cada una de las combinaciones de entradas: – – Producen las mismas salidas Transitan a los mismos estados 33 Diseño de máquinas de estados Asignación de estados • Determinar el número de variables binarias. – • Si tenemos s estados, necesitamos log2(s) variables. Codificar cada estado con combinaciones de estas variables binarias. 34 Diseño de máquinas de estados Asignación de estados: Distintas posibilidades Assignment State Name Simplest Q1–Q3 Decomposed Q1–Q3 One-hot Q1–Q5 Almost One-hot Q1–Q4 INIT 000 000 00001 0000 A0 001 100 00010 0001 A1 010 101 00100 0010 OK0 011 110 01000 0100 OK1 100 111 10000 1000 Table 7Possible st assignmen state mach Table 7-6. 35 Diseño de máquinas de estados Tabla de Excitación / Transición • Una vez codificados los estados, construir la tabla de transición a partir de la tabla de estados. • Si se usan flip-flops D, como Q* = D, entonces la tabla de transición coincide con la de excitación. 36 Diseño de máquinas de estados Ejemplos AB Q1 Q2 Q3 00 01 11 10 Z 000 100 100 101 101 0 100 110 110 101 101 0 101 100 100 111 111 0 110 110 110 111 101 1 111 100 110 111 111 1 Ta bl e 7 - 8 Transition and output table for example problem. Tabla de transición / salida Q1∗ Q2∗ Q3∗ Ta bl e 7 - 9 Excitation and output table for Table 7-8 using D flip-flops. Tabla de excitación / salida AB Q1 Q2 Q3 00 01 11 10 Z 000 100 100 101 101 0 100 110 110 101 101 0 101 100 100 111 111 0 110 110 110 111 101 1 111 100 110 111 111 1 D1 D2 D3 37 Diseño de máquinas de estados Ejemplo D1 A AB 00 01 11 10 00 1 1 1 1 01 d d d d Q2 Q3 A AB 00 01 11 10 00 1 1 1 1 01 1 1 1 1 11 1 1 1 1 10 1 1 1 1 Q2 Q3 1 Q3 11 d d d d 10 d d d d Q3 Q2 Q2 Q1=0 D2 A AB 00 01 11 10 00 0 0 0 0 01 d d d d Q2 Q3 A AB D3 00 01 11 10 00 1 1 0 0 01 0 0 1 1 Q2 Q3 Q3 11 d d d d 10 d d d d Q1=1 A AB 00 01 11 10 00 0 0 1 1 01 d d d d Q2 Q3 11 0 1 1 1 10 1 1 1 0 B A AB 00 01 11 10 00 0 0 1 1 01 0 0 1 1 11 0 0 1 1 10 0 0 1 1 Q2 Q3 A Q3 Q3 Q2 Q2 Q1 • Q3′ • A′ B Q3 • A 11 d d d d 10 d d d d Q3 Q2 Q2 Q2 B • Q1=0 B Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e Q1=1 B Q1=0 B Q1=1 B 38 Diseño de máquinas de estados Ejemplo Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e 1 D1 D Q Q1 CLK Q CLR Q1 Q3′ A′ D2 Q3 A D Q Q2 Z CLK Q CLR A Q2 B B D3 D Q Q3 CLK Q CLR RESET_L CLK 39