Ejercicios sobre instrucciones y direccionamiento

Anuncio

Ejercicios sobre instrucciones y

direccionamiento

• Siguiente: Ejercicios sobre periféricos y ADM

• Padre: Materiales didácticos

• Inicial: Fundamentos de ordenadores

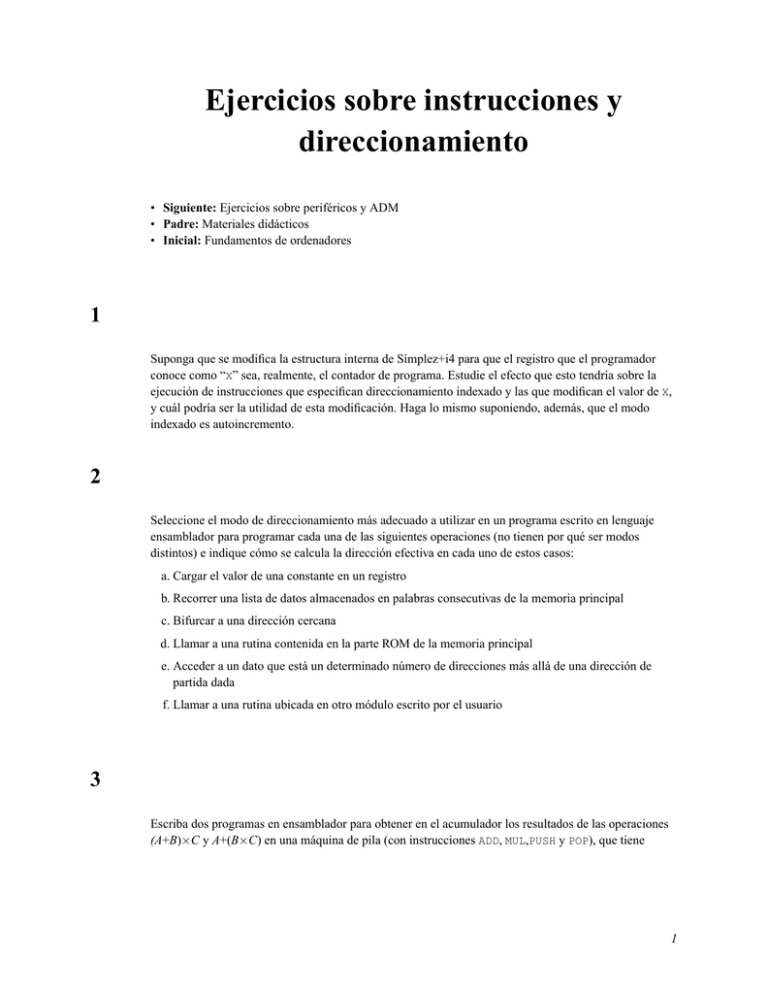

1

Suponga que se modifica la estructura interna de Símplez+i4 para que el registro que el programador

conoce como “X” sea, realmente, el contador de programa. Estudie el efecto que esto tendría sobre la

ejecución de instrucciones que especifican direccionamiento indexado y las que modifican el valor de X,

y cuál podría ser la utilidad de esta modificación. Haga lo mismo suponiendo, además, que el modo

indexado es autoincremento.

2

Seleccione el modo de direccionamiento más adecuado a utilizar en un programa escrito en lenguaje

ensamblador para programar cada una de las siguientes operaciones (no tienen por qué ser modos

distintos) e indique cómo se calcula la dirección efectiva en cada uno de estos casos:

a. Cargar el valor de una constante en un registro

b. Recorrer una lista de datos almacenados en palabras consecutivas de la memoria principal

c. Bifurcar a una dirección cercana

d. Llamar a una rutina contenida en la parte ROM de la memoria principal

e. Acceder a un dato que está un determinado número de direcciones más allá de una dirección de

partida dada

f. Llamar a una rutina ubicada en otro módulo escrito por el usuario

3

Escriba dos programas en ensamblador para obtener en el acumulador los resultados de las operaciones

(A+B)×C y A+(B×C) en una máquina de pila (con instrucciones ADD, MUL,PUSH y POP), que tiene

1

Ejercicios sobre instrucciones y direccionamiento

también instrucciones de acceso a una memoria de acceso aleatorio (LD /A, etc.) en la que se encuentran

los operandos (A está en la dirección A, etc.)

4

Escriba las operaciones de transferencia entre los registros PP y CP que tienen lugar para las

instrucciones CALL y RET en una máquina que utiliza una pila simulada en la MP para las direcciones de

retorno.

5

Parte del modelo procesal de Símplez con pila puede ser así:

(I0)

(I1)

0 -> CP,RA; ?

repetir siempre

(MP[RA]) -> RI; (CP)+1 -> CP

si (CO) es

CLR: 0 -> AC; (CP) -> RA

...

{otras instrucciones}

CALL: ?

(OCALL0)

?

(OCALL1)

?

RET:

?

(RET0)

?

(RET1)

?

Sustituya las “?” con las expresiones de transferencias entre registros adecuadas. Recuerde que el fondo

de la pila está en la dirección 507 y que el convenio es que el puntero de pila, PP, apunte a la cima.

(Naturalmente, hay que suponer que existen el registro PP y los caminos y circuitos necesarios en la ruta

de datos para realizar las operaciones).

2

Ejercicios sobre instrucciones y direccionamiento

6

Imagine que medimos los tiempos de ejecución, en milisegundos, de cuatro UCP, U1, U2, U3 y U4,

ejecutando dos programas, P1 (que ejecuta 1.000 instrucciones) y P2 (que ejecuta 10.000), y obtenemos

los siguientes resultados:

P1

P2

U1

1

10

U2

10

16

U3

1

40

U4

2

5

Calcule las velocidades medias, en MIPS, de las cuatro UCP, suponiendo:

a. Que la carga de trabajo se distribuye uniformemente entre P1 y P2 (es decir, ambos se ejecutan el

mismo número de veces)

b. Que la carga de trabajo es tal que de cada diez programas que se ejecutan uno es P2 y nueve P1

¿Puede identificar la más rápida y la más lenta de las cuatro UCP?

7

Considere una UCP con una frecuencia de reloj de 100 MHz que tiene tres tipos de instrucciones:

tipo

ciclos por instrucción

I1

CPI = 1

I2

CPI = 2

I3

CPI = 3

Por otra parte, tenemos dos compiladores, CA y CB, que, traduciendo un mismo programa fuente, nos han

generado dos códigos objeto con distintas mezclas de instrucciones para esta UCP. En millones de

instrucciones a ejecutar, estas mezclas han resultado ser:

CA

I1

I2

I3

2

4

10

3

Ejercicios sobre instrucciones y direccionamiento

CB

I1

32

I2

6

I3

2

Se trata de averiguar cuál de los dos compiladores está más optimizado para esta UCP (y este programa).

Para ello, calcule:

a. La velocidad de la UCP en MIPS en función del compilador

b. El tiempo real de ejecución de cada uno de los programas objetos

8

En los procesadores Pentium (arquitectura IA-32) hay registros de propósito general y registros para

funciones diversas. En la Figura 1 se presentan los más importantes, de los cuales, y a efectos de estos

ejercicios, sólo nos vamos a fijar en los ocho de propósito general (de 32 bits) y en los seis de segmento

(de 16 bits), cuyos nombres aparecen en la Figura 2. La primera figura también muestra el espacio de

direccionamiento de la MP, de 232 bytes (4 GB) (que puede extenderse a 64 GB con un mecanismo que

4

Ejercicios sobre instrucciones y direccionamiento

no veremos aquí).

Figura 1. Registros de la IA-32

5

Ejercicios sobre instrucciones y direccionamiento

Figura 2. Registros de propósito general y de segmento de la IA-32

La UCP tiene tres modos de operación, llamados “protegido” (o “nativo”), “real-address” (para

compatibilidad con 8086) y “de gestión” (para ciertas funciones de los sistemas operativos). En estos

ejercicios nos referimos al primero. También hay tres modelos de memoria: “segmentada”, “plana” y

“real-address”, y nos referimos al primero.

Sólo hay tres modos de direccionamiento de operandos, aunque el tercero es muy flexible:

•

inmediato (operando en la instrucción)

•

registro (operando en un registro de propósito general, RPG)

•

base/indexado, en el que la dirección efectiva es, en general:

DE = base + factor×índice + desplazamiento

donde “base” es el contenido de uno de los RPG, “factor” está especificado en la instrucción, y puede

ser 1, 2, 4 u 8, “índice” es otro de los RPG, y “desplazamiento” está especificado en la instrucción (en

un campo “CD”). La instrucción también especifica los registros que actúan como base e índice.

Cualquiera de estos componentes puede estar presente o no, de acuerdo con convenios seguidos en el

formato de instrucciones

El tercer modo, al poder combinar entre una y cuatro informaciones, es aplicable a diversas necesidades.

Razone (pensando como un diseñador del compilador, es decir, teniendo en cuenta las estructuras de

6

Ejercicios sobre instrucciones y direccionamiento

datos habituales en los lenguajes de alto nivel) para qué pueden servir cada una de estas combinaciones:

a. desplazamiento (es decir, no se usa registro de base ni de índice)

b. base (sin considerar índice ni desplazamiento)

c. base + desplazamiento

d. (factor×índice) + desplazamiento

e. base + índice + desplazamiento

f. base + (factor×índice) + desplazamiento

9

El formato de instrucciones de la arquitectura IA-32 (Figura 3, “Figure 2-1” de la documentación

original de Intel) es bastante complejo (como corresponde a un CISC cuyo diseño ha ido evolucionando

bajo las restricciones de compatibilidad con arquitecturas anteriores). Una instrucción ocupa entre uno y

16 bytes, dependiendo de su código de operación, y de si tiene o no “prefijos” (bytes que modifican de

varias maneras lo que hace la instrucción).

Figura 3. Formato de instrucciones de la IA-32

Suponga una instrucción sin prefijos, con un código de operación binario de un solo byte que

corresponde a “mover palabra (32 bits)”, que en el siguiente byte (ModR/M) especifica que se trata de

mover de memoria al registro EAX con un modo de direccionamiento que debe considerar tanto el byte

SIB como un campo de desplazamiento de 16 bits, y que tiene (SIB) = H’8A y (desplaz.) = H’000A.

•

¿Cuál será la dirección efectiva? Para dar una respuesta concreta, suponga que inmediatamente antes

de ejecutarse esta instrucción los contenidos de los RPG son: (EAX) = H’00000000; (EBX) =

H’0000000F; (ECX) = H’000000FF; etc. Estos registros se codifican en binario en el byte SIB como

000, 001, etc. Los factores de escala, 1, 2, 4, 8, se codifican como 00, 01, 10 y 11, respectivamente

7

Ejercicios sobre instrucciones y direccionamiento

10

En modo protegido y memoria segmentada, lo que en los dos ejercicios anteriores hemos llamado

“dirección efectiva” no es, en realidad, la dirección final en la memoria física, sino una dirección relativa

a segmento. En la terminología de Intel, esta dirección relativa se llama offset, el contenido del registro

de segmento que se use junto con el offset se llama “dirección lógica”, y la dirección definitiva de la MP,

“dirección lineal”. Por defecto, el registro de segmento que se usa para acceso a datos es “DS”, para

aceso a pila, “SS” (stack segment), y para leer la siguiente instrucción, “CS” (code segment). Los otros

tres registros de segmento pueden utilizarse para estructuras de datos adicionales, como indica la Figura

4.

Figura 4. Uso de los registros de segmento en el modelo de memoria segmentado

Ahora bien, la traducción de la dirección lógica a dirección lineal no se hace combinando directamente el

contenido del registro de segmento con el offset (como indica la figura 4.9 del libro, y como se hacía en

el 8086). Hay otros registros (que no aparecen en la Figura 1) cuyos contenidos determinan la ubicación

en la MP de varias tablas que contienen datos para el cálculo de esa dirección lineal. Concretamente,

GDTR (Global Descriptor Table Register) contiene la dirección (y el tamaño) de una “tabla de

descriptores globales”. Su formato (junto con el de IDTR, que contiene la dirección y el tamaño de una

tabla de vectores de interrupción) es el de la Figura 5

8

Ejercicios sobre instrucciones y direccionamiento

Figura 5. Registros de tablas del sistema

El contenido de un registro de segmento se llama “selector de segmento” y, combinado con la dirección

de base de la tabla, determina la dirección en la MP del “descriptor de segmento” que, entre otras cosas,

contiene la dirección de base del segmento a sumar al offset para obtener la dirección lineal de la MP.

Las Figuras 6 y 7 muestran este cálculo (ambas figuras dan la misma información; tenga en cuenta que el

convenio de Intel para los mapas de memoria es el contrario al que seguimos en el curso: la dirección 0

está abajo y la más alta, H’FFFFFFFF, arriba):

Figura 6. Cálculo de la dirección lineal

9

Ejercicios sobre instrucciones y direccionamiento

Figura 7. Cálculo de la dirección lineal

La Figura 8 muestra el formato de un descriptor de segmento, que ocupa 8 bytes (dos palabras):

10

Ejercicios sobre instrucciones y direccionamiento

Figura 8. Formato del descritor de segmento

Los descriptores se almacenan en la memoria con un convenio extremista menor, es decir:

dirección d:

dirección d+1:

dirección d+2:

...

dirección d+7:

límite 7..0 (8 bits menos significativos)

límite 15..8

base 7..0

...

base 31..24

De entre las informaciones codificadas cabe destacar:

•

Dirección de base del segmento: 32 bits

•

Límite (longitud de este segmento): 20 bits. La unidad en que se mide depende del bit G

(granularidad): si G = 0, es el número total de bytes; si G = 1 es el número de “trozos” de 4 KB

•

Tipo: 4 bits. Determina si es un segmento de código o de datos, si es de lectura y escritura o de sólo

lectura, etc.

•

DPL (descriptor privilege level): 2 bits. El procesador contempla cuatro niveles de privilegio. Los

11

Ejercicios sobre instrucciones y direccionamiento

procesos (programas en ejecución) sólo pueden acceder a segmentos que tengan un nivel igual o

inferior al suyo (si intentan acceder a un nivel superior se genera una interrupción, trap). El nivel 0 es

el de máxima prioridad, y el 3 el de mínima

Finalmente, hay que aclarar que el selector de segmento (contenido de un registro de segmento) no se

suma directamente con la dirección de base de la tabla de descriptores para obtener la dirección del

descriptor. El formato de un selector de segmento es el indicado en la Figura 9,

Figura 9. Formato del selector de segmento

donde:

•

“RPL” es el nivel de privilegio del selector (el procesador lo compara con el nivel de privilegio del

descriptor para asegurarse de que un proceso no intenta acceder a un segmento que tenga un privilegio

mayor). El RPL del registro CS (Code Segment) determina el nivel de privilegio del programa que se

está ejecutando (CPL: Current Privilege Level). Pero si una instrucción de ese programa intenta

acceder a la memoria (por ejemplo, a un segmento de datos determinado por el registro DS) y el RPL

del registro de segmento correspondiente (DS) es mayor (menos prioridad) que el CPL entonces CPL

queda sustituido por el RPL del registro DS

•

“TI” es un bit indicador de tabla: si TI = 0 se selecciona la GDT, si TI = 1 se selecciona otra distinta, la

LDT (Local Descriptor Table), cuya dirección de base y límite están en otro registro, LDTR.

•

“Index” selecciona un descriptor en la GDT o la LDT. El procesador multiplica el valor del índice por

8 (el número de bytes en un descriptor de segmento) y suma el resultado a la dirección de base de la

GDT o la LDT (contenida en GDTR o LDTR, respectivamente)

De acuerdo con todo esto,

a. ¿Qué tamaño máximo puede tener la GDT?

b. ¿Cuántos descriptores puede contener la GDT?

c. ¿Cuál es el tamaño máximo de un segmento?

d. En el ejercicio anterior habíamos calculado el offset para una instrucción que cargaba una palabra en

el registro EAX. Suponga que en el momento de ejecutarse esta instrucción,

12

Ejercicios sobre instrucciones y direccionamiento

•

(GDTR) = H’00000000FF

•

(DS) = H’001A

•

Los 256 primeros bytes de la memoria tienen contenidos que coinciden con sus direcciones, es

decir, (MP[0]) = 00, (MP[1]) = 01,... (MP[255]) = H’FF

¿Cuál sería la dirección final (la “dirección lineal”) del operando a cargar en EAX? Por los datos que

conocemos, ¿hay algo que impida que se ejecute esta instrucción?

e. El paso del sencillo esquema del 8086 a esta idea de que los registros de segmento direccionen

tablas en memoria con una diversidad de informaciones se planteó ya en el diseño del

microprocesador Intel 80286. ¿Qué ventaja tiene este esquema que pueda justificar su complejidad?

f. Pero aparte de esta ventaja, el esquema, tal como lo hemos presentado, tiene un grave inconveniente.

¿Cuál es? ¿Cómo puede resolverse? (si encuentra tanto el inconveniente como la solución dada por

los diseñadores de Intel se merece una calificación de Matrícula en la asignatura; no podemos

comprobarlo, pero puede servirle como satisfacción personal)

11

Los modos de direccionamiento genéricos descritos en el ejercicio 8 son para el acceso a operandos. Las

instrucciones de transferencia de control, JMP (BR en nuestra notación de ensamblador), CALL, RET, INT

(BRK) e IRET (RETI) (incondicionadas, o condicionadas al valor de algún indicador) admiten también

modos relativos a programa (desplazamiento positivo o negativo con respecto al contador de programa) y

a segmento (desplazamiento a sumar a la dirección de base del segmento de código). Estos modos (con

distintas variantes: bifurcaciones “cortas”, con un desplazamiento de 8 bits, “largas”, con desplazamiento

de 32 bits, etc.) son los más utilizados en estas instrucciones.

a. ¿Cuándo será necesario utilizar los modos genéricos para las instrucciones de transferencia de

control?

b. ¿Qué valores deberá guardar CALL en la pila?

• Siguiente: Ejercicios sobre periféricos y ADM

• Padre: Materiales didácticos

• Inicial: Fundamentos de ordenadores

13