Módulo 4

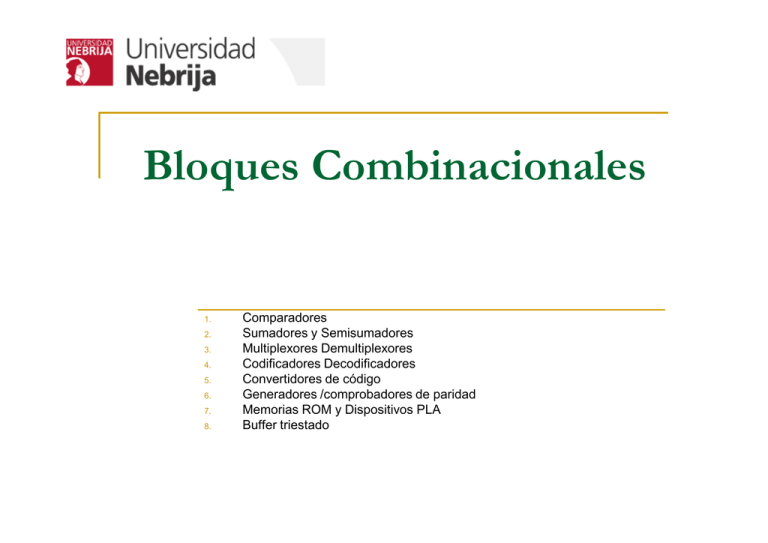

Anuncio

Bloques Combinacionales 1. 2. 3. 4. 5. 6. 7. 8. Comparadores Sumadores y Semisumadores Multiplexores Demultiplexores Codificadores Decodificadores Convertidores de código Generadores /comprobadores de paridad Memorias ROM y Dispositivos PLA Buffer triestado Circuitos combinacionales Cuando se conectan puertas lógicas entre sí, sin que haya almacenamiento, el circuito resultante se califica como combinacional. Dr. Oscar Ruano 2011-2012 ¿Por qué módulos estándar? Cualquier sistema combinacional puede implementarse como un sistema de 2 niveles: AND-OR Teóricamente es posible implementar cualquier sistema recurriendo a este modelo sistemático Utilizar esto para sistemas complejos, es muy costoso en tiempo y a veces imposible de implementar una network de 2 niveles debido a propiedades inherentes en las puertas lógicas: FAN IN: define el máximo número de inputs que una puerta lógica puede aceptar FAN OUT: define el máximo número de inputs que la salida de una puerta lógica puede alimentar. Estos motivos hacen que los sistemas complejos se implemente de forma jerárquica o modular. Dr. Oscar Ruano 2011-2012 Comparadores Comparador Básico Dr. Oscar Ruano 2011-2012 Especificación de un comparador Especificación en alto nivel Codificación: Dr. Oscar Ruano 2011-2012 Especificación de un comparador Función: Ecuación: Dr. Oscar Ruano 2011-2012 Sumadores y Semisumadores Suma de dos números Dr. Oscar Ruano 2011-2012 Sumadores y Semisumadores Ecuación: Dr. Oscar Ruano 2011-2012 Sumadores y Semisumadores Dr. Oscar Ruano 2011-2012 Semisumador elemental El semisumador (half adder) es un circuito que suma dos bits de entrada ai y bi y devuelve un bit de resultado zi y un bit de acarreo ci. Dr. Oscar Ruano 2011-2012 Sumador completo El sumador completo (full adder) es un circuito que suma dos bits de entrada ai y bi más un acarreo de entrada ci-1 y devuelve un bit de resultado zi y un bit de acarreo ci Dr. Oscar Ruano 2011-2012 Sumador completo (full adder) BCin 00 01 11 10 0 0 1 1 0 11 1 1 0 11 0 BCin 00 01 11 10 0 0 0 1 0 1 0 1 1 1 A A ∑ = ABC + ABC + ABC + ABC = ( ) ( ) = C ( A ⊕ B ) + C (A ⊕ B ) = ( A ⊕ B ) ⊕ C = C AB + AB + C AB + AB = Cout = AB + ACin + BCin Cout = AB + ABCin + A BCin = ( ) = AB + Cin AB + AB = = AB + Cin( A ⊕ B ) Dr. Oscar Ruano 2011-2012 Sumador completo compuesto de semisumadores Dr. Oscar Ruano 2011-2012 Sumador en paralelo de 4 bits (nibble) Un sumador de 4 bits se implementa mediante 4 full adders. Dependiendo del método elegido para manejar los acarreos el sumador puede ser acarreo serie acarreo anticipado Dr. Oscar Ruano 2011-2012 Ejemplo de aplicación Dr. Oscar Ruano 2011-2012 Sumador paralelo con acarreo serie Se construye asociando n sumadores elementales completos (full adder) que reciben y procesan todos ellos los datos en paralelo, si bien el acarreo se propaga en serie de un sumador a otro (circuito lento) Dr. Oscar Ruano 2011-2012 Ejemplo de retardo acarreo serie Dr. Oscar Ruano 2011-2012 El tiempo de retardo considerado es el tiempo de suma del caso peor Sumador de acarreo anticipado Dr. Oscar Ruano 2011-2012 Sumador de acarreo anticipado El sumador Paralelo con Acarreo Anticipado (Look Ahead Carry, LAC) es muy rápido porque evita el overhead de propagación del acarreo a costa de una penalización en área. No se basa en las ecuaciones directas para Ci+1 y Si, sino en dos funciones adicionales llamadas de generación (Gi) y de propagación (Pi), para cada bit ‘i’ (i = 0, 1, 2…) Generación de Acarreo: tiene lugar cuando el sumador completo genera internamente un acarreo de salida. Solo cuando ambos bits son 1 se genera acarreo Gi = AiBi Propagación de Acarreo: tiene lugar cuando el acarreo de entrada se transmite como acarreo de salida. Solo cuando un de los bits de entrada es 1 se propaga el acarreo i i i P = A ⊕B Dr. Oscar Ruano 2011-2012 Sumador de acarreo anticipado La limitación mas importante es que a medida que aumenta el número de etapas (bits), la ecuación de acarreos se hace más larga aumentando así la complejidad del sistema. Dr. Oscar Ruano 2011-2012 Sumador de acarreo anticipado Dr. Oscar Ruano 2011-2012 Sumador/restador binario para números de 4 bits en Ca2 Para números en complemento a 2, la substracción se implementa con el mismo hardware, negado el sustraendo; el 1 se suma poniendo a 1 el acarreo inicial Dr. Oscar Ruano 2011-2012 Generación del segundo operando Dr. Oscar Ruano 2011-2012 Sumador/restador de 16 bits en ca2 Dr. Oscar Ruano 2011-2012 Sumador BCD Suma números codificados en BCD y genera otro BCD Dr. Oscar Ruano 2011-2012 Decodificadores Dr. Oscar Ruano 2011-2012 Decodificador de n entradas Dr. Oscar Ruano 2011-2012 Decodificador de 2 entradas Dr. Oscar Ruano 2011-2012 Decodificador 4 bits Salida Activa a nivel Bajo Dr. Oscar Ruano 2011-2012 Codificadores Dr. Oscar Ruano 2011-2012 Codificadores: Decimal-BCD Dr. Oscar Ruano 2011-2012 Convertidores de Código Los convertidores de código son circuitos lógicos combinacionales que permiten el paso de un código a otro. Dr. Oscar Ruano 2011-2012 Convertidores de Código Dr. Oscar Ruano 2011-2012 Conversor BCD a 7-segmentos Dr. Oscar Ruano 2011-2012 Conversor BCD a decimal Un decodificador BCD a decimal convierte el código BCD en uno de los 10 posibles dígitos decimales. Dr. Oscar Ruano 2011-2012 Multiplexor de 2n entradas Dr. Oscar Ruano 2011-2012 Multiplexor de 2 a 1 Dr. Oscar Ruano 2011-2012 Multiplexor de 2 a 1 Dr. Oscar Ruano 2011-2012 Multiplexor de 2 a 1 Dr. Oscar Ruano 2011-2012 Multiplexores 4 a 1 Y = D0S1’S0’+ D1S1’S0+ D2S1S0’+ D3S1S0 Dr. Oscar Ruano 2011-2012 Multiplexor como generador de funciones lógicas Sirven para generar funciones lógicas combinacionales en forma de Suma de Productos Dr. Oscar Ruano 2011-2012 Demultiplexores (DEMUX) Dr. Oscar Ruano 2011-2012 Generadores y comprobadores de paridad Dr. Oscar Ruano 2011-2012 Generadores y comprobadores de paridad Paridad Par: PO = I 0 ⊕ I1 Paridad Impar: PE = ( PO)' = ( I 0 ⊕ I1)' Dr. Oscar Ruano 2011-2012 Memorias ROM Tipos de memoria: Mask-programmed ROM EPROM (erasable programmable ROM) Se graba con un programador Se borra con luz ultravioleta EEPROM (electrically erasable PROM) Los datos son permanentes Económicamente posible en grandes cantidades debido al alto coste del diseño Se borra con pulsos eléctricos Se pudee reprogramar 100 a 1000 veces Flash memoria Similar a EEPROM pero se puede escribir sin necesidad de programador Dr. Oscar Ruano 2011-2012 Líneas externas de una ROM Líneas de datos Dr. Oscar Ruano 2011-2012 Tabla de datos Dr. Oscar Ruano 2011-2012 Almacenamiento de la información Dr. Oscar Ruano 2011-2012 Estructura de una ROM Dr. Oscar Ruano 2011-2012 Estructura de una ROM Dr. Oscar Ruano 2011-2012 Bloques de una ROM Dr. Oscar Ruano 2011-2012 Programmable-Logic-Arrays (PLAs) Módulo combinacional que proporciona una implementación NOT-AND-OR para generación de funciones. Por niveles: NOT: provee la capacidad de complementar las distintas señales de input AND: provee la capacidad de generar los productos OR: provee la capacidad de generar las sumas Una PLA por lo tanto implementa sumas de productos Como en el caso de las ROMs la programación de una PLA puede hacerse durante el proceso de fabricación (mask-programmed PLA) o bien sobre el “field” (field-programmable PLA o FPLA) Dr. Oscar Ruano 2011-2012 Estructura de una PAL NOTA: Los puntos fuertes de la figura indican aquellas conexiones que han sido programadas para una determinada función Dr. Oscar Ruano 2011-2012 Buffer tri-estado http://www.cs.umd.edu/class/spring2003/cms c311/Notes/CompOrg/tristate.html Dr. Oscar Ruano 2011-2012