Compuertas Lógicas

Anuncio

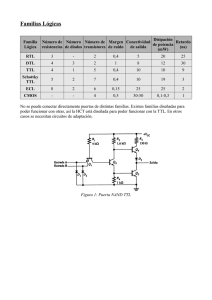

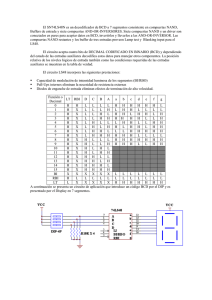

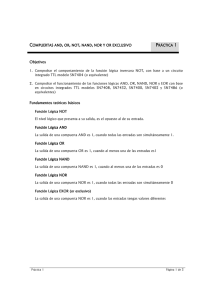

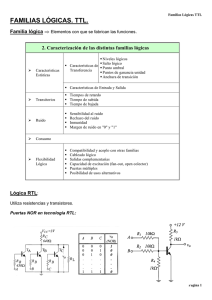

Compuertas lógicas Compuertas Lógicas Circuito básico Mario Medina C. [email protected] n≥1 entradas binarias 1 o más salidas binarias Implementa una función lógica de las entradas Dispositivos físicos que representan las operaciones binarias estudiadas Eléctricos Hidráulicos Mecánicos Ejemplos de sumadores binarios Tubos al vacío Hecho en cartón Compuertas lógicas Hecho en madera Usuario ve la compuerta como caja negra Hecho con Legos Ejemplo: sumador LEGO Hecho en metal Sólo importa su comportamiento de salida No necesita conocer funcionamiento interno Conocer las condiciones de operación Toda expresión booleana puede implementarse físicamente mediante la interconexión de puertas lógicas La representación de los elementos interconectados se conoce como esquemático. Compuertas lógicas Puerta lógica AND Puertas lógicas básicas AND: intersección o producto lógico OR: unión o suma lógica NOT: complemento o inversión NAND y NOR: basadas en las anteriores XOR: OR exclusivo NEXOR: equivalencia o NOT XOR Buffers: acopladores © 2014 Mario Medina C. f = A*B Símbolos más usados Simbología militar o distintiva Simbología rectangular o europea 1 Puerta lógica OR Puertas AND de más entradas La compuerta anterior puede extenderse a más variables f = A*B*C*D f=A+B Diferencia conceptual y funcional entre producto lógico (AND) y suma lógica (OR), y sus pares aritméticos, ^ y v. 7 Puerta lógica NOT Puerta lógica NAND f = A’ f = (A*B)’ = A’ + B’ Triángulo + burbuja AND con salida negada Triángulo: función acopladora (buffer) Burbuja: función de inversión o complementación OR con entradas negadas Otras notaciones A|B (Sheffer Stroke) AB (Sheffer Stroke) Henry M. Sheffer (1882 – 1964) Puerta lógica NAND NAND es más común que AND Más fácil de fabricar Eléctricamente más conveniente NAND es conjunto funcionalmente completo Es posible construir otras compuertas lógicas utilizando solamente compuertas NAND Puerta lógica NOR f = (A + B)’ = A’*B’ OR con salida negada AND con entradas negadas Otras notaciones AB (Peirce Arrow) A†B (Quine Dagger) Charles S. Peirce (1839 – 1914) © 2014 Mario Medina C. 2 Puerta lógica XOR f = A⊕B = A’B + AB’ Salida es 1 si las entradas son diferentes Operador de desigualdad Salida es 1 si paridad es impar XOR de 2 entradas es común Puerta lógica NEXOR Salida es 1 si las entradas son iguales Operador de equivalencia Llamado también XNOR, NXOR Salida es 1 si paridad es par Posible XOR de 3 o más entradas, pero es raro Puerta buffer f = A≡B = AB + A’B’ f=A Conjuntos funcionalmente completos Conjunto funcionalmente completo Salida es igual a la entrada Compuerta mejora características eléctricas de la señal Aumenta la corriente Mejora las transiciones 0→1 y 1→0 Operadores pueden implementar cualquier función de conmutación Conjunto {AND, OR y NOT} es funcionalmente completo Pero, AND es OR con entradas y salida negadas Y, OR es AND con entradas y salida negadas Entonces, conjunto {OR, NOT} es completo También lo es {AND, NOT} Conjuntos funcionalmente completos Conjuntos funcionalmente completos NOR con ambas entradas unidas es un NOT NAND con ambas entradas unidas es NOT Las funciones {NAND} y {NOR} son, cada una, conjuntos funcionalmente completos Toda función de conmutación puede implementarse usando sólo compuertas NAND ó compuertas NOR © 2014 Mario Medina C. Importancia de conjuntos funcionalmente completos y equivalencias entre funciones No disponibilidad de uno o varios tipos de puertas lógicas X ó X’ disponibles,pero no ambas Requerimientos eléctricos específicos Costos de implementación Menor número de puertas generalmente no implica simplicidad de implementación 3 Equivalencias entre puertas AND + NOT OR + NOT Lógica positiva y negativa NOR NAND AND En la práctica, compuertas lógicas no funcionan con 0s y 1s Manuales de fabricantes especifican niveles lógicos de voltajes H y L Lógica positiva asume que H = 1 y L = 0 Lógica negativa asume que H = 0 y L = 1 Interpretación de H y L asigna funciones lógicas diferentes al mismo circuito OR NAND NOR Lógica positiva y negativa Lógica positiva y negativa Fabricantes expresan el comportamiento físico real El usuario interpreta las señales El equivalente en lógica negativa de una función en lógica positiva es el dual de la función Las definiciones de puertas (AND, OR, etc) se refieren siempre a lógica positiva para entradas y salidas. Datos Fabricante Lógica Positiva Lógica Negativa A B f A B f A B f L L L 0 0 0 1 1 1 L H L 0 1 0 1 0 1 H L L 1 0 0 0 1 1 H H H 1 1 1 0 0 0 Lógica positiva y negativa Para evitar confusiones, use solo lógica positiva o negativa en el diseño Puede haber lógicas mezcladas Esto no siempre es posible Una salida activa alta puede conectarse a una entrada activa baja Una señal activa alta (baja) indica que la acción esperada se produce cuando el voltaje es alto (bajo) © 2014 Mario Medina C. Ejemplo: apertura de una válvula Válvula se abre sólo si se cumplen A y B A: petición de llenado B: estanque vacío C: apertura de válvula A (activa alta) B (activa alta) Lógica Positiva C (activa alta) A (activa baja) C (activa baja) B (activa baja) Lógica Negativa 4 Ejemplo: apertura de una válvula Puede resultar confuso interpretar el tipo de lógica con que se diseña un esquemático. Ejemplo: apertura de una válvula Esquema anterior cumple con lo requerido Convenciones Todas las puertas usan lógica positiva Marcar explícitamente señales activas bajas Burbuja en la entrada o salida correspondiente A (activa baja) C (activa baja) Complicado de entender por ops. de inversión Convención hacer corresponder las entradas activas bajas de una A puerta, con salidas activas bajas (bubble matching) (activa baja) C A (activa baja) (activa baja) C B (activa baja) (activa baja) B (activa baja) Notaciones alternativas B (activa baja) Bubble mismatch Circuitos integrados Conjunto de resistencias, diodos y transistores fabricados en una sola pieza de material semiconductor (generalmente silicio) llamada sustrato (die) El chip se encuentra dentro de un receptáculo plástico o cerámico que tiene pines para la interconexión Ejemplos de circuitos integrados DIPs, SOICs y PLCCs Dual Inline Package (DIP) Plastic Leaded Chip Carrier (PLCC) Encapsulados típicos de SSI y MSI Componentes DIP Componentes SOIC (Dual In-line Package) (Small Outline Inline Package) 0.335 – 0.334 in. 14 13 12 11 10 0.740 – 0.770 in. 14 13 12 11 10 9 0.250 0.010 in. 1 2 3 4 5 6 8 6 7 0.228 – 0.244 in. 7 1 Pin no.1 identifiers 9 8 2 3 4 5 Lead no.1 identifier 14 1 14 1 © 2014 Mario Medina C. 5 Encapsulados típicos de LSI Clasificación de complejidad de circuitos integrados Circuitos integrados digitales Conjunto de puertas logicas fabricadas sobre una misma base semiconductora Han tenido un desarrollo sostenido tendiente a: Reducir el tamaño físico Reducir el retardo Reducir el consumo de potencia Incluir funciones más complejas Reducir los costos de fabricación Clasificación de CI por escala de integración Chips SSI y MSI vistos en clases se usan como interfaz para CI más complejos Complejidad Compuertas por chip Small Scale Integration (SSI) 100 a 9999 Very Large Scale Integration (VLSI) 10000 a 99999 Ultra Large Scale Integration (ULSI) 100000 a 999999 1000000 o más Familia TTL (TransistorTransistor Logic) Utilizan transistores bipolares (PNP - NPN) Familia más popular de circuitos integrados Todos los chips de esta serie comienzan con este número (7400, 7402, 7438, etc) Subfamilias derivadas incorporan nuevas tecnologías Idéntica configuración de pines y operación lógica Diferencias están en características eléctricas (potencia, velocidad, etc) C. I. de la familia TTL usan 0V y 5V (Vcc) como estados lógicos 0 y 1 © 2014 Mario Medina C. Wafer de silicio de 5” con cientos de pequeñas “IC dies” 12 a 99 Large Scale Integration (LSI) menos de 12 Medium Scale Integration (MSI) Giga Scale Integration (GSI) Fabricación de circuitos integrados Familia TTL Chip ID. Función 7400 Quad 2 input NAND 7408 Quad 2 input AND 7432 Quad 2 input OR 7486 Quad 2 input XOR 7410 Triple 3 input NAND 7411 Triple 3 input AND 7427 Triple 3 input NOR 7420 Dual 4 input NAND 7421 Dual 4 input AND 7404 Hex Not 7430 8-input NAND 6 Configuraciones de IC típicos VCC VCC 14 13 12 11 10 9 1 2 3 4 5 6 '00 8 7 GND VCC 2 3 4 5 6 '10 8 7 GND VCC 2 3 4 5 6 ' 02 7 GND 1 2 3 4 5 '27 6 8 7 GND 2 3 4 5 6 '11 1 2 3 4 5 9 8 6 7 GND '04 8 7 GND 1 2 3 4 '30 5 6 8 7 GND 2 3 4 5 9 6 '20 1 2 3 4 5 6 '08 8 7 GND 8 7 GND 1 2 3 4 2 3 4 '32 5 9 6 8 7 GND 5 6 '21 14 13 12 11 10 9 1 2 3 4 Tecnología Schottky: alta frecuencia de conmutación y uso eficiente de la potencia Serie TTL 14 13 12 11 10 9 8 7 GND VCC 14 13 12 11 10 1 14 13 12 11 10 9 VCC 14 13 12 11 10 VCC 14 13 12 11 10 9 1 VCC 14 13 12 11 10 VCC 14 13 12 11 10 9 VCC 14 13 12 11 10 9 1 1 8 VCC 14 13 12 11 10 9 1 VCC 14 13 12 11 10 9 Familias TTL 5 '86 6 8 7 GND 7404 Baja potencia 74L 74L04 Alta velocidad 74F 74F04 Schottky 74S 74S04 Schottky baja potencia 74LS 74LS04 Schottky avanzada 74AS 74AS04 Schottky avanzada de baja potencia 74ALS 74ALS04 Bajo voltaje (3.3V) 74LV 74LV04 Familias CMOS Posteriores a tecnología TTL Menor consumo de potencia Usan VDD en rango 4V a 15V como 1 lógico Familia 4000: alternativa independiente a TTL Familia 74C: funcionalidad compatible con TTL 74C04 es lógicamente igual a 7404 Familia 74CT: Voltajes compatibles con TTL Retardos en puertas lógicas Serie CMOS Estándar CMOS Prefijo Ejemplo 74C 74C04 High-Speed CMOS 74HC 74HC04 Very High-Speed CMOS 74VHC 74VHC04 Fast CMOS High-Speed TTL Compatible Advanced CMOS 74FC 74FC04 74HCT 74HCT04 74AC 74AC04 Advanced High-Speed CMOS 74AHC 74AHC04 Bajo voltaje (3.3V, 5V) 74LVX 74LVX04 Retardos de las compuertas Salida depende sólo de la combinación de las entradas al circuito Considerar comportamiento dinámico Cómo varía la salida en función del tiempo La mayoría son eléctricamente compatibles con TTL Hemos considerado sólo el comportamiento estático de los circuitos combinacionales Ejemplo 74 Familias CMOS Prefijo Estándar Propagación de señales por los cables no es instantánea Distintas puertas lógicas presentan retardos diferentes Señales en un circuito viajan por múltiples caminos con retardos diferentes Puede producir pulsos espurios en la salida (glitches) © 2014 Mario Medina C. 7 Comportamiento dinámico de un pulso lógico Retardos en puertas TTL Retardos 1→0 (1) y 0→1 (2) suelen ser distintos Especificados por el fabricante Máximo Componente TTL 7400 74H00 74L00 74LS00 74S00 74LS02 74LS86A tpHL 15 10 60 15 5 15 22 © 2014 Mario Medina C. Típico tpLH 22 10 60 15 4.5 15 30 tpHL 7 6.2 31 10 3 10 13 tpLH 11 5.9 35 9 3 10 20 8