Ejemplo de diseño de memoria

Anuncio

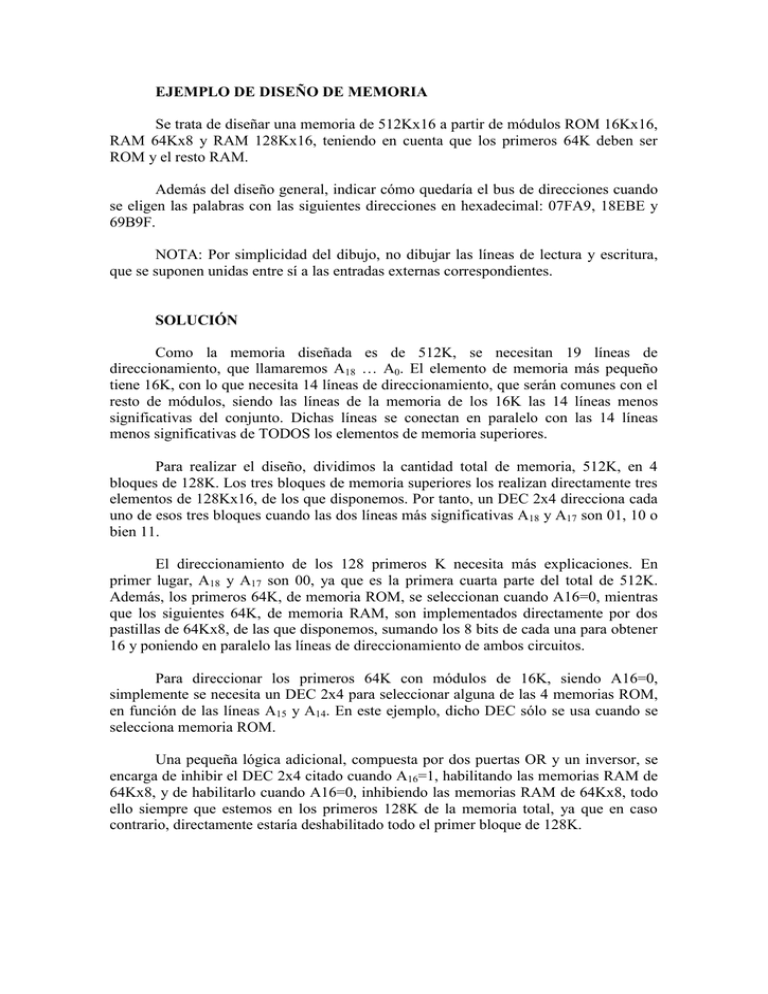

EJEMPLO DE DISEÑO DE MEMORIA Se trata de diseñar una memoria de 512Kx16 a partir de módulos ROM 16Kx16, RAM 64Kx8 y RAM 128Kx16, teniendo en cuenta que los primeros 64K deben ser ROM y el resto RAM. Además del diseño general, indicar cómo quedaría el bus de direcciones cuando se eligen las palabras con las siguientes direcciones en hexadecimal: 07FA9, 18EBE y 69B9F. NOTA: Por simplicidad del dibujo, no dibujar las líneas de lectura y escritura, que se suponen unidas entre sí a las entradas externas correspondientes. SOLUCIÓN Como la memoria diseñada es de 512K, se necesitan 19 líneas de direccionamiento, que llamaremos A18 … A0. El elemento de memoria más pequeño tiene 16K, con lo que necesita 14 líneas de direccionamiento, que serán comunes con el resto de módulos, siendo las líneas de la memoria de los 16K las 14 líneas menos significativas del conjunto. Dichas líneas se conectan en paralelo con las 14 líneas menos significativas de TODOS los elementos de memoria superiores. Para realizar el diseño, dividimos la cantidad total de memoria, 512K, en 4 bloques de 128K. Los tres bloques de memoria superiores los realizan directamente tres elementos de 128Kx16, de los que disponemos. Por tanto, un DEC 2x4 direcciona cada uno de esos tres bloques cuando las dos líneas más significativas A18 y A17 son 01, 10 o bien 11. El direccionamiento de los 128 primeros K necesita más explicaciones. En primer lugar, A18 y A17 son 00, ya que es la primera cuarta parte del total de 512K. Además, los primeros 64K, de memoria ROM, se seleccionan cuando A16=0, mientras que los siguientes 64K, de memoria RAM, son implementados directamente por dos pastillas de 64Kx8, de las que disponemos, sumando los 8 bits de cada una para obtener 16 y poniendo en paralelo las líneas de direccionamiento de ambos circuitos. Para direccionar los primeros 64K con módulos de 16K, siendo A16=0, simplemente se necesita un DEC 2x4 para seleccionar alguna de las 4 memorias ROM, en función de las líneas A15 y A14. En este ejemplo, dicho DEC sólo se usa cuando se selecciona memoria ROM. Una pequeña lógica adicional, compuesta por dos puertas OR y un inversor, se encarga de inhibir el DEC 2x4 citado cuando A16=1, habilitando las memorias RAM de 64Kx8, y de habilitarlo cuando A16=0, inhibiendo las memorias RAM de 64Kx8, todo ello siempre que estemos en los primeros 128K de la memoria total, ya que en caso contrario, directamente estaría deshabilitado todo el primer bloque de 128K. Parte común del Bus de direcciones (A13-A0), las 14 líneas menos significativas A0 14 14 A13 0 DEC 2x4 1 2 1 A15 ROM 16Kx16 OE CS WR ROM 16Kx16 OE CS WR ROM 16Kx16 DATOS 16 15 K 14 0 A14 0K 13---0 OE CS WR Espacio direccionable E 3 16 K 13---0 DATOS 16 31 K 14 OR 32 K 13---0 DATOS 16 47 K 14 A16 48 K 13---0 OE CS WR ROM 16Kx16 DATOS 16 63 K 14 OR 15 14 13-0 CS RAM 64Kx8 OE CS WR OE 0 A17 CS WR 0 1 64 K 15 14 13-0 CS 8 RAM 64Kx8 16 127 K 128 K 16 15 14 13---0 RAM 128Kx16 DATOS 16 256 K 16 15 14 13---0 RAM 128Kx16 DATOS 255 K 16 383 K DEC 2x4 2 A18 OE 1 E 3 MEM 16 Bus de datos (D15-D0) CS WR 384 K 16 15 14 13---0 RAM 128Kx16 DATOS 16 511 K Parte común del Bus de direcciones (A13-A0), las 14 líneas menos significativas Direcciones 16.297 3FA9 H 00.000 00000H A0 14 Dirección 32.681 07FA9 H A13 A15 DEC 2x4 1 DATOS 16 16.383 03FFFH 2 E 3 16.384 04000 13---0 OE CS WR 1 0 ROM 16Kx16 14 0 1 13---0 OE CS WR (14 bits) 0 A14 14 ROM 16Kx16 DATOS 16 32.767 07FFFH 14 OR 32.768 08000H 13---0 OE CS WR ROM 16Kx16 DATOS 16 49.151 0BFFFH 14 A16 0 49.152 0C000H 13---0 OE CS WR ROM 16Kx16 DATOS 16 65.535 0FFFF 14 1 OR 0 65.536 10000H 1 15 14 13-0 CS RAM 64Kx8 15 14 13-0 CS RAM 64Kx8 16 131.071 1FFFFH 8 OE CS WR OE 0 A17 0 CS WR 0 1 131.072 20000H 16 15 14 13---0 RAM 128Kx16 DATOS 16 262.144 40000H 16 15 14 13---0 RAM 128Kx16 DATOS 262.143 3FFFFH 16 393.215 5FFFFH DEC 2x4 A18 2 0 OE 1 E 3 MEM 16 Bus de datos (D15-D0) CS WR 16 15 14 13---0 RAM 128Kx16 DATOS 393.216 60000H 16 524.287 7FFFFH Parte común del Bus de direcciones (A13-A0), las 14 líneas menos significativas A0 14 14 Dirección 102.078 18EBE H A13 0 A14 A15 DEC 2x4 1 DATOS 16 16.383 03FFFH 2 E 3 16.384 04000 13---0 OE CS WR 1 1 ROM 16Kx16 14 0 0 00.000 00000H 13---0 OE CS WR Direcciones ROM 16Kx16 DATOS 16 32.767 07FFFH 14 OR 32.768 08000H 13---0 OE CS WR ROM 16Kx16 DATOS 16 49.151 0BFFFH 14 A16 1 0 0 OR 0 49.152 0C000H 13---0 OE CS WR ROM 16Kx16 DATOS 16 65.535 0FFFF 14 36.542 8EBE H 1 1 0 0 1 15 14 13-0 CS RAM 64Kx8 0 (16 bits) 65.536 10000H 15 14 13-0 CS RAM 64Kx8 16 131.071 1FFFFH 8 OE CS WR OE 0 A17 0 CS WR 0 1 131.072 20000H 16 15 14 13---0 RAM 128Kx16 DATOS 16 262.144 40000H 16 15 14 13---0 RAM 128Kx16 DATOS 262.143 3FFFFH 16 393.215 5FFFFH DEC 2x4 A18 2 0 OE 1 E 3 MEM 16 Bus de datos (D15-D0) CS WR 16 15 14 13---0 RAM 128Kx16 DATOS 393.216 60000H 16 524.287 7FFFFH Parte común del Bus de direcciones (A13-A0), las 14 líneas menos significativas A0 14 Dirección 433.055 69B9F H A13 0 A14 A15 DEC 2x4 1 ROM 16Kx16 DATOS 16 16.383 03FFFH 2 E 3 16.384 04000 13---0 OE CS WR 1 1 00.000 00000H 13---0 OE CS WR 14 0 0 14 Direcciones ROM 16Kx16 DATOS 16 32.767 07FFFH 14 OR 32.768 08000H 13---0 OE CS WR ROM 16Kx16 DATOS 16 49.151 0BFFFH 14 A16 0 49.152 0C000H 13---0 OE CS WR ROM 16Kx16 DATOS 16 65.535 0FFFF 14 1 OR 1 65.536 10000H 1 15 14 13-0 CS RAM 64Kx8 15 14 13-0 CS RAM 64Kx8 16 131.071 1FFFFH 8 OE CS WR OE 0 A17 1 CS WR 0 1 131.072 20000H 16 15 14 13---0 RAM 128Kx16 DATOS 16 262.144 40000H 16 15 14 13---0 RAM 128Kx16 DATOS DEC 2x4 262.143 3FFFFH 16 393.215 5FFFFH 39.839 9B9F H (16 bits) A18 2 1 OE 1 E 3 MEM 16 Bus de datos (D15-D0) CS WR 16 15 14 13---0 393.216 60000H 0 10 RAM 128Kx16 DATOS 16 524.287 7FFFFH EJEMPLO 1 Para seleccionar la dirección de memoria 07FA9 H, equivalente a 32.681 decimal, hay que elegir el 2º bloque de 16K, que cubre de las posiciones 16.384, hasta 32.767, y dentro de dicho bloque, la posición relativa referida a su comienzo, 16.384, es 16.297, ya que 16.384+16.297=32.681. Por tanto, en las 14 líneas A13 … A0 del módulo hay que poner 16.297, en hexadecimal 3FA9, A15A14 = 01, por ser el 2º bloque de 16K, A16=0 por estar en la primera mitad de los 128 primeros K y A18A17=00 por estar en el primer bloque de 128K del total de 512K. Viendo directamente la dirección, resulta: 07FA9 00 0 0111 1111 1010 1001 A18A17 A16 A15A14A13A12 A11A10A9A8 A7A6A5A4 A3A2A1A0 3FA9 EJEMPLO 2 Para seleccionar la dirección de memoria 18EBE H, equivalente a 102.078 decimal, hay que elegir el 2º bloque de 64K, que cubre de las posiciones 65.536, hasta 131.071, y dentro de dicho bloque, la posición relativa referida a su comienzo, 65.536, es 36.542, ya que 65.536+36.542=102.078. Por tanto, en las 16 líneas A15 … A0 del módulo hay que poner 36.542, en hexadecimal 8EBE, A16=1 por estar en la segunda mitad de los 128 primeros K y A18A17=00 por estar en el primer bloque de 128K del total de 512K. Viendo directamente la dirección, resulta: 18EBE 00 1 1000 1110 1011 1110 A18A17A16 A15A14A13A12 A11A10A9A8 A7A6A5A4 A3A2A1A0 8EBE EJEMPLO 3 Para seleccionar la dirección de memoria 69B9F H, equivalente a 433.055 decimal, hay que elegir el 4º bloque de 128K, que cubre de las posiciones 393.216, hasta 524.287, y dentro de dicho bloque, la posición relativa referida a su comienzo, 393.216, es 39.839, ya que 393.216+39.839=433.055. Por tanto, en las 17 líneas A16 … A0 del módulo hay que poner 39.839, en hexadecimal 9B9F, y A18A17=11 por estar en el cuarto bloque de 128K del total de 512K. Viendo directamente la dirección, resulta: 69B9F 11 0 1001 1011 1001 1111 A18A17 A16 A15A14A13A12 A11A10A9A8 A7A6A5A4 9B9F A3A2A1A0