Controlador Programable de Interrupciones i8259 FUNCIONES

Anuncio

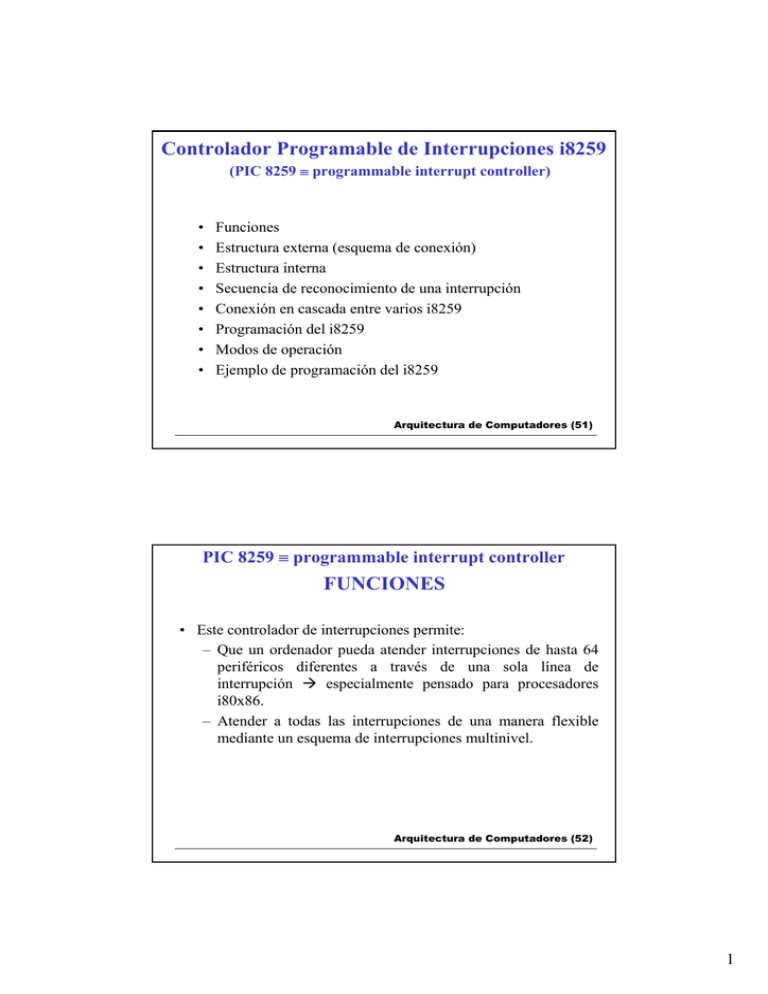

Controlador Programable de Interrupciones i8259

(PIC 8259 ≡ programmable interrupt controller)

•

•

•

•

•

•

•

•

Funciones

Estructura externa (esquema de conexión)

Estructura interna

Secuencia de reconocimiento de una interrupción

Conexión en cascada entre varios i8259

Programación del i8259

Modos de operación

Ejemplo de programación del i8259

Arquitectura de Computadores (51)

PIC 8259 ≡ programmable interrupt controller

FUNCIONES

• Este controlador de interrupciones permite:

– Que un ordenador pueda atender interrupciones de hasta 64

periféricos diferentes a través de una sola línea de

interrupción Æ especialmente pensado para procesadores

i80x86.

– Atender a todas las interrupciones de una manera flexible

mediante un esquema de interrupciones multinivel.

Arquitectura de Computadores (52)

1

PIC 8259 ≡ programmable interrupt controller

ESTRUCTURA EXTERNA

(esquema de conexión)

• IRQ0 – IRQ7: peticiones de

interrupción de los periféricos, de mayor

a menor prioridad.

• INT: petición de interrupción al

procesador gestionada por el i8259.

• INTA (Interrupt Acknowledgement):

reconocimento/aceptación

de

la

interrupción por parte del procesador.

• CS (chip select): para leer y escribir en

los registros del PIC Æ utilizada para

programar PIC.

Arquitectura de Computadores (53)

PIC 8259 ≡ programmable interrupt controller

ESTRUCTURA EXTERNA

(Descripción de Señales)

• CAS2 – CAS0: líneas para la conexión en cascada de varios i8259.

Actúan como salida del PIC maestro y como entrada de los PIC

esclavos.

• EN: indica si el PIC actúa como maestro o como esclavo cuando hay

varios encadenados (en cascada).

• RD, RW (read, write): permiten leer o escribir en los registros de

control del i8259.

• A0: única línea del bus direcciones usada para seleccionar los registros

de control.

• Bus de datos: intercambio de datos entre el PIC y el resto de

componentes de un computador (memoria y procesador).

Arquitectura de Computadores (54)

2

PIC 8259 ≡ programmable interrupt controller

ESTRUCTURA INTERNA

Arquitectura de Computadores (55)

ESTRUCTURA INTERNA

Registros Internos

• Todos los registros del PIC son de ocho bits:

– IRR (Interrupt Request Register): cada uno de los bits de

este registro está asociado con una de las líneas de petición

de interrupción. Estos bits almacenan las peticiones de

interrupción pendientes.

– ISR (In-Service Register): cada uno de los bits se asocia

con una línea de petición de interrupción. En este caso sólo

se activa el bit que corresponde a la interrupción que se está

procesando en un momento dado.

– IMR

(Interrupt

Mask

Register):

registro

de

enmascaramiento de interrupciones.

Arquitectura de Computadores (56)

3

ESTRUCTURA INTERNA

– Lógica de gestión de prioridad: determina qué

interrupción, de las solicitadas en el IRR, debe ser atendida

primero.

– Buffer del bus de datos: conecta el 8259 con el bus de

datos de la placa principal del ordenador.

– Lógica de lectura y escritura: acepta los comandos que

envía la CPU; transfiere el estado del 8259 hacia el bus de

datos.

– Buffer de cascada/comparador: almacena y compara las

identificaciones de todos los 8259 del sistema.

Arquitectura de Computadores (57)

PIC 8259 ≡ programmable interrupt controller

Secuencia de Reconocimiento de una Interrupción

1.

Una o más líneas IRQ son activadas por los periféricos conectados al PIC y esto

activa los correspondientes bits del IRR.

2.

El 8259 evalúa la prioridad de estas interrupciones (mediante el codificador de

prioridad) y solicita una interrupción a la CPU activando la línea INT.

3.

Cuando la CPU reconoce la interrupción envía la señal INTA.

4.

Entonces el PIC, recibida la señal INTA, activa el bit correspondiente a la

interrupción de mayor prioridad (la que va a ser procesada) en el ISR y borra ese

mismo bit en el IRR. En este ciclo, el 8259 aún no controla el bus de datos.

5.

Cuando la CPU envía un segundo ciclo INTA, el 8259 deposita en el bus de

datos un valor de 8 bits que indica el número de vector de interrupción (type code

= offset o base de interrupciones del PIC + nº de IRQ). La CPU multiplica este

valor por 4 para buscar en esa dirección de memoria la dirección de comienzo de

la RTI.

6.

En el modo AEOI del PIC, el bit de la interrupción en el ISR es borrado

automáticamente nada más acabar el segundo pulso INTA. En caso contrario, este

bit permanece activo hasta que la CPU envíe el mandato (comand) EOI (End of

Interrupt) al final de la rutina que trata la interrupción (esto es lo más normal).

Arquitectura de Computadores (58)

4

PIC 8259 ≡ programmable interrupt controller

Conexión en cascada entre varios i8259 (I)

• Cuando es necesario atender a las peticiones de interrupción de más de

ocho periféricos se pueden conectar varios PIC’s en cascada.

• Se utilizan dos niveles de controladores: en el primero tenemos al PIC

master, y en el segundo entre 1 y 8 esclavos. Sólo la salida INT del master

está conectada a la entrada INTR del procesador.

• Para conectar un PIC en configuración de cascada se conecta su salida INT

a una de las entradas IRQ del PIC master y sus entradas CAS a las salidas

CAS del master.

• Además, la entrada EN debe ser coherente con la función de cada uno de

los microcontroladores: debe valer 0 para los esclavos y 1 para el master.

Arquitectura de Computadores (59)

Conexión en cascada entre varios i8259 (II)

•

La secuencia de reconocimiento de una

petición de interrupción en las líneas del

master es la misma que ya se ha explicado.

Si la petición de interrupción es en una de las

líneas de un esclavo, entonces:

1. El PIC esclavo detecta la petición de

interrupción por una de sus líneas y activa la

señal INT.

2. El PIC master detecta la petición de

interrupción por la línea

a la que

se conecta

Arquitectura

de Computadores

(60)

ese esclavo. Activa el correspondiente bit del

5

Conexión en cascada entre varios i8259 (III)

6.

Con el segundo pulso de INTA, el esclavo vuelca en el bus de datos el

número del vector de interrupción.

7.

En el modo AEOI, los bits de los registros ISR del master y el esclavo se

limpian automáticamente cuando termina el segundo ciclo de INTA. Si

no se trabaja en este modo, el procesador deberá enviar dos mandatos de

EOI, uno al master y otro al esclavo. Para que esto funcione así, la RTI

debe saber en cada caso si está atendiendo a una interrupción gestionada

directamente por el master o a través de una pareja master-esclavo. Esto

es necesario para que envíe uno o dos comandos EOI respectivamente.

8.

Se debe tener en cuenta que la conexión de un PIC esclavo al PIC master

origina una reestructuración del esquema de prioridades de los niveles de

interrupción del computador: se intercalan ocho nuevos niveles entre los

que ya tuviera el master conectados.

Arquitectura de Computadores (61)

PIC 8259 ≡ programmable interrupt controller

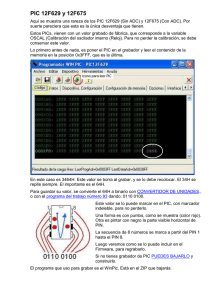

Programación del i8259 (I)

•

El 8259 acepta dos tipos de comandos generados por la CPU:

1.

2.

ICW (Inicialization Command Word): inicializa el 8259.

OCW (Operation Command Word): programa la modalidad de funcionamiento.

•

La comunicación con el 8259 emplea las líneas WR y RD, así como la A0

y el bus de datos.

•

El hecho de que exista una sola línea de direcciones (la A0) implica que el

PIC sólo ocupa dos direcciones de puerto en el espacio de E/S del

ordenador (normalmente 20h y 21h).

•

Los ICW y OCW constan de secuencias de 2 a 4 comandos consecutivos

que el 8259 espera recibir secuencialmente, unos tras otros, a través del

bus de datos.

•

Los ICW deben mandarse antes de que el sistema comience a trabajar.

Posteriormente los OCW pueden ser enviados en cualquier momento, una

vez realizada la inicialización.

Arquitectura de Computadores (62)

6

Programación del i8259 (II)

ICWS (Inicialization Command Words)

•ICW1 (primera palabra de inicialización)

• Cuando un mandato es enviado con A0=0 y D4=1, el PIC lo

interpreta como la primera palabra de la inicialización e inicia la

secuencia de inicialización.

•Se inicializan (reset) todos los circuitos, se limpia el IMR y se

asignan los niveles de prioridad.

•Los bits más importantes de este comando son:

– SNGL: Si vale 0 (modo simple, no es necesario ICW3); 1 (en cascada).

– IC4: Si vale 0, significa que tampoco es necesario el comando ICW4

(Todas las funciones que programa esta palabra se ponen a cero).

– LTIM: Indica si las líneas de petición de interrupción funcionan por

nivel (1) o por flancos (0).

Arquitectura de Computadores (63)

Programación del i8259 (III)

ICWS (Inicialization Command Words)

• ICW2: se envía con A0=1, siempre a continuación de ICW1. Programa el

Offset (base) del vector de interrupciones.

• ICW3: se envía con A0=1 sólo si existe más de un 8259 en el sistema

(señal SNGL de ICW1 a 1), en caso contrario en su lugar se enviaría ICW4

(si procede). Hay que distinguir entre maestro y esclavo:

– En el caso del PIC maestro, cada bit del comando indica si hay un PIC

conectado a la correspondiente línea de petición de interrupción. Por

ejemplo, si S6 vale 1 significa que a la línea IRQ6 tenemos conectado

un 8259 en lugar de un periférico.

– Para los PIC esclavos, este mandato sirve para indicar la línea del PIC

maestro a la que se conectan el PIC esclavo (que siempre estará entre 0

y 7).

Arquitectura de Computadores (64)

7

Programación del i8259 (IV)

ICWS (Inicialization Command Words)

•

ICW4 (A0 = 1): se envía cuando se quiere que el PIC trabaje en un modo de

operación diferente al establecido por defecto. (previamente hay que poner el bit

IC4 de ICW1 a 1).

–

–

–

–

–

•

•

•

SFNM: Bit que activa el Special Fully Nested Mode.

BUF: Bit que activa el Buffered Mode.

M/S: l cuando se trata del NC maestro, y 0 cuando se trata de un NC esclavo.

AEOI: Bit que activa el modo auto EOI.

MD: Bit que señala si trabajamos con el modo del PIC para el 8086.

Fully Nested Mode, modo por defecto, que ordena las IR por prioridades (IR0,

máxima – IR7, mínima). Equivale a enviar ICW4 con todos sus bits a cero.

Buffered Mode, el 8259 tiene una serie de buffers internos para almacenar los datos

antes de volcarlos al bus.

Modos de EOI, bajar el bit del registro ISR al final de la señal INTA (AEOI) o para

que no se baje de forma manual usando OCW2.

Arquitectura de Computadores (65)

Programación del i8259 (I)

OCWS (Operation Command Words)

Existen tres comandos básicos,

OCW1 (con A0=l), OCW2 y OCW3 (estos dos últimos con A0=0).

Permiten realizar operaciones de:

–

–

–

habilitar/deshabilitar niveles de interrupción,

modificar las prioridades de estos niveles,

enviar órdenes de EOI cuando no se trabaja en modo automático,...

OCW1. Los bits a 1 inhiben (enmascaran) la correspondiente IR y los

que están a 0 habilitan (desenmascaran) la IR.

Arquitectura de Computadores (66)

8

Programación del i8259 (II)

OCWS (Operation Command Words)

OCW2. Varias funciones.

•Permite configurar un sistema de rotaciones de

prioridades: la última IR atendida pasa a ser la IR de

menor prioridad.

•Permite el envío del EOI manual por parte del

procesador.

Arquitectura de Computadores (67)

Programación del i8259 (III)

OCWS (Operation Command Words)

OCW3: Varias funciones.

• Permite leer los registros IRR e ISR.

• Permite mediante el bit POLL gestionar las interrupciones por software

(poco utilizado) inhibiendo la salida INT y posteriormente leyendo el

registro ISR.

• También permite trabajar con el modo de operación Special Mask.

Arquitectura de Computadores (68)

9

PIC 8259 ≡ programmable interrupt controller

Modos de operación (I)

• Fully Nested Mode (modo de anidamiento completo): el i8259 opera, por

defecto, en esta modalidad.

– En este modo, tras la secuencia de inicialización, las interrupciones quedan

ordenadas, por prioridades, de mayor (IRQ0) a menor (IRQ7). Este orden

puede modificarse en la modalidad de prioridad rotatoria o con el mandato de

asignación de prioridad.

Cuando se produce un reconocimiento de interrupción por parte de la CPU,

el i8259 evalúa cuál es la interrupción pendiente de mayor prioridad, coloca

su número de vector en el bus y activa su bit correspondiente en el ISR.

Este bit permanece activo hasta que el 8259 recibe el mandato EOI (fin de

interrupción) por parte del procesador. Mientras el bit del ISR esté activo,

todas las interrupciones de igual o menor prioridad que lleguen permanecen

inhibidas; Sin embargo, las de mayor prioridad podrán interrumpir.

Arquitectura de Computadores (69)

PIC 8259 ≡ programmable interrupt controller

Modos de operación (II)

• Special Fully Nested Mode (modo de anidamiento completo especial):

– se emplea en sistemas que tienen varios PIC conectados. Sólo el i8259 maestro

es programado en este modo.

– Las diferencias respecto al Fully Nested Mode normal son:

– Cuando se atiende una interrupción de un 8259 esclavo, si viene otra de

mayor prioridad de ese mismo 8259 esclavo, se provoca una

interrupción al maestro (normalmente, el 8259 esclavo estaría

enmascarado mientras se procesa una de sus interrupciones).

– Cuando acaba la rutina de servicio de interrupción, hay que enviar un

EOI al 8259 esclavo. Además hay que leer a continuación su ISR y

comprobar si es cero. En ese caso, hay que enviar además otro EOI al

8259 maestro (si no es cero significa que aún hay interrupciones en

proceso en el 8259 esclavo).

Arquitectura de Computadores (70)

10

PIC 8259 ≡ programmable interrupt controller

Modos de operación: Modos de EOI (III)

•

•

•

•

El EOI (End Of lnterrupt) sirve para bajar el bit del ISR que representa la

interrupción que está siendo procesada.

El EOI puede producirse automáticamente (AEOI) al final de la última señal

INTA que envía la CPU.

Como la mayoría de los sistemas requieren una gestión de prioridades en las

interrupciones, es mejor que el EOI lo envíe el propio procesador al 8259 a

través de OCW2 cuando termine la RTI (rutina de tratamiento de la

interrupción).

En un sistema con varios PIC, el EOI debe ser enviado al 8259 esclavo y

también al maestro. Hay dos modalidades de EOI:

– No especifico: el 8259 borra el bit más significativo que esté activo en el

registro ISR, que se supone que es el correspondiente a la última

interrupción producida (la de mayor prioridad y que está siendo

procesada). Esto es suficiente para un sistema donde se respeta el Fully

Nested Mode.

– Especifico: si el 8259 es incapaz de determinar cuál fue el último nivel de

interrupción procesado (no se respeta el Fully Nested Mode), la RTI debe

enviar un EOI específico al PIC indicándole qué bit hay que borrar en el

ISR.

Arquitectura de Computadores (71)

PIC 8259 ≡ programmable interrupt controller

Modos de operación (IV)

• Rotación de prioridades. Hay sistemas en que varios periféricos

tienen el mismo nivel de prioridad, en los que no interesa mantener un

orden de prioridades en las líneas IR.

• La solución consiste en asignar el menor nivel de prioridad a la

interrupción recién atendida para permitir que las demás pendientes se

procesen también.

• Para ello se envía un EOI que rote las prioridades. Por ejemplo, si se

había procesado una IRQ3, entonces IRQ3 pasará a tener el menor

nivel de prioridad e IRQ4 el mayor. Existe también una asignación

específica de prioridades a través de OCW2.

• Special Mask Mode. Hay ocasiones en las que mientras se ejecuta una

RTI es necesario permitir que se produzcan ciertas interrupciones de

menor prioridad. Esto implica alterar la estructura normal de

prioridades activando el Special Mask Mode con OCW3 durante la

RTI (es importante inhibirlo de nuevo al final). Una vez activado este

modo, el registro IMR indica qué interrupciones están permitidas (bit a

0) y cuáles inhibidas (bit a 1). Al final hay que enviar un EOI

especifico, ya que este modo de trabajo altera el Fully Nested Mode.

Arquitectura de Computadores (72)

11

PIC 8259 ≡ programmable interrupt controller

Ejemplo de programación del i8259 (I)

En un PC existen dos i8259, uno actúa como maestro y el otro como

esclavo.

Ambos son inicializados por la BIOS al arrancar el ordenador.

Generalmente la inicialización de la BIOS se hace usando código

ensamblador.

El 8259 está conectado al puerto (dirección) de E/S 20h y el esclavo al

puerto A0h. En este código escrito en C se propone una posible

inicialización.

/* Declaración de constantes */

#define BASE_INT_MASTER

#define PORT_MASTER_8259_0

#define PORT_MASTER_8259_1

8h

20h

21h

#define BASE_INT_SLAVE

#define PORT_SLAVE_8259_0

#define PORT_SLAVE_8259_1

70h

0A0h

0A1h

Arquitectura de Computadores (73)

PIC 8259 ≡ programmable interrupt controller

Ejemplo de programación del i8259 (II)

/* Rutina de inicialización */

void INICIALIZAR_SISTEMA () {

disable (); /* Inhibición de las interrupciones */

...

/* Como se trabaja con 8259-s en cascada, se precisan al menos las tres ICW iniciales.

No obstante se hará uso también de la ICW4 */

/*** INICIALIZACIÓN MAESTRO ***/

/* ICW1: activación por flancos, modo en cascada, si ICW4 */

outportb (PORT_MASTER _8259_0, 0x11); /* 0b 0001 0001 */

/* ICW2 : base interrupciones */

outportb (PORT_MASTER_8259_1, BASE_INT_MASTER);

/* ICW3 : se conecta un 8259 esclavo en la IR2 del maestro por ejemplo */

outportb (PORT_MASTER_8259_1, 0x04);

/*

ICW4 : establecer modos de funcionamiento iniciales: “special fully nested”

desactivado, “buffered mode” activado, auto EOI (AEOI) */

outportb (PORT_MASTER_8259_1, 0x0F); /* 0b 0000 1111 */

Arquitectura de Computadores (74)

12

PIC 8259 ≡ programmable interrupt controller

Ejemplo de programación del i8259 (III)

/*** INICIALIZACIÓN ESCLAVO ***/

/* ICW1: activación por flancos, modo en cascada, si ICW4 */

outportb (PORT_SLAVE_8259_0, 0x11); /* 0b 0001 0001 */

/* ICW2 : base interrupciones */

outportb (PORT_SLAVE_8259_1, BASE_INT_SLAVE);

/* ICW3 : es el 8259 esclavo conectado a la IR2 del maestro */

outportb (PORT_SLAVE_8259_1, 0x02);

/* ICW4 : establecer modos de funcionamiento iniciales: “fully nested” desactivado,

“buffered mode” activado, auto EOI (AEOI) */

outportb (PORT_SLAVE_8259_1, 0x0B); /* 0b 0000 1011 */

Arquitectura de Computadores (75)

PIC 8259 ≡ programmable interrupt controller

Ejemplo de programación del i8259 (IV)

/* Ahora mediante las OCW se pueden gestionar o reconfigurar los 8259.

Generalmente las OCW2 y OCW3 se usan en las rutinas de atención de las

interrupciones para poder hacer un uso más personal y controlado de estas. */

/* OCW1 : habilitar sólo las IR0, IR1, IR2, IR3 y enmascarar resto en el esclavo */

outportb (PORT_MASTER_8259_1, 0x00) ;

outportb (PORT_SLAVE_8259_1, 0xF0);

/* OCW2 : activar en ambos rotación de prioridades con AEOI */

outportb (PORT_MASTER_8259_0, 0x80); /* 0b 1000 0000 */

outportb (PORT_SLAVE_8259_0, 0x80); /* 0b 1000 0000 */

/* OCW3 : no se necesita todavía leer ISR ó IRR ni habilitar el modo "special mask”

y por lo tanto en la inicialización no se usa este mandato. Se podría incluir en

una rutina de atención para inhibir o desinhibir momentáneamente algunas

interrupciones determinadas. */

…

enable (); /* Habilitación de interrupciones */

};

Arquitectura de Computadores (76)

13