Organización de la Computadora

Anuncio

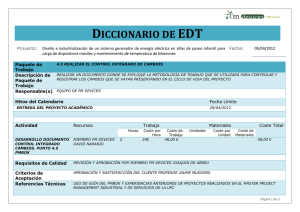

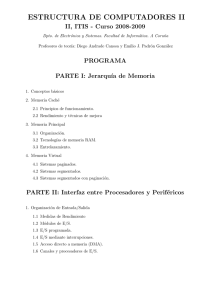

Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Organización de la Computadora Sistemas Operativos Andrés Felipe Barco Santa Pontificia Universidad Javeriana Febrero de 2010 Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arquitectura Arquitectura de Von Newumann Arquitectura El Sistema operativo provee abstracciones para que el hardware pueda ser operado sin tener que conocer los detalles de cómo son se realiza esa operación. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arquitectura Arquitectura de Von Newumann Arquitectura El Sistema operativo provee abstracciones para que el hardware pueda ser operado sin tener que conocer los detalles de cómo son se realiza esa operación. John Von Neumann “It is evident that the machine must be capable of storing in some manner not only digital information needed in a given computation..., but also the instructions wich govern the actual routines to be performed on the numerical dara” Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arquitectura Arquitectura de Von Newumann Arquitectura de Von Newumann Figura: Tomado de Operating Systems, 3 Edition, Gary Nutt Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Arithmetical Logical Unit La ALU realiza una serie de operaciones binarias tanto aritmeticas como lógicas, tales como; suma, resta y el AND lógico. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Arithmetical Logical Unit La ALU realiza una serie de operaciones binarias tanto aritmeticas como lógicas, tales como; suma, resta y el AND lógico. La unidad funcional realiza las operaciones. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Arithmetical Logical Unit La ALU realiza una serie de operaciones binarias tanto aritmeticas como lógicas, tales como; suma, resta y el AND lógico. La unidad funcional realiza las operaciones. Los registros retienen los operandos y resultados. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Arithmetical Logical Unit La ALU realiza una serie de operaciones binarias tanto aritmeticas como lógicas, tales como; suma, resta y el AND lógico. La unidad funcional realiza las operaciones. Los registros retienen los operandos y resultados. Los registros de estado reflejan los resultados de las operaciones de la unidad funcional. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Arithmetical Logical Unit Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Control Unit La unidad de control es la encargada de la secuencia de obtener una instrucción de memoria y ejecutarla. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Control Unit La unidad de control es la encargada de la secuencia de obtener una instrucción de memoria y ejecutarla. El contador de programa (PC) contiene la dirección de la próxima instrucción a ejecutar. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Control Unit La unidad de control es la encargada de la secuencia de obtener una instrucción de memoria y ejecutarla. El contador de programa (PC) contiene la dirección de la próxima instrucción a ejecutar. El registro de instrucción (IR) contiene una copia de la intrucción actual una vez se ha obtenido de memoria. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Control Unit La unidad de control es la encargada de la secuencia de obtener una instrucción de memoria y ejecutarla. El contador de programa (PC) contiene la dirección de la próxima instrucción a ejecutar. El registro de instrucción (IR) contiene una copia de la intrucción actual una vez se ha obtenido de memoria. Sus tres unidades lógicas son la unidad de obtención (fetch unit), unidad decodificadora (decode unit) y unidad de ejecución (execute unit). Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Control Unit Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Fetch-Execute Cycle PC = <machine start address>; Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Fetch-Execute Cycle PC = <machine start address>; IR = memory[PC] Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Fetch-Execute Cycle PC = <machine start address>; IR = memory[PC] haltflag = CLEAR; Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Arithmetical Logical Unit Control Unit Fetch-Execute Cycle Fetch-Execute Cycle PC = <machine start address>; IR = memory[PC] haltflag = CLEAR; while(haltFlag not SET during execution)f PC = PC + 1; execute(IR); IR = memory[PC]; g; Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Executable Memory Diseño de memoria Executable Memory La unidad de memoria primaria almacena tanto programas como los datos que estos usan mientras operan en la CPU. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Executable Memory Diseño de memoria Executable Memory La unidad de memoria primaria almacena tanto programas como los datos que estos usan mientras operan en la CPU. El registro de dirección de memoria (MAR) almacena la dirección de memoria a la cual se desea acceder. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Executable Memory Diseño de memoria Executable Memory La unidad de memoria primaria almacena tanto programas como los datos que estos usan mientras operan en la CPU. El registro de dirección de memoria (MAR) almacena la dirección de memoria a la cual se desea acceder. El registro de dato de memoria (MDR) almacena los datos que se escriben/leen a/desde la memoria. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Executable Memory Diseño de memoria Executable Memory La unidad de memoria primaria almacena tanto programas como los datos que estos usan mientras operan en la CPU. El registro de dirección de memoria (MAR) almacena la dirección de memoria a la cual se desea acceder. El registro de dato de memoria (MDR) almacena los datos que se escriben/leen a/desde la memoria. El registro de comando (Cmd) almacena la operación deseada (read/write). Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Executable Memory Diseño de memoria Diseño de memoria Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Devices Los dispositivos se unen al computador por medio de los buses. Cada dispositivo de entrada envia datos a los registros de la CPU. Cuando se usa esa información se envia desde la CPU a los dispositvos de salida. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Devices Los dispositivos se unen al computador por medio de los buses. Cada dispositivo de entrada envia datos a los registros de la CPU. Cuando se usa esa información se envia desde la CPU a los dispositvos de salida. El controlador del dispositivo provee un conjunto de componentes que la CPU puede manipular para hacer operar el dispositivo. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Devices Los dispositivos se unen al computador por medio de los buses. Cada dispositivo de entrada envia datos a los registros de la CPU. Cuando se usa esa información se envia desde la CPU a los dispositvos de salida. El controlador del dispositivo provee un conjunto de componentes que la CPU puede manipular para hacer operar el dispositivo. El dispositivo (entrada/salida) Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Device-Controller Relationship Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Device Controllers Motivación Un dispositivo requiere de mucha antención durante su operación. Si el software realizará esto, se necesitaria monitorear constantemente el dispositivo por lo cual se gastarı́an recursos. busy define si el dispositivo está ocupdado Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Device Controllers Motivación Un dispositivo requiere de mucha antención durante su operación. Si el software realizará esto, se necesitaria monitorear constantemente el dispositivo por lo cual se gastarı́an recursos. busy define si el dispositivo está ocupdado done define si la operación encargada al dispositivo a terminado Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Device Controllers Motivación Un dispositivo requiere de mucha antención durante su operación. Si el software realizará esto, se necesitaria monitorear constantemente el dispositivo por lo cual se gastarı́an recursos. busy define si el dispositivo está ocupdado done define si la operación encargada al dispositivo a terminado error define si ha habido algún error mientras se operaba Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Device Controllers Motivación Un dispositivo requiere de mucha antención durante su operación. Si el software realizará esto, se necesitaria monitorear constantemente el dispositivo por lo cual se gastarı́an recursos. busy define si el dispositivo está ocupdado done define si la operación encargada al dispositivo a terminado error define si ha habido algún error mientras se operaba command define que comando se ejecuta Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Device Controllers Motivación Un dispositivo requiere de mucha antención durante su operación. Si el software realizará esto, se necesitaria monitorear constantemente el dispositivo por lo cual se gastarı́an recursos. busy define si el dispositivo está ocupdado done define si la operación encargada al dispositivo a terminado error define si ha habido algún error mientras se operaba command define que comando se ejecuta Los regustros de datos son, naturalmente, para almacenar datos de entrada y salida Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Device Controller Interface Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Posibilidades El diseño anterior permite cubrir algunas funcionalidades. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Posibilidades El diseño anterior permite cubrir algunas funcionalidades. Direct Memory Access (DMA) Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Devices Device-Controller Relationship Device Controllers Device Controller Interface Posibilidades Posibilidades El diseño anterior permite cubrir algunas funcionalidades. Direct Memory Access (DMA) Memory-Mapped I/O Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Polling Método Antiguo El polling es el método en el cual el software esta haciendo un chequeo constante de los registros busy y done, averiguando si el dispositivo termino su trabajo. Situacion busy-wait en el procesador!!! Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Polling I/O Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Interrupts Método Moderno La arquitectura de Von Neumann ha sido modificada para incorporar las intrrupciones. Esto permitirá un uso mucho más eficiente de los recursos por medio del solapar el uso de estos. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Interrupts Método Moderno La arquitectura de Von Neumann ha sido modificada para incorporar las intrrupciones. Esto permitirá un uso mucho más eficiente de los recursos por medio del solapar el uso de estos. Interrup Request Un registro al interior de la CPU controla el hecho de que un dispositivo teminó su trabajo. Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Fetch-Execute Cycle with Interrupts while(haltFlag not SET during execution)f IR = memory[PC]; PC = PC + 1; execute(IR); Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Fetch-Execute Cycle with Interrupts while(haltFlag not SET during execution)f IR = memory[PC]; PC = PC + 1; execute(IR); if(InterrupRequest) f memory[0] = PC; PC = memory[1]; g; Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Interrup Handler Interrupt Handlerf saveProcessorState(); Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Interrup Handler Interrupt Handlerf saveProcessorState(); for (i=0, i<Number devices; i++) if (device[i].done == 1 ) goto device handler(i); /* Something wrong if we get here */ g; Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Disabling Interrupts if(InterrupRequest && InterruptEnabled) f /* Interrupt current process */ memory[0] = PC; PC = memory[1]; g; Andrés Felipe Barco Santa Organización de la Computadora Introducción Unidad Central de Procesamiento Memoria Primaria I/O Devices Interrupts Polling Polling I/O Interrupts Fetch-Execute Cycle with Interrupts Interrup Handler Disabling Interrupts Fin de la Clase Nos vemos en la próxima!!! Andrés Felipe Barco Santa Organización de la Computadora