Tema 2: Arquitectura del repertorio de instrucciones Visión del

Anuncio

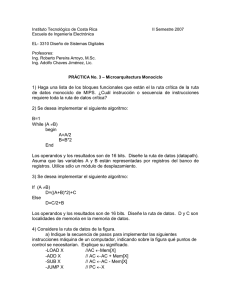

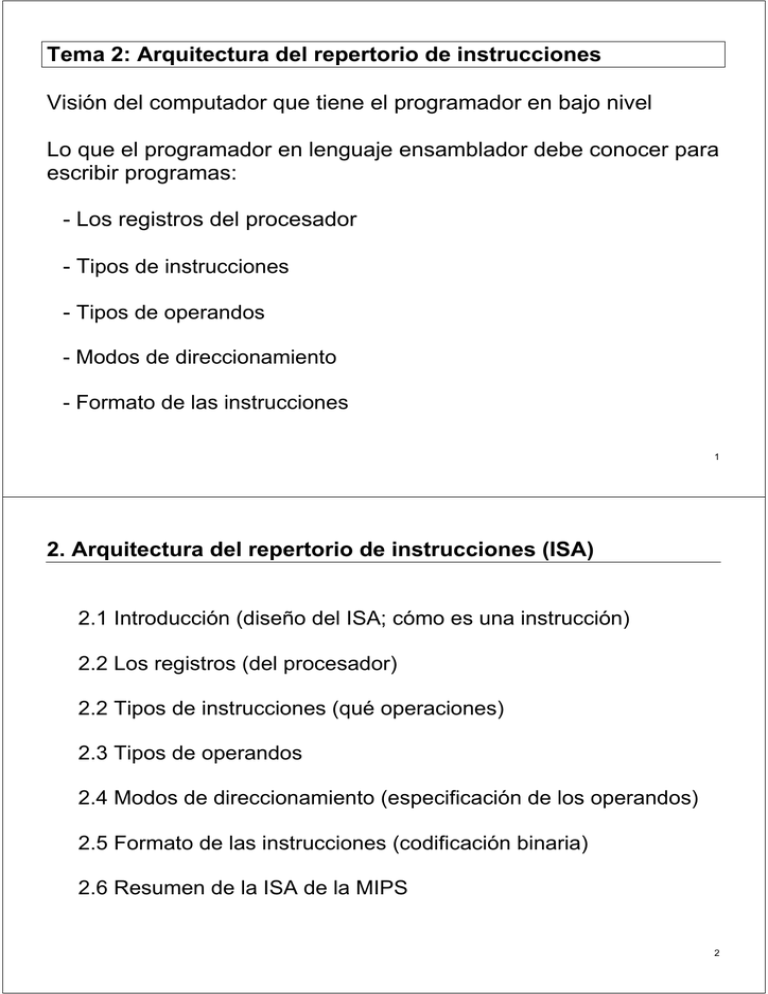

Tema 2: Arquitectura del repertorio de instrucciones Visión del computador que tiene el programador en bajo nivel Lo que el programador en lenguaje ensamblador debe conocer para escribir programas: - Los registros del procesador - Tipos de instrucciones - Tipos de operandos - Modos de direccionamiento - Formato de las instrucciones 1 2. Arquitectura del repertorio de instrucciones (ISA) 2.1 Introducción (diseño del ISA; cómo es una instrucción) 2.2 Los registros (del procesador) 2.2 Tipos de instrucciones (qué operaciones) 2.3 Tipos de operandos 2.4 Modos de direccionamiento (especificación de los operandos) 2.5 Formato de las instrucciones (codificación binaria) 2.6 Resumen de la ISA de la MIPS 2 2.1 Introducción Diseño del ISA Es un nivel complicado de diseñar Al hacerlo, hay que tener en cuenta: el software (compilador de LANs) que tiene que soportar la estructura del hardware que lo soportará Es la conexión entre ambos niveles: lenguaje que ambos tienen que entender 3 Es un punto de encuentro de el diseñador de la estructura y el programador a bajo nivel del computador (o el escritor del compilador): - el diseñador de la estructura ve el nivel ISA como la funcionalidad que ésta debe dar al programador - el programador se hace consciente de la estructura definida por el diseñador: cómo usa los registros, qué operaciones tiene la ALU, cómo accede a memoria y qué tipos de datos tiene Objetivo común de los diseñadores de computadores: – encontrar un lenguaje que haga fácil la construcción del hardware y del software (el compilador) – maximizar el rendimiento y minimizar el coste 4 Cómo es una instrucción Los programas en este nivel se expresan en lenguaje ensamblador swap:muli $2, $5,4 add $2, $4,$2 lw $16, 4($2) sw $16, 0($2) jr $31 El lenguaje ensamblador es ‘equivalente’ al lenguaje máquina 00000000101000010000000000011000 00000000100011100001100000100001 10001100011000100000000000000000 10101100011000100000000000000100 00000011111000000000000000001000 5 El lenguaje máquina, lo interpreta y ejecuta directamente el hardware del computador Formado por instrucciones (máquina) simples Instrucción máquina = especifica una operación que debe realizar el procesador 6 Una instrucción especifica tanto la operación a realizar como los operandos a utilizar en esta operación (1) Las operaciones son básicas (las que realiza la estructura del computador): - aritmético-lógicas (de la ALU): suma, resta, AND, OR, desplazamientos - movimientos de datos entre registros y memoria (2) Los operandos: objetos con los que se opera (fuentes) y el resultado de la operación (destino); estarán en registro o memoria 7 Sintaxis típica de una instrucción en lenguaje ensamblador Ejemplo: Lenguaje ensamblador del procesador MIPS R2000/3000 4 campos básicos: etiqueta, nemónico de la instrucción, operandos (2 fuentes y 1 destino) y comentarios (opcional) 8 Fíjate que el número de operandos fuente de una instrucción aritmética como la suma son dos Esto permite tener una ALU más sencilla Para evaluar expresiones aritméticas que aparecen en los lenguajes de alto nivel (LAN) habrá que ejecutar varias instrucciones aritméticas de bajo nivel Ejemplo: la sentencia de alto nivel a=b+c+d+e se implementa con la secuencia de instrucciones de bajo nivel: add a, b, c add a, a, d add a, a, e Esto es un ejemplo de la diferencia de nivel de abstracción de un LAN y un lenguaje ensamblador ó máquina (1 instrucción de alto nivel equivale a 3 de bajo) 9 2.2 Los registros Pequeña memoria rápida en el procesador para almacenamiento temporal de información Su número y función varían entre los distintos diseños de arquitecturas del repertorio de instrucciones Hoy en día, casi todas las arquitecturas son con registros de propósito general: conjunto de registros manejables por el programador, para contener operandos y especificar direcciones de memoria Este no es el único tipo de arquitectura Æ veamos qué tipos de arquitectura hay en función de cómo se pueden especificar en una instrucción los operandos 10 Tipos de arquitecturas del repertorio de instrucciones Una primera clasificación (histórica) según el tipo de almacenamiento temporal para los operandos Esto determina el número de operandos explícitos por instrucción Almacenamiento Ejemplos temporal 1. Pila HP 3000 2. Acumulador PDP-8 Motorola 6809 3. Conjunto de IBM 360 registros DEC VAX,MIPS Operandos explícitos 0 1 Operando destino en … Pila Acumulador 2ó3 Registros o memoria 11 Dónde están los operandos, en los distintos tipos de arquitectura: - arquitectura de pila: implícitamente en la cima de la pila (memoria) - arquitectura de acumulador: implícitamente uno de los fuente y el destino en el registro acumulador y el otro fuente en memoria - arquitectura de registros: en registros o posiciones de memoria, 2 ó 3 operandos explícitos Según el tipo de arquitectura de registros: i) se podrá hacer operaciones ALU con datos en memoria, ó ii) habrá que cargarlos en registros para operar con ellos (MIPS) 12 Veamos como se traduciría la secuencia de código C = A + B para las 3 clases de arquitectura: (A, B y C son variables: los valores de A, B, C están en memoria y los valores de A y B no cambian) Pila PUSH A PUSH B ADD POP C Acumulador LOAD A ADD B STORE C Registro LOAD R1, A ADD R1, B STORE C, R1 13 (1) Pila Ventajas: - evaluación sencilla de expresiones (polaca inversa) - instrucciones cortas: como máximo se especifica un operando Inconveniente: - muchas transferencias con memoria (2) Acumulador Ventajas: - minimización de los estados internos de la máquina - instrucciones cortas: sólo se especifica un operando Inconveniente: - muchas (menos que las de pila) transferencias con memoria 14 (3) Registros Las arquitecturas de registros dominan hoy día Ventajas: - Los registros son fáciles de usar por el compilador, pueden ser asociados con las variables, con lo que se consigue: • una disminución del tiempo de ejecución: reducción del tráfico de memoria (los registros son más rápidos) • una mejor densidad de código: menos bits necesarios especificar un registro que una dirección de memoria 15 Veamos una clasificación de las arquitecturas de registros atendiendo a: (1) el número de operandos (2 ó 3) que se especifican explícitamente las instrucciones aritmético-lógicas Si se especifican dos operandos, uno de ellos es fuente y destino (2) el número de operandos que pueden estar en memoria en las instrucciones aritmético-lógicas (de 0 a 3) 16 Las posibles combinaciones de estas 2 características son: Máximo número de operandos explícitos por instrucción ALU (1) 2 3 2 Número de operandos que pueden estar en memoria por instrucción ALU (2) 0 0 1 2 3 2 3 Ejemplos IBM RT-PC SPARC, MIPS PDP-10, Motorola 68000, IBM 360 PDP-11 VAX 17 Los tres tipos más comunes de arquitecturas de registro atendiendo a estas dos características son: Tipo Registro-registro (3,0) Cargaalmacenamiento Registromemoria (2,1) Memoriamemoria (3,3) Ventajas Codificación simple de instrucciones de longitud fija Nºciclos/instrucción similares Fácil codificación de las instrucciones No hay que cargar los datos en registros Inconvenientes Necesarias más instrucciones que arquitecturas con referencias a memoria Se destruye un operando Variación en el tamaño de las instrucciones 18 Registros del procesador Son de dos tipos: (1) visibles al programador en lenguaje ensamblador: puede ser utilizados explícitamente en una instrucción (2) de control y de estado: usados por (a) la unidad de control para controlar el funcionamiento de la CPU: proceso de instrucciones y accesos a memoria (b) el SO para controlar la ejecución de los programas 19 (1) Registros manejables por el programador: Junto con la ALU forman el camino de datos Se utilizan para contener los operandos de las instrucciones máquina o para especificar una dirección de memoria Pueden ser referenciados explícitamente en las instrucciones máquina Por ejemplo en la MIPS mediante un número: add $9, $17, $2 ó lw $16, 4($2) 20 Los compiladores pueden usarlos para asociarlos con variables y disminuir el tráfico con memoria El ejemplo anterior (a=b+c+d+e) add a, b, c add a, a, d add a, a, e en realidad se implementa asociando las variables con registros: a - $8, b - $9, c - $10, d - $11, e - $12, de forma que el compilador generaría: add $8, $t9, $10 add $8, $8, $11 add $8, $8, $12 21 Cuestiones de diseño de los registros manejables por el programador: (a) Respecto al uso que le puede dar el programador: (1) de propósito general: pueden contener datos y especificar direcciones (MIPS) (2) de datos: sólo pueden contener datos (3) de dirección: sólo para especificar direcciones (modos de direccionamiento indirecto ó base+desplazamiento) (b) Número de registros La experiencia dice que entre 8 – 32 Menos Æ no suficientes para contener variables Æmuchas referencias a memoria Más Æ no reduce notablemente las referencias a memoria y aumenta la longitud de las instrucciones (más número de bits para especificar los registros) 22 (c) Tamaño de los registros Habrá que decidir si todos los registros tienen el mismo tamaño (MIPS) o no (1) los que han de contener direcciones, lo suficientemente largo para contener direcciones completas (2) los que han de contener datos, lo suficientemente largos para contener la mayoría de los tipos de datos: una palabra A menudo es posible usar dos registros de datos contiguos como uno solo para contener valores de doble longitud (MIPS: los registros para punto flotante doble precisión) 23 (2) Registros de control y estado del funcionamiento de la CPU: En la mayoría de las máquinas, no manejables por el usuario Algunos serán manejables por instrucciones ejecutadas en modo supervisor (control del SO) (a) Registros de control (1) Contador de programa: contiene la dirección de la instrucción a ejecutar (2) Registro de instrucción: contiene la instrucción a ejecutar (3) Registro de dirección de memoria: contiene la dirección de una posición de memoria para ser leída o escrita (4) Registro de buffer de memoria: contiene la palabra de datos a escribir en memoria o que ha sido leída 24 En esta figura vemos los registros de control 25 (b) Registro de estado (del programa en ejecución) Contiene los códigos de condición y otra información de estado (i) Los códigos de condición (indicadores o ‘flags’) son valores binarios (bits) que especifican si se ha producido una determinada circunstancia en una operación ALU Pueden ser de signo, cero, acarreo, overflow,… Son utilizados implícitamente en las instrucciones de salto condicional (ii) Además de los códigos de condición la palabra de estado puede contener bits para: (1) habilitación/deshabilitación de interrupciones (2) modo supervisor/usuario (de funcionamiento de la CPU) 26 Ejemplos de organización de registros: 2 microprocesadores contemporáneos (1978):Motorola MC68000, Intel 8086 27 Motorola MC68000: Registros de 32 bits: 8 de datos y 9 de dirección (1) Los de datos: También se usan como registros índice (un modo de direccionamiento) Permiten operaciones con 8,16 y 32 bits según determine el código de operación (MIPS) (2) Los de direcciones: A7 y A7’ punteros de pila para usuarios y para SO respectivamente (3) Contador de programa de 32 bits y registro de estado de 16 Decisiones de diseño: (1) repertorio de instrucciones regular sin registros de uso especial (2) división en dos grupos, ahorro de 1 bit (compromiso razonable entre generalidad total y código más compacto) 28 Intel 8086 Enfoque diferente en la organización de los registros: cada registro tiene un uso particular aunque algunos pueden tener uso general 4 registros de datos de 16 bits, direccionables también como bytes Uso general en algunas instrucciones e implícito en otras, p.e. la multiplicación usa siempre el acumulador Registros de segmento uso dedicado e implícito, apuntan a los segmentos de datos, código y pila (base + desplazamiento) Los índice implícitos en algunas operaciones: contienen desplazamientos dentro de cada segmento(base + desplazamiento) Decisiones de diseño: codificación compacta Æ flexibilidad reducida 29 Intel 80386 Microprocesador de 32 bits, diseñado como una ampliación del 8086 (16 bits) Conserva la organización de registros original integrada en la nueva organización Æ proporciona compatibilidad ascendente para los programas del 8086 Tuvieron que limitar la flexibilidad al diseñar la organización de los registros El Pentium tiene la misma organización de registros que el 386 30 Características del banco de registros del MIPS R2000 31 (1) Banco de registros de propósito general: 32 Registros de 32 bits (CPU) Se identifican como $0 a $31. Ejemplo: add $2, $3, $4 ($2=$3+$4) El registro $0 tiene permanentemente el valor 0 (2) Dos registros especiales de 32 bits (CPU) HI y LO: almacenan los resultados de multiplicaciones y divisiones. (3) Banco de registros de reales (FPU) 32 registros de 32 bits que puede utilizarse como: - 32 registros de 32 bits con formato IEEE 754 de simple precisión. Se identifican por $f0, $f2, $f4, …, $f30 - 16 registros de 64 bits con formato IEEE 754 de doble precisión. Se identifican por $f0, $f2, $f4, …, $f30 32 Convención en el uso de los registros en la MIPS Nombre del registro zero at v0 v1 a0 a1 a2 a3 t0..t7 s0..s7 t8, t9 k0, k1 gp sp fp ra Número Uso 0 1 2 3 4 5 6 7 8..15 16..23 24, 25 26, 27 28 29 30 31 Constante 0 Reservada para ensamblador Para devolver resultados de funciones “ Argumento 1 a una rutina Argumento 2 “ Argumento 3 “ Argumento 4 “ Temporal (no se guarda valor entre llamadas) Temporal (el valor se guarda entre llamadas) Temporal (no se guarda valor entre llamadas) Reservado para el kernel del sistema operativo Puntero al área global (apunta al bloque de datos) Puntero de pila Puntero de marco de pila Dirección de retorno, usado por llamadas a rutina 33 Esta es la visión de los registros de la MIPS que nos da el PCSpim 34 2.2 Tipos de instrucciones Las instrucciones soportadas por la mayoría de las arquitecturas pueden clasificarse según la siguiente tabla: 35 (I) Aritméticas y lógicas Aritméticas En todas las máquinas La mayoría suma, resta, multiplicación y división Tipos de operandos: - todas con enteros con signo - algunas con enteros sin signo (MIPS) - a menudo con punto flotante (MIPS) - a veces para BCD Otras operaciones aritméticas posibles: - valor absoluto - cambio de signo - incremento y decremento 36 Lógicas En todas las máquinas Operaciones sobre datos lógicos: operaciones lógicas bit a bit Operaciones lógicas en la MIPS: AND, OR, NOR y XOR Ejemplo: sean los valores en registros: R1 = 10100101 y R2 = 00001111 R1 AND R2 = 00000101 Además operaciones de desplazamiento (MIPS) y rotación: 37 38 Examples of ALU Instructions Instruction Meaning MULF A, B, C multiply the32-bit floating point values at mem loc’ns. A and B, store at C VAX11 nabs r3, r1 Store abs value of r1 in r3 Machine PPC601 ori $2, $1, 255 Store logical OR of reg $1 with 255 into reg $2 MIPSR3000 DEC R2 Decrement the 16-bit value stored in reg R2 DECPDP11 SHL AX, 4 Shift the16-bit value in reg AX left by 4 bit pos’ns. Intel8086 39 (II) Transferencia de datos Operación: copiar un dato de un sitio a otro Existe en todas las máquinas Debe especificar: - operandos fuente y destino (en registro o memoria) - longitud datos a transferir Opción de diseño: dónde especifico el tamaño del dato: - en el código de operación (MIPS: lb ó lw) - en el operando (VAX) Operación muy sencilla en el caso registro-registro (no en la MIPS) Si es con memoria, habrá que calcular la dirección del dato y hacer el acceso a memoria (más lenta que los registros) 40 Examples of Data Movement Instructions Instruction Meaning MOV A, B Move 16 bits from memory location A to Location B VAX11 Load accumulator A with the byte at memory location Addr M6800 Move 32-bit data from memory location A to register R3 PPC601 Load the 32-bit integer at memory location addr into register $3 MIPS R3000 Move 16-bit data from R4 to output port dout DEC PDP11 Load a byte from in port KBD to accumulator Intel Pentium LDA A, Addr lwz R3, A lw $3, addr mov R4, dout IN AL, KBD Machine 41 (IV) Control (de flujo de ejecución) En las instrucciones vistas hasta ahora la instrucción que se ejecutará a continuación es la siguiente en memoria Las instrucciones de control cambian esta secuencia de ejecución (ruptura de secuencia) Para ello tendrán que especificar que instrucción se ejecutará a continuación La operación que realiza la CPU es actualizar el registro contador de programa (PC) para que contenga la dirección en memoria de la próxima instrucción a ejecutar 42 Tipos de rupturas de secuencia: (1) Bifurcaciones (branch): rupturas de secuencias condicionales La condición puede ser el valor de un bit de estado, la comparación (con cero) del valor de un registro (MIPS) ó la comparación de los valores de 2 registros (MIPS) (2) Saltos (jump): rupturas de secuencia no condicionales (3) Llamadas y retornos de procedimientos: para ejecutar un procedimiento y retornar al programa principal 43 (V) Sistema En todas las máquinas Llamadas al sistema operativo (MIPS:syscall) para que realice algún servicio: entrada/salida, detener la ejecución del programa,… en la MIPS (VI) Punto flotante 44 Operaciones con reales En casi todas las máquinas La MIPS las tiene (VII) Decimal Para operar con datos BCD No las tiene (VIII) Cadenas Para copiar o mover cadenas de caracteres No las tiene 45 Veamos un resumen del repertorio de instrucciones de la MIPS: MIPS IV Instruction Set (1) Arithmetic and Logical Instructions (2) Constant-Manipulating Instructions (3) Comparison Instructions (4) Branch Instructions (5) Jump Instructions (6) Load Instructions (7) Store Instructions (8) Data Movement Instructions (9) Floating-Point Instructions (10) Exception and Interrupt Instructions 46 (1) Arithmetic and Logical Instructions Addition (with overflow) add rd, rs, rt Put the sum of registers rs and rt into register rd Addition immediate (with overflow) addi rt, rs, imm Put the sum of register rs and the sign-extended immediate into register rt If the addition results in 32-bit 2’s complement arithmetic overflow then the destination register is not modified and an Integer Overflow exception occurs 47 AND and rd, rs, rt Put the logical AND of registers rs and rt into register rd AND immediate andi rt, rs, imm Put the logical AND of register rs and the zero-extended immediate into register rt Divide div rs, rt Divide register rs by register rt. Leave the quotient in register lo and the remainder in register hi Multiply mult rs, rt Multiply registers rs and rt. Leave the low-order word of the product in register lo and the high-order word in register hi 48 NOR nor rd, rs, rt Put the logical NOR of registers rs and rt into register rd OR or rd, rs, rt Put the logical OR of registers rs and rt into register rd OR immediate ori rt, rs, imm Put the logical OR of register rs and the zero-extended immediate into register rt 49 Shift left logical sll rd, rt, shamt Shift left logical variable sllv rd, rt, rs Shift right arithmetic sra rd, rt, shamt Shift right arithmetic variable srav rd, rt, rs Shift right logical srl rd, rt, shamt Shift right logical variable srlv rd, rt, rs Shift register rt left (right) by the distance indicated by immediate shamt or the register rs and put the result in register rd 50 Subtract (with overflow) sub rd, rs, rt Put the difference of registers rs and rt into register rd. If the subtraction results in 32-bit 2’s complement arithmetic overflow then the destination register is not modified and an Integer Overflow exception occurs Exclusive OR xor rd, rs, rt Put the logical XOR of registers rs and rt into register rd. XOR immediate xori rt, rs, imm Put the logical XOR of register rs and the zero-extended immediate into register rt 51 (2) Constant-Manipulating Instructions Load upper immediate lui rt, imm Load the lower halfword of the immediate imm into the upper halfword of register rt. The lower bits of the register are set to 0 Cargar una palabra inmediata en un registro No hay una instrucción máquina para ello Se puede hacer con un lui y un ori Por ejemplo lui $t0, 0x1234 # t0=0x12340000 ori $t1, $t0, 0x5678 # t1=0x12340000 OR 0x00005678 cargaría la palabra 0x12345678 en el registro t1 52 (3) Comparison Instructions Set less than slt rd, rs, rt Set register rd to 1 if register rs is less than rt, and to 0 otherwise Set less than immediate slti rt, rs, imm Set register rt to 1 if register rs is less than the sign-extended immediate, and to 0 otherwise 53 (4) Branch Instructions Branch on equal beq rs, rt, label Conditionally branch to instruction specified by label if register rs equals rt Branch on greater than equal zero bgez rs, label Conditionally branch to instruction specified by label if register rs is greater than or equal to 0 Branch on greater than zero bgtz rs, label Conditionally branch to instruction specified by label if register rs is greater than 0 54 Branch on less than equal zero blez rs, label Conditionally branch to instruction specified by label if register rs is less than or equal to 0 Branch on less than zero bltz rs, label Conditionally branch to instruction specified by label if register rs is less than 0 Branch on not equal bne rs, rt, label Conditionally branch to instruction specified by label if register rs is not equal to rt 55 (5) Jump instructions Jump j target Unconditionally jump to the instruction at target Jump and link jal target Unconditionally jump to the instruction at target; save the address of the next instruction in register $ra Jump register jr rs Unconditionally jump to the instruction whose address is in register rs 56 (6) Load Instructions Load byte lb rt, address Load unsigned byte lbu rt, address Load the byte at address into register rt; the byte is sign-extended by lb, but not by lbu 57 Load halfword lh rt, address Load unsigned halfword lhu rt, address Load the 16-bit quantity (halfword) at address into register rt; the halfword is sign-extended by lh, but not by lhu Load word lw rt, address Load the 32-bit quantity (word) at address into register rt 58 (7) Store Instructions Store byte sb rt, address Store the low byte from register rt at address Store halfword sh rt, address Store the low halfword from register rt at address Store word sw rt, address Store the word from register rt at address 59 (8) Data Movement Instructions Move from hi mfhi rd Move from lo mflo rd Move the hi (lo) register to register rd Move to hi mthi rs Move to lo mtlo rs Move register rs to the hi (lo) register Mover un registro a otro No existe una instrucción máquina para ello Se puede hacer con un add rd, rs, $zero #rd=rs+0 60 (9) Floating-Point Instructions No las veremos (10) Exception and Interrupt Instructions System call syscall Register $v0 contains the number of the system call (see Figure A.17) provided by SPIM 61 2.4. Tipos de operandos El tipo de un dato viene determinado por la operación que se realice con él Categorías generales más importantes: (1) (2) (3) (4) Direcciones Números Caracteres Datos lógicos 62 (1) Direcciones En las instrucciones de control de secuencia el operando es una dirección de memoria de la instrucción a la que se salta Pueden considerarse como números enteros sin signo En la MIPS serán números de 32 bits 63 (2) Números Son usuales tres tipos de datos numéricos: (i) Enteros - con signo, representados en complemento a 2 - sin signo Tamaños: byte, media palabra (half-word), palabra (word) (ii) Punto flotante IEEE 754: simple precisión (32 bits) y doble precisión (64 bits) (iii) Decimal En BCD (Decimal codificado en binario): - empaquetado: 2 dígitos decimales por byte. Ejemplo: 01001001 -> 49 - no empaquetado: 1 dígito/byte. Ejemplo: 00000100 00001001 -> 49 MIPS no los tiene 64 (3) Caracteres Códigos binarios para representar caracteres mediante secuencias de bits Estándares: - ASCII de 8 bits - EBCDIC de 8 bits (utilizado por los grandes computadores IBM) MIPS no tiene instrucciones específicas para tratamiento de caracteres (4) Datos lógicos Un objeto de n bits es considerado como n datos de 1 bit Utilizados en operaciones lógicas 65 Formatos numéricos del Pentium II 66 2.4. Modos de direccionamiento Distintas formas que tiene la arquitectura para especificar los operandos Objetivos: - referenciar un rango elevado de posiciones de memoria principal (número de bits para el direccionamiento limitado) - dar soporte a las estructuras de datos de alto nivel Puede ser: - para datos, sobre los que opera la instrucción - para instrucciones, especifica la dirección de la siguiente instrucción a ejecutar (en instrucciones de control) Veremos: - aspectos del almacenamiento de datos en memoria: alineación y orden de los bytes - los distintos modos de direccionamiento 67 2.4.1. Necesidades de direccionamiento Dónde puede estar un operando: - en la propia instrucción - en un registro - en memoria 68 A simple vista, lo lógico sería que en la propia instrucción se especificase el operando, su dirección en memoria o el registro que lo contiene No siempre lo más indicado por las siguientes razones: - ahorro de espacio: direccionamientos indirectos, base+desplazamiento e indexado, ocupan menos bits que una dirección - código reubicable: con los direccionamientos relativos a una dirección base (almacenada en un registro) - estructuras de datos: direccionamientos relativos a la dirección base (en un registro) de la tabla, con un desplazamiento (en un registro o una constante), direccionamientos auto-incremento/decremento y escalado o índice 69 2.4.2. Interpretación de las direcciones de memoria ¿Qué objeto es accedido dada una dirección y una longitud? Dos convenios para ordenar en memoria los bytes de un objeto multibyte: - little endian: el byte en la dirección menos significativa es el del extremo menos significativo - big endian: el byte en la dirección menos significativa es el del extremo más significativo 70 Convenios para clasificar los bytes de una palabra: - Little Endian: La dirección de un dato es la dirección de la parte menos significativa del dato - Big Endian: La dirección de un dato es la dirección de la parte más significativa del dato Aspecto importante cuando se intercambia información entre distintas máquinas 71 Alineación de los datos en memoria Algunas arquitecturas exigen que los objetos mayores de un byte estén alineados en memoria Definición: un acceso a un objeto de tamaño t bytes en el byte de dirección D se alinea si D mod t = 0 (mod: resto de la división D/t) Es decir, la dirección del objeto debe ser múltiplo de su tamaño en bytes 72 El alineamiento permite simplificar los accesos a memoria: hardware más sencillo y la misma velocidad de acceso para cualquier palabra en memoria Ejemplo ‘little-endian’: 73 Ejemplo: doble palabra alineada y no alineada 74 2.4.3. Descripción de los distintos modos de direccionamiento 75 Para especificar algunos modos de direccionamiento usaremos la siguiente notación: A = especificación de una dirección de memoria (Address) R = especificación de un registro (Register) EA = dirección real del operando en memoria (Effective address) (X) = contenido de la posición de memoria X o del registro X 76 (1) Direccionamiento por registro El campo de dirección especifica un registro donde está el operando OPERANDO = (R) n bits del campo de dirección necesarios para referenciar 2n registros Ventajas : campo de direcciones pequeño y no hay accesos a memoria Desventaja: espacio de posiciones limitado Ejemplo: add r4, r3 equivale a r4 = r4 + r3 77 (2) Direccionamiento inmediato El operando está en la propia instrucción OPERANDO = Operand Para definir constantes cortas Ejemplo: add r4, #5 equivale a r4 = r4 + 5 78 Número en complemento a 2, se hace extensión del signo al cargarlo en un registro Ventaja: una vez captada la instrucción, no se necesitan más referencias a memoria Desventaja: pocos bits para codificar el dato VAX permite distintos tamaños para operandos inmediatos: 6, 8, 16, 32 y 64 bits MIPS solo permite 16 bits 79 (3) Direccionamiento directo El campo de dirección contiene la dirección efectiva del operando EA = A Muy sencillo, usada en las 1ªs computadoras Desventaja: limitación del rango de direcciones por el tamaño del campo Ejemplo: add r1, (100) equivale a r1 = r1 + M[100] 80 Direccionamiento indirecto (por memoria o por registro) Solución a la limitación del direccionamiento directo (4) Direccionamiento indirecto por registro Se especifica un registro donde está la dirección del operando EA = (R) Supera la limitación del nº de bits para especificar la dirección y un solo acceso a memoria para obtener el operando Ejemplo: add r2, (r5) equivale a r2 = r2 + M[r5] 81 (5) Direccionamiento indirecto por memoria El campo de direcciones contiene la dirección de una palabra donde está la dirección del operando EA = (A) Desventaja: dos accesos a memoria, para obtener el operando Ejemplo: add r1, @(100) equivale a r1 = r1 + M[M[100]] 82 (6) Direccionamiento base + desplazamiento Combina posibilidades del directo (facilidad de uso) y del indirecto por registro (menos bits para especificar dirección) Habrá que especificar un registro y un valor. La suma del contenido del registro y el valor es la dirección del operando EA = (R) + A Ejemplo: add r4,28(r1) equivale a r4 = r4 + M[28+r1] Para tratar vectores: el registro puede apuntar al principio del vector y el desplazamiento selecciona el elemento correspondiente 83 (7) Direccionamiento relativo al contador de programa Caso particular de direccionamiento base + desplazamiento El registro referenciado implícitamente es el contador de programa El campo de direcciones se trata como un número en complemento a 2, y representa un desplazamiento relativo al PC Se utiliza para realizar saltos condicionales (concepto de localidad) 84 (8) Direccionamiento indexado La dirección del operando es la suma de dos registros Para acceder a vectores de forma más versátil que base + desplazamiento. Un registro contiene la base del vector y el otro el índice del elemento correspondiente Ejemplo: add r3, (r1+r2) equivale a r3= r3+M[r1+r2] 85 (9) Direccionamiento autoincremento Indirecto por registro con autoincremento del mismo Ejemplo: add r1,(r3)+ equivale a r1= r1 + M[r3] r3=r3+d (d:tamaño del elemento) (10) Direccionamiento autodecremento Igual pero se autodecrementa el registro (11) Direccionamiento escalado o índice Para soportar tratamientos de arrays Ejemplo: add r1, 50(r2)[r3] equivale a r1=r1+M[50+r2+r3*d] donde d:tamaño del elemento del array 86 Los cinco modos de direccionamiento del MIPS son: (1) Direccionamiento inmediato El operando se encuentra codificado en la propia instrucción, representado como dato inmediato 87 (2) Direccionamiento a registro El operando está en un registro cuyo identificador se encuentra codificado en la instrucción 88 (3) Direccionamiento base (+desplazamiento) La dirección efectiva del operando se obtiene sumando un desplazamiento que se encuentra en la instrucción con una dirección base que se encuentra en un registro especificado también por la instrucción 89 (4) Direccionamiento relativo al contador de programa Es un caso particular del direccionamiento base (+desplazamiento) donde el registro que contiene la dirección base es de forma implícita el PC y el desplazamiento es de instrucciones (4 posiciones de memoria) 90 Este modo de direccionamiento se utiliza en instrucciones de bifurcación Ya que el desplazamiento es de 16 bits, este modo de direccionamiento permite saltar dentro del rango de palabras ±215 respecto a la instrucción Esto es suficiente para implementar bucles y sentencias ‘if’ Este modo de direccionamiento, especifica un salto relativo (número de instrucciones) a la instrucción de bifurcación 91 (5) Direccionamiento pseudodirecto La dirección se calcula concatenando los 4 bits más significativos del PC con la dirección de 26 bits especificada en la instrucción y dos ceros Este modo de direccionamiento permite saltar más allá que el anterior 92 2.5. Formato de las instrucciones Representación de las instrucciones en el computador Mediante 0s y 1s: una instrucción máquina es un número Cómo se agrupan en distintos campos que especificar la operación y los operandos Instrucción máquina = combinación de números (valores de los campos) 93 Tamaño de las instrucciones: aspecto básico del diseño del formato Compromiso entre: - repertorio de instrucciones potente (más operaciones, más operandos, más modos de direccionamiento y mayor rango de direcciones (más registros)): más bits para codificar - programas cortos: instrucciones cortas y de longitud variable - sencillez del hardware de captación y decodificación de las instrucciones: tamaño de las instrucciones fijo e igual al tamaño de la palabra de la máquina Los direccionamientos implícito e indirecto, permiten acortar el tamaño de la instrucción 94 Codificación de los modos de direccionamiento Según el número de modos de direccionamiento que tenga una arquitectura: 95 Características de los formatos de instrucción que deben tener las arquitecturas: - Cada computador tiene unos pocos formatos: cada instrucción se ajusta a uno de ellos. Cuantos menos más sencilla la unidad de control - Son sistemáticos: campos del mismo tipo tienen la misma longitud y ocupan el mismo sitio dentro de la instrucción (código de operación el primero). Simplifica la decodificación de la instrucción 96 Ejemplos de formatos de instrucciones IBM 360 16 registros de tipo general: 0 – 15 Palabra de 32 bits Modos de direccionamiento del computador: - inmediato (8 bits) - registro: Ri (4 bits) - almacenamiento (base + desplazamiento): Bi (registro base), Di (desplazamiento de 12 bits) - indexado: Xi (registro índice), Bi (registro base), Di (desplazamiento) Tiene 5 formatos de instrucción, según los modos de direccionamiento 2 o 3 operandos explícitos, cada uno mediante un modo de direccionamiento determinado 97 98 Veamos ejemplos de instrucciones (RR, RS y SI) del IBM 360: Especificación de las instrucciones: Descripción Código mnemónico Suma ADR normalizada larga Salta si BXH índice alto Movimiento MVI inmediato Código Formato Especificación de operación instrucc. los operandos 2A RR R1, R2 86 RS R1, R3, D2(B2) 92 SI D1(B1), inmediato ADR 3, 4 equivale a 0x2A34 BXH 5, 8, X’6B8’(7) equivale a 0x865876B8 MVI X’A49’(6), X’3F’ equivale a 0x923F6A49 99 El VAX Formato de instrucción muy flexible: código de operación de 8 bits, seguido de un máximo de cinco especificadores de operando: 100 Cada especificador de operando se compone de dos o tres partes: 1. Código del modo de direccionamiento (4 bits): - 5: registro 0xC: base + desplazamiento (de 16 bits) 0xA: base + desplazamiento (de 8 bits) Para especificar un operando inmediato los 2 bits más significativos son 00 y los 6 bits restantes se utilizan para codificar el valor del operando 2. especificación de registro (4 bits) 3. (opcional) especifica un desplazamiento en el direccionamiento base + desplazamiento (8, 16 ó 32 bits) Veamos algunos ejemplos de instrucciones del VAX: 101 102 Ejemplos: Dar la instrucción máquina equivalente a: CLRL R13 equivale a 0xD45D MOVW 362(R3), 67(R12) equivale a 0xB0C36A01AC43 ADDL3 #58, R1, 55(R11) equivale a 0xC13A51AC37 103 Formatos de instrucción de la MIPS 3 formatos de instrucción de 32 bits: 104 Los tipos de instrucciones en cada formato son: - Formato tipo R: utilizado por las instrucciones aritméticas y lógicas que no tienen operandos inmediatos - Formato tipo I: utilizado por las instrucciones de transferencia, las de salto condicional (bifurcación) y las instrucciones con operandos inmediatos - Formatos tipo J: utilizado por las instrucciones de salto Veamos ejemplos de los distintos formatos: 105 1. Tipo R - op: operación básica de la instrucción, tradicionalmente llamada código de operación - rs: primer registro operando fuente - rt: segundo registro operando fuente - rd: registro operando destino, donde se almacena el resultado de la operación - shamt: tamaño del desplazamiento (shift amount) - funct: función. Este campo selecciona la variante específica de la operación del campo op, y a veces se le denomina código de función 106 Instrucciones aritméticas y lógicas: (1) 3 operandos en registros: Ejemplos: 107 Cuidado, son números en decimal Modo de direccionamiento registro: 108 (2) 2 operandos en registros: Desplaza rt (fuente), ‘shamt’ posiciones, y pon el resultado en rd (destino) Por ejemplo: sll $7, $3, 5 0 0 3 7 6 0 109 2. Tipo I 2.1. Instrucciones de transferencia (de datos entre memoria y registros) 110 Existen instrucciones de carga distintas para los diferentes tamaños de objeto: 111 En todos los casos, el direccionamiento para el segundo operando es base (registro rt) + desplazamiento (valor especificado en la propia instrucción con 16 bits): El uso de etiquetas en ensamblador evita al programador hacer el cálculo con direcciones: lb $2, dirección (dirección = valor($1) = $1 + valor) 112 2.2. Instrucciones de salto condicional (bifurcación) La instrucción “beq rs, rt, L1”(branch if equal) significa ir a la sentencia etiquetada con L1 si el valor del registro rs es igual al valor del registro rt La instrucción “bne rs, rt, L1”(branch if not equal) significa ir a la sentencia etiquetada con L1 si el valor de rs no es igual al valor en rt 113 El modo de direccionamiento empleado es direccionamiento con desplazamiento relativo al contador de programa Se especifica el desplazamiento (16 bits) con respecto al contador de programa donde está la instrucción destino del salto Æ las instrucciones de bifurcación pueden saltar 215-1 instrucciones hacia delante y 215 hacia atrás En ensamblador, el uso de etiquetas libera al programador del tedioso cálculo de las direcciones de salto: beq $19, $20, L1 donde L1= PC + 0x183d 114 2.3. Instrucciones con un operando inmediato Para operaciones con constantes: Direccionamiento inmediato 115 3. Tipo J 3.1. Instrucciones de salto (incondicional) Direccionamiento pseudodirecto: donde la dirección de salto son los 26 bits de la instrucción concatenados con los bits de mayor peso del contador de programa: 116 Ejemplos de modos de direccionamiento de la MIPS 117 (1) Inmediato Instrucción ensamblador: addi $t0,$t1,4 (operando inmediato) Tipo I Instrucción máquina: 001000010010100000000000000000100 4 Operación a realizar: $t0 = $t1 + 4 Contenido de los registros antes de la operación: Contenido de los registros después de la operación: 118 (2) Registro: Instrucción ensamblador: sub Tipo R Instrucción máquina: $10, $11, $12 (los 3 operandos direccionados en modo registro) 00000001011011000101000000100010 $11 $12 $10 Operación a realizar: $10 = $11 - $12 = 7 – 4 = 3 Contenido de los registros después de la operación: 119 (3) Base (+desplazamiento) Instrucción ensamblador: sw $13, 8($14) (dir.base+desplaz.) Instrucción máquina: 10101101110011010000000000001000 $14 8 Operación: transfiere la palabra en el registro $13 a la posición de memoria especificada (8 + $14) 120 Contenido de los registros antes de la operación: De forma que la operación a realizar es: M ($14 + 8) = M (0x10010008) = $13 = 0x1234567 El valor queda almacenado en la correspondiente posición de memoria: 121 (4) Relativo al contador de programa Este modo de direccionamiento, especifica un salto relativo (número de instrucciones) a la instrucción de bifurcación Instrucción ensamblador: bgez $t2, instr1 (dir. relativo al PC) add $t7, $t0,$t1 instr1: add $t7, $t1, $t2 122 Instrucción máquina: 00000101010000010000000000000010 2 Operación: bifurca a la instrucción especificada por la etiqueta instr1 si el registro $t2 es mayor o igual que 0 Sea [0x0040002C] la dirección de la instrucción de bifurcación (bgez $t2, instr1) Æ instr1 = 0x0040002C + (2*4)= 0x00400034, que es la dirección de la instrucción destino del salto (add $t7,$t1,$t2) 123 (5) Pseudodirecto La dirección se calcula concatenando los 4 bits más significativos del PC con la dirección de 26 bits especificada en la instrucción y dos ceros Instrucción ensamblador: instr2: j instr2 (dir. pseudodirecto) add $t7, $t0,$t1 add $t7, $t1, $t2 Operación : salta a la instrucción especificada por instr2 124 Instrucción máquina: 00001000000100000000000000010000 Sea [0x00400038] la dirección de la instrucción de salto (j instr2) instr2 = 00000000010000000000000001000000 = 0x00400040, que es la dirección de la instrucción destino del salto (add $t7,$t1,$t2) 125