TEMA 2 Arquitectura de los sistemas basados en dispositivos

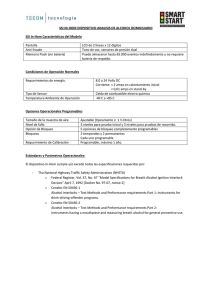

Anuncio