Práctico 3

Anuncio

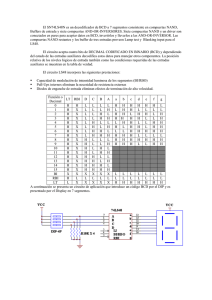

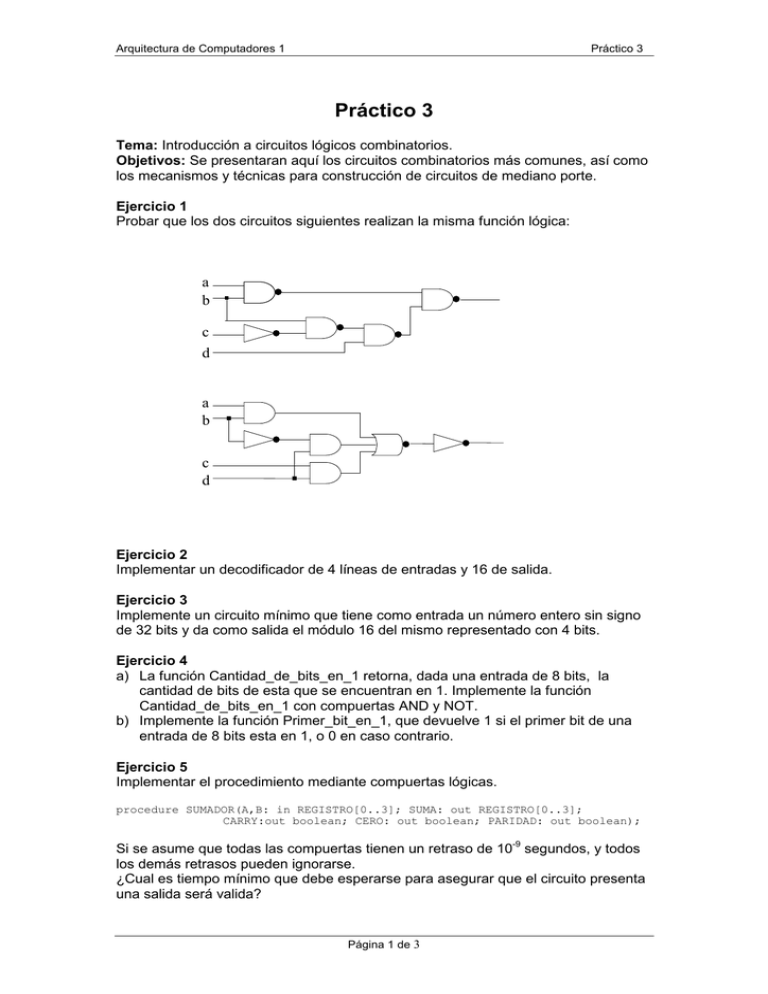

Arquitectura de Computadores 1 Práctico 3 Práctico 3 Tema: Introducción a circuitos lógicos combinatorios. Objetivos: Se presentaran aquí los circuitos combinatorios más comunes, así como los mecanismos y técnicas para construcción de circuitos de mediano porte. Ejercicio 1 Probar que los dos circuitos siguientes realizan la misma función lógica: a b c d a b c d Ejercicio 2 Implementar un decodificador de 4 líneas de entradas y 16 de salida. Ejercicio 3 Implemente un circuito mínimo que tiene como entrada un número entero sin signo de 32 bits y da como salida el módulo 16 del mismo representado con 4 bits. Ejercicio 4 a) La función Cantidad_de_bits_en_1 retorna, dada una entrada de 8 bits, la cantidad de bits de esta que se encuentran en 1. Implemente la función Cantidad_de_bits_en_1 con compuertas AND y NOT. b) Implemente la función Primer_bit_en_1, que devuelve 1 si el primer bit de una entrada de 8 bits esta en 1, o 0 en caso contrario. Ejercicio 5 Implementar el procedimiento mediante compuertas lógicas. procedure SUMADOR(A,B: in REGISTRO[0..3]; SUMA: out REGISTRO[0..3]; CARRY:out boolean; CERO: out boolean; PARIDAD: out boolean); Si se asume que todas las compuertas tienen un retraso de 10-9 segundos, y todos los demás retrasos pueden ignorarse. ¿Cual es tiempo mínimo que debe esperarse para asegurar que el circuito presenta una salida será valida? Página 1 de 3 Arquitectura de Computadores 1 Práctico 3 Ejercicio 6 (a) Construir una compuerta AND utilizando compuertas NAND. (b) Construir una compuerta OR con compuertas NAND. Ejercicio 7 Una función Mayoria es un circuito digital cuya salida es 1 si y solamente si la mayoría de las entradas son 1. La salida es 0 en cualquier otra condición. (a) Obtenga la tabla de verdad para la función Mayoría de 3 entradas. (b) Muestre que el circuito de una función Mayoría puede obtenerse con 4 compuertas NAND. (c) Muestre que el circuito sumador completo consta de un XOR de 3 entradas y una función Mayoría de 3 entradas. Ejercicio 8 Se desea implementar un display de 7 segmentos. Para entradas en el rango 0..9 se debe desplegar el número correspondiente, y E en otro caso. La salida son 7 valores que corresponden a cada uno de los segmentos. Cuando se pone un 1 en la entrada correspondiente a un determinado segmento, el mismo se enciende. Construir el bloque decodificador 7 segmentos utilizando un decodificador y compuertas OR. x y z w a b c d e f g Decodificador 7 segmentos a c f d bb g Display e Ejercicio 9 Se dispone de multiplexores de 4 a 1 (con 2 entradas de control) y compuertas NAND. a) Diseñar un registro de corrimiento a la izquierda (Shift Left) de 4 bits únicamente con multiplexores 4 a 1. b) A partir del diseño de la parte a) armar un Shift Left de 8 bits (debe tener 3 entradas de control) con las compuertas disponibles. Ejercicio 10 Multiplexores como compuertas universales: a) Probar que un multiplexor de 2 entradas de control es universal mostrando como construir las funciones AND, OR y NOT utilizando un multiplexor. b) Idem para un multiplexor de 1 entradas de control. Ejercicio 11 Asumir que X consiste de 3 bits, x2 x1 x0. Escribir cuatro funciones lógicas que son verdaderas solamente en los casos: • X contiene un sólo 1 • X contiene un número impar de 1s • X cuando se interpreta como entero binario sin signo es menor que 3 Página 2 de 3 Arquitectura de Computadores 1 Práctico 3 • X cuando se interpreta como número con signo (complemento a 2) es menor que -1. Ejercicio 12 a) Implemente un sumador completo de 4 bits. b) ¿ Qué modificaciones deben realizarse para que el circuito reste números representados en complemento a dos de 4 bits ? Ejercicio 13 a) Construir un semisumador de 1 bit únicamente con puertas NAND b) Construir un semisumador de 1 bit únicamente con puertas NOR c) Construir un sumador de 8 bits en función de la parte a) para enteros representados en complemento a 2. Setear las banderas de CARRY, ZERO y SIGNO. Ejercicio 14 a) Dado el circuito de la figura indique de qué tipo es y que función aritmética realiza. Proponga una implementación de hardware que minimice el uso de compuertas para el mismo circuito. b) Generalice el circuito propuesto para un operando de cuatro bits y otro de tres bits, sabiendo que de dispone de sumadores de cuatro bits y compuertas AND de dos entradas. a0 a1 b1 b0 AND AND b1 b0 AND AND SEMISUMADOR C S c3 SEMISUMADOR C S c2 c1 c0 Ejercicio 15 Construir un circuito que compare dos números enteros sin signo de 4 bits. Se dispone solamente de compuertas lógicas (and, or, not, xor). Las entradas al circuito son a3 a2 a1 a0 b3 b2 b1 b0, donde a3 es el bit más significativo del numero A y b3 el mas significativo de B. Las salidas del circuito son: A > B (es 1 si el número A es mayor que el número B) A = B (es 1 si el número A es igual que el número B) A < B (es 1 si el número A es menor que el número B) Nota: se sugiere diseñar primero un comparador de números de 2 bits. Página 3 de 3