Arquitectura de la memoria ROM (Read Only Memory)

Anuncio

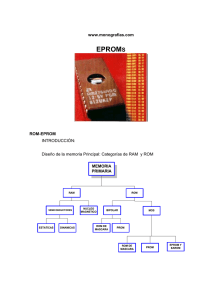

INSTITUTO POLITÉCNICO NACIONAL CENTRO DE ESTUDIOS CIENTÍFICOS Y TECNOLÓGICOS ELECTRÓNICA DIGITAL ARQUITECTURA DE LA MEMORIA (ROM) La arquitectura (estructura) interna de un CI−ROM es muy compleja y no necesitamos conocer todos sus detalles. Sin embargo es constructivo observar un diagrama simplificado de la estructura interna. Existen cuatro partes básicas: decodificador de renglones, arreglo de registros y buffer de salida. • Arreglo de registros. El arreglo de registros almacena los datos que han sido programados en la ROM. Cada registro contiene un numero de celdas de memoria que es igual al tamaño de la palabra. En este caso, cada registro almacena una palabra de 8 bits. Los registros se disponen en un arreglo de matriz< cuadrada que es común a muchos circuitos de semiconductor. Podemos especificar la posición de cada registro como una ubicada en un reglon y una columna específicos. Las 8 salidas de datos de cada registro se conectan a un canal de datos interno que corre atreves de todo el circuito. Cada registro tiene dos entradas de habilitación (E); ambas tienen que ser altas a fin de que los datos del registro sean colocados en el canal. • Decodificadores de direcciones. El código de dirección aplicado A3, A2, A1, A0, determina que registro será habilitado para colocar su palabra de datos en 8 bits en el canal. Los bits de dirección A1, A0, se alimentan de un decodificador uno de 4 que activa una línea de selección de renglón, y los bits de dirección A3, A2, se alimentan de un segundo decodificador uno de cuatro que activa una línea de selección de columna. Solamente un registro estará en el renglón y la columna seleccionados por las entradas de difracción, y estará habilitado. • Buffer de salida. El registro habilitado por las entradas de selección coloca el dato que tiene sobre el canal de datos. Estos datos entraran en los buffers de salida mismos que se encargan de trasmitirlos hacia las salidas externas siempre y cuando CS este en bajo. Si CS esta en alto, los buffers de salida se encuentran en el estado de alta impedancia, con lo que D7 asta D0 estarán flotando0 ARQUITECTURA DE LA MEMORIA (RAM) Como sucede con la ROM, es útil pensar que la RAM consta de varios registros, cada uno de los cuales almacena una sola palabra de datos y tiene una dirección única. Las RAMS comúnmente vienen con capacidades de palabras de 1K, 4K, 8K, 16K, 64K, 128K, 256K, y 1024K, y tamaños de palabras de 1, 4, u 8 1 bits. Como veremos mas adelante , la capacidad de las palabras y el tamaño de estas puede extenderse combinando circuios integrados de memoria. • Operación de lectura. El código de dirección selecciona un registro del circuito de memoria para leer o escribir. A fin de leer el contenido de registro seleccionado, la entrada lectura/escritura (R/−W)* debe ser un 1. además, la entrada (CS) selección de CI debe ser activada (un 0 de este caso). La combinación de R/−W es igual a 1 y CS es igual a 0 habilita los buffers de salida de manera que el contenido de registro seleccionado aparecerá en las cuatro salidas de datos. R/−W igual a 1 también deshabilita los buffers de entrada de manera que las entradas de datos no afecten la memoria durante la operación de lectura. • Operación de escritura. Para escribir una nueva palabra de cuatro bits en el registro seleccionado se requiere que R/−W igual a 0 y CS igual 0. esta combinación habilita los buffers de entrada de manera que la palabra de cuatro bits aplicada a las entradas de datos se cargara en el registro seccionado. R/−W igual a 0 también deshabilita los buffers de salida que son de tres estados, de manera que las salidas de datos se encuentran en el estado de alta−z, durante una operación de escritura. La operación de escritura, desde luego, destruye la palabra que antes estaba almacenada en la dirección. • Selección de CI. Muchos circuitos de memoria tienen una o mas entradas CS que se usan para habilitar o deshabilitar el circuito en su totalidad. En el modo deshabilitado todas las salidas y entradas de datos se deshabilitas (alta−z) de manera que no puede tener lugar no la operación de lectura ni de escritura. En este modo en contenido de la memoria no se afecta. La razón para tener entradas CS será mas clara cuando se combinen CI de memoria para tener mayores memorias. Observe que muchos fabricantes llaman a estas entradas CE (habilitación de circuito). Cuando las entradas CS o CE se encuentran en un estado activo, se dice que el CI de memoria a sido seleccionado; de otro modo se dice que no esta seleccionado. Muchos CI de memoria están diseñados para consumir una potencia mucho menor cuando están seleccionados. En sistemas de memoria grandes, para una operación dada de memoria, serán seleccionados una o mas CI de memoria mientras que los demás no. • Terminales comunes de entrada/ salida. A fin de conservar terminales en un encapsulado de CI, los fabricantes a menudo combinan los funciones de entradas y salida de datos utilizando terminales comunes de entrada/salida. La entrada R/−W controla la función de estas terminales E/S. Durante una operación de lectura, las terminales de entrada y salida actúan como salida de datos que reproducen el contenido de la localidad de dirección seleccionada. Durante una operación de escritura, las terminales de S/E actúan como entrada de datos. A las cuales se aplican los datos al ser escritos. ARQUITECTURA DE LA MEMORIA (EPROM) • ROM programable y borrable. Una EPROM puede ser programada por el usuario y también puede borrarse y reprogramarse tantas veces como desee. Una ves programada, la EPROM es una memoria no volátil que contendrá sus datos almacenados indefinidamente. El proceso para programar una EPROM implica la aplicación de niveles de voltaje especiales (comúnmente en un orden de 10 a 25 volts) a las entradas adecuadas del circuito en una cantidad de 2 tiempo especificada (por lo general 50 minutos) por la localidad de dirección. El proceso de programación generalmente es efectuado por un circuito especial de programación que esta separando del circuito en el cual la EPROM eventualmente trabajara. El proceso de programación completo puede llevar barios minutos para un microcircuito EPROM. En una EPROM las celdas de almacenamiento son transistores MOSFET que tienen una compuerta de cilicio sin ninguna conexión eléctrica (es decir, una compuerta flotante). En un estado normal, cada transistor esta apagado y cada celda guarda un 1 lógico un transistor puede encenderse mediante la aplicación de un curso de programación de alto voltaje, el cual inyecta electrones de alta energía en la región formada por la compuerta flotante. Estos electrones permanecen en esta región una ves que a finalizado el pulso ya que no existe ninguna trayectoria de descarga. Una ves que sea programado una celda de la EPROM se puede borrar su contenida exponiendo la EPROM a la luz ultravioleta (UV), la cual se aplica a través de la ventana que se encuerta sobre el encapsulado del circuito. La luz (UV) produce una foto corriente que va desde la compuerta flotante hacia el sustrato de cilicio; con esto se apaga el transistor y se lleva de nuevo la celda hacia el estado uno lógico. Este proceso de borrado requiere entre 15 a 20 minutos de exposición a los rayos (UV). Desafortunadamente, no existe ninguna forma de borrar solo algunas celdas; la luz (UV) borra todas las celdas al mismo tiempo por lo que una EPROM barrada almacena solamente unos lógicos. Una ves borrada puede volverse a programar. 3