temporizadores y contadores

Anuncio

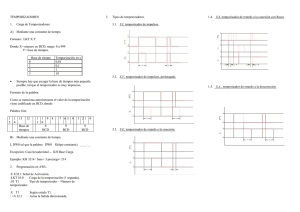

Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Los µC51 tienen dos temporizadores/contadores, TIMER0 y TIMER1 de 16 bits cada uno. Cuando operan como temporizadores, los registros SFR’s THx y TLx son incrementados cada ciclo de máquina, desde 0000H hasta FFFFH, por tanto, estos registros cuentan ciclos de máquina. Un temporizador es un arreglo en cascada de Flip Flop los cuales dividen la frecuencia de reloj en un factor de 2. El valor binario de esta cuenta es igual al número de pulsos de reloj ó eventos desde que el temporizador fue iniciado. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES El estado de cambio del último Flip Flop es llamado “condición de sobreflujo” y se activa cuando la cuenta pasa de valor FFFFH a 0000H. Para un temporizador de 16 bits se tienen: 216 = 65,535 estados ó pulsos de reloj antes de ocurrir un sobreflujo. Los temporizadores pueden programarse en varios modos de operación: Modo 0: 13 bits Modo 1: 16 bits Modo 2: 8 bits autorrecargables Modo 3: 8 bits compartidos (split) Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Registro SFR TCON (Control Timer) Este registro se utilíza para controlar el funcionamiento de los temporizadores (bits TCON.4 hasta TCON.7). TF1 (TCON.7). Bandera de sobre flujo del temporizador 1. TR1 (TCON.6). Bit de control de inicio del temporizador 1. TF0 (TCON.5). Bandera de sobre flujo del temporizador 0. TR0 (TCON.4). Bit de control de inicio del temporizador 0. * Los Bits TCON.0 a TCON.3 se definiran en las interrupciones. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Registro SFR TMOD (Modo Timer) Este registro contiene dos grupos de cuatro bits cada uno que se activan para operar el modo de trabajo del temporizador-contador. Este registro no es direccionable por bit. GATE. Bit de compuerta. Cuando esta activado, el temporizador sólo inicia cuando INTx (P3.2 ó P3.3) esta en alto (control por hardware). Cuando GATE=0 el temporizador sólo inicia cuando TRx (TCON.4 ó TCON.6) esta activado (control por software). Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Registro SFR TMOD (Modo Timer) Este registro contiene dos grupos de cuatro bits cada uno que se activan para operar el modo de trabajo del temporizador-contador. Este registro no es direccionable por bit. C/T’. Bit selector de función de operación. C/T’ = 0, temporizador (ciclos de máquina). C/T’ = 1, contador de eventos externos en T0 ó T1 (pines P3.4, P3.5). Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Registro SFR TMOD (Modo Timer) Este registro contiene dos grupos de cuatro bits cada uno que se activan para operar el modo de trabajo del temporizador-contador. Este registro no es direccionable por bit. M0, M1. Bits selector de modo de operación. Determinan el modo de operación del temporizador - contador. M1 M0 Modo Función 0 0 0 13 bits 0 1 1 16 bits 1 0 2 8 bits auto recargables 1 1 3 8 bits (compartido) Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Operación de los Temporizadores Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Temporizador en Modo 0 En este modo el temporizador sólo tiene 213 estados (8192). El byte alto del temporizador (THx) contiene los 8 bits más significativos de la cuenta y el registro TLx contiene los 5 bits menos significativos de la cuenta. TLx Æ 0000 0000b hasta 0001 1111b (00H) (1FH) Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Temporizador en Modo 1 En este modo el temporizador opera con 16 bits, es decir, tiene 216 estados (65,535). El byte alto del temporizador (THx) contiene los 8 bits más significativos de la cuenta y el registro TLx contiene los 8 bits menos significativos de la cuenta. La bandera de sobre flujo es activada durante la transición de FFFFH a 0000H. Los registros THx y TLx pueden ser cargados o leidos por software en cualquier momento, así como la bandera de sobre flujo TFx. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Temporizador en Modo 2 En este modo el registro TLx trabaja como un temporizador individual mientras que el registro THx retiene el valor de la cuenta de recarga. Cuando se activa la bandera de sobre flujo (FFH a 00H en TLx), el valor que contiene THx es cargado automáticamente en TLx continuando la cuenta. Este modo es usado para generar la velocidad de comunicación serial a través del TIMER1. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES Temporizador en Modo 3 En este modo el TIMER1 es desactivado y los registros TL0 y TH0 actúan como dos temporizadores separados de 8 bits con banderas de sobre flujo TF0 y TF1 respectivamente. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Recursos Internos del µC51. TEMPORIZADORES Y CONTADORES CONTADORES Si el bit correspondiente de los temporizadores, C/T’ = 1, el temporizador será configurado como contador de eventos externos al microcontrolador, es decir, el reloj de cuenta es un reloj externo. En este modo los registros THx y TLx son incrementados cada vez que ocurre una transición negativa (de 1 a 0) en las terminales T0 ó T1 (P3.4 y P3.5). Esta operación se ejecuta en 2 ciclos de máquina, por tanto, la máxima frecuencia será de: 500 KHz, para un cristal de 12 MHz. Ing. Ricardo Godínez Bravo.