Pauta certamen 2 del primer semestre del 2006 - csrg

Anuncio

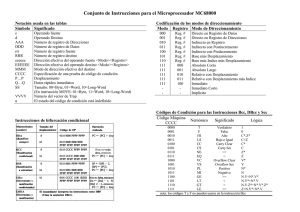

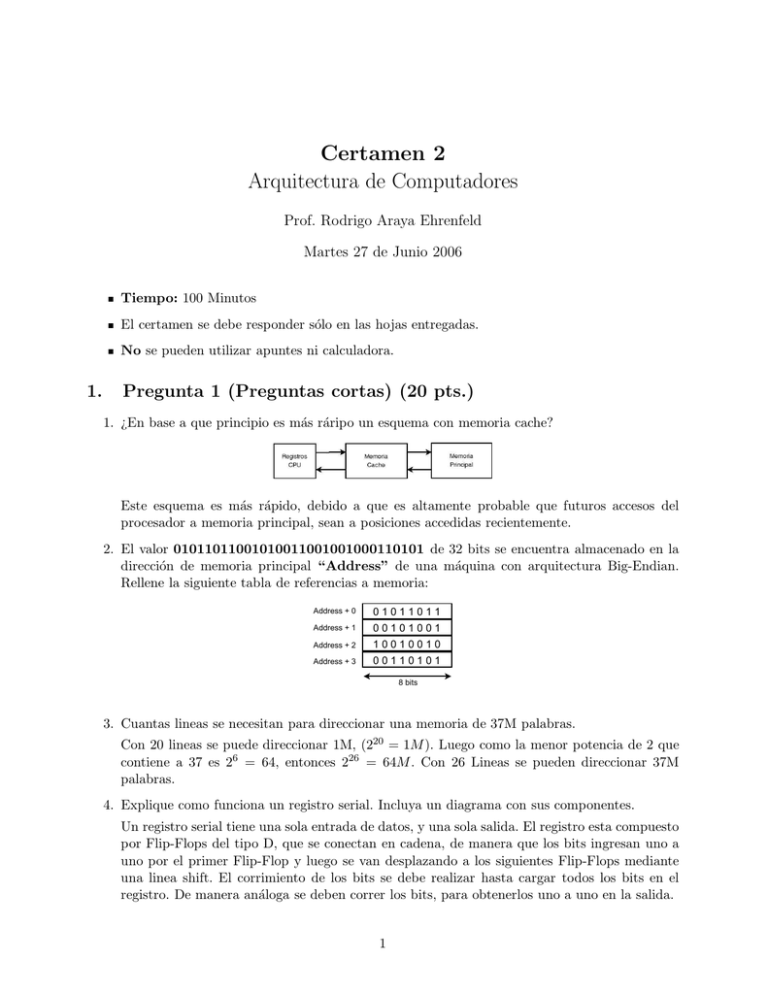

Certamen 2 Arquitectura de Computadores Prof. Rodrigo Araya Ehrenfeld Martes 27 de Junio 2006 Tiempo: 100 Minutos El certamen se debe responder sólo en las hojas entregadas. No se pueden utilizar apuntes ni calculadora. 1. Pregunta 1 (Preguntas cortas) (20 pts.) 1. ¿En base a que principio es más ráripo un esquema con memoria cache? Este esquema es más rápido, debido a que es altamente probable que futuros accesos del procesador a memoria principal, sean a posiciones accedidas recientemente. 2. El valor 01011011001010011001001000110101 de 32 bits se encuentra almacenado en la dirección de memoria principal “Address” de una máquina con arquitectura Big-Endian. Rellene la siguiente tabla de referencias a memoria: Address + 0 01011011 Address + 1 00101001 Address + 2 10010010 Address + 3 00110101 8 bits 3. Cuantas lineas se necesitan para direccionar una memoria de 37M palabras. Con 20 lineas se puede direccionar 1M, (220 = 1M ). Luego como la menor potencia de 2 que contiene a 37 es 26 = 64, entonces 226 = 64M . Con 26 Lineas se pueden direccionar 37M palabras. 4. Explique como funciona un registro serial. Incluya un diagrama con sus componentes. Un registro serial tiene una sola entrada de datos, y una sola salida. El registro esta compuesto por Flip-Flops del tipo D, que se conectan en cadena, de manera que los bits ingresan uno a uno por el primer Flip-Flop y luego se van desplazando a los siguientes Flip-Flops mediante una linea shift. El corrimiento de los bits se debe realizar hasta cargar todos los bits en el registro. De manera análoga se deben correr los bits, para obtenerlos uno a uno en la salida. 1 2. Pregunta 2 (35 pts.) Considere la siguiente pseudo-instrucción: rot reg 1, reg 2, n Esta instrucción realiza una “rotación” de los bits, considerando ambos registros como si fueran uno solo. Es decir, cuando se ejecuta la instrucción, los n bits menos significativos de reg 2 (ver diagrama) quedaran en los n bits más significativos de reg 1. Y los n bits menos significativos de reg 1 quedaran en los n bits más significativos de reg 2. La idea es que no se pierde ningun bit! Ej: Si reg 1 contiene: 111...111 y reg 2 contiene: 000...000 , al ejecutar “rot reg 1, reg 2, 2”, el contenido de reg 1 será: 0011...111 y el contenido de reg 2 será: 1100...000 Escriba en assembly MIPS el código que genera el compilador cuando se encuentra con esta instrucción. Puede utilizar las instrucciones sllv y srlv, que operan de igual forma que sll y srl, a diferencia que el tercer argumento no es un valor inmediato de corrimiento, sino que un registro, el cual contiene el valor de corrimiento. Considere que la instrucción rot será correctamente utilizada, por lo que No hay que preocuparse por los rangos de bits que esten fuera del registo. addi addi sub sllv srlv sllv srlv or or $t3, $0, n $t4, $0, 32 $t4, $t4, $t3 $t0, reg 1, $t4 reg 1, reg 1, $t3 $t1, reg 2, $t4 reg 2, reg 2, $t3 reg 2, reg 2, $t0 reg 1, reg 1, $t1 # # # # # # # # # t3=n t4=32 t4=32-n $t0 = reg 1 reg 1 = reg $t1 = reg 2 reg 2 = reg reg 2 = reg reg 1 = reg 2 << 32-n 1 >> n << 32-n 2 >> n 2 || $t0 1 || $t1 3. Pregunta 3 3.1. Camino de datos (15 pts.) Considere la nueva instrucción jm (jump memory) jm offset($rs) Esta instrucción busca en memoria principal la palabra que se encuentra en la dirección efectiva ($rs + offset) y luego la deja en PC. Corresponde a una instrucción Tipo I, en la que no se utiliza el campo rt. Modifique el Camino de datos adjunto, agregando lineas de control y de datos si fuera necesario. Justifique los cambios y explique como funciona el control de la nueva instrucción. Basta con agregar una linea de datos, desde la salida de la memoria principal, hasta la entrada del multiplexor jump, por lo que se debe agregar una entrada a este multiplexor (ver figura). Con esta modificación la linea de control jump queda de 2 bits. 3.2. Complete la tabla (10 pts.) Utilice el camino de datos modificado, para completar la siguiente tabla con los valores para las lineas de control (si alguno de los valores es superfluo, marquelo con “X”): Instruc- Reg Jump Branch Mem Mem Mem ALU Reg Operacion ción Dst Read toReg Write Src Write ALU lw 0 00 0 1 1 0 1 1 suma jm x 10 x 1 x 0 1 0 suma j x 01 x 0 x 0 x 0 x 3 4. Pregunta 4 , Multiciclo 4.1. ¿Que se realiza en cada paso de la ejecución de instrucciones? (20 pts.) Paso 1: IR=Memoria[PC] PC=PC+4 Paso 2: A=REG[IR[25-21]] B=REG[IR[20-16]] ALUOut=PC + (ext(IR[15-0]) << 2) Paso 3: ALUOut= A op B ALUOut = A + ext(IR[15-0]) Paso 4: REG[IR[15-11]]= ALUOut Si (A==B) PC=ALUOut MDR = MEMORY[ALUOut] PC= (PC[31-28] || (IR[25-0] << 2)) MEMORY[ALUOut] = B Paso 5: REG[IR[20-16]]=MDR 4.2. Marque con una “X” los pasos necesarios para cada tipo de instrucción. (5 pts.) Tipo de instrucción tipo R lw sw j beq 4.3. Paso 1 X X X X X Paso 2 X X X X X Paso 3 X X X X X Paso 4 X X X Paso 5 X Total 4 5 4 3 3 Estime la cantidad media de ciclos por instrucción de una máquina multiciclo. (5 pts.) Para ello considere que en promedio en un código hay: 25 % cargas, 15 % almacenamientos, 40 % operaciones tipo R, 15 % saltos, 5 % saltos condicionales. 5∗ 25 100 +4∗ 15 100 +4∗ 40 100 +3∗ 15 100 +3∗ 5 100 = 4, 05 ciclos por instrucción. RAE/LATEX 4