Historia de los Microprocesadores

Anuncio

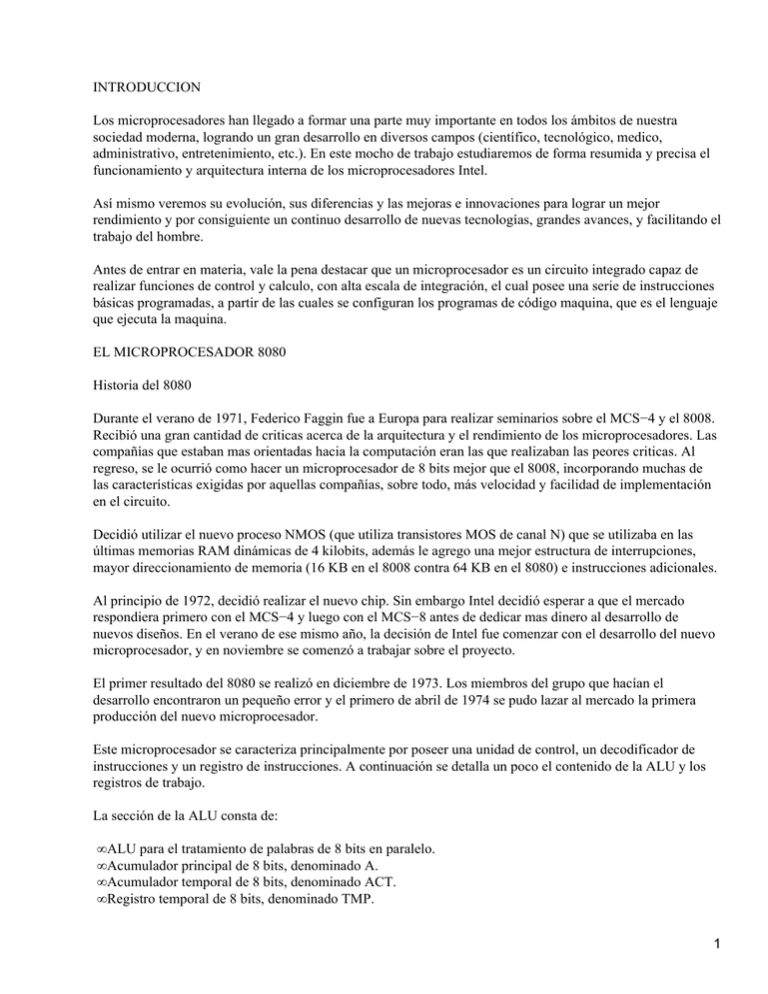

INTRODUCCION Los microprocesadores han llegado a formar una parte muy importante en todos los ámbitos de nuestra sociedad moderna, logrando un gran desarrollo en diversos campos (científico, tecnológico, medico, administrativo, entretenimiento, etc.). En este mocho de trabajo estudiaremos de forma resumida y precisa el funcionamiento y arquitectura interna de los microprocesadores Intel. Así mismo veremos su evolución, sus diferencias y las mejoras e innovaciones para lograr un mejor rendimiento y por consiguiente un continuo desarrollo de nuevas tecnologías, grandes avances, y facilitando el trabajo del hombre. Antes de entrar en materia, vale la pena destacar que un microprocesador es un circuito integrado capaz de realizar funciones de control y calculo, con alta escala de integración, el cual posee una serie de instrucciones básicas programadas, a partir de las cuales se configuran los programas de código maquina, que es el lenguaje que ejecuta la maquina. EL MICROPROCESADOR 8080 Historia del 8080 Durante el verano de 1971, Federico Faggin fue a Europa para realizar seminarios sobre el MCS−4 y el 8008. Recibió una gran cantidad de criticas acerca de la arquitectura y el rendimiento de los microprocesadores. Las compañías que estaban mas orientadas hacia la computación eran las que realizaban las peores criticas. Al regreso, se le ocurrió como hacer un microprocesador de 8 bits mejor que el 8008, incorporando muchas de las características exigidas por aquellas compañías, sobre todo, más velocidad y facilidad de implementación en el circuito. Decidió utilizar el nuevo proceso NMOS (que utiliza transistores MOS de canal N) que se utilizaba en las últimas memorias RAM dinámicas de 4 kilobits, además le agrego una mejor estructura de interrupciones, mayor direccionamiento de memoria (16 KB en el 8008 contra 64 KB en el 8080) e instrucciones adicionales. Al principio de 1972, decidió realizar el nuevo chip. Sin embargo Intel decidió esperar a que el mercado respondiera primero con el MCS−4 y luego con el MCS−8 antes de dedicar mas dinero al desarrollo de nuevos diseños. En el verano de ese mismo año, la decisión de Intel fue comenzar con el desarrollo del nuevo microprocesador, y en noviembre se comenzó a trabajar sobre el proyecto. El primer resultado del 8080 se realizó en diciembre de 1973. Los miembros del grupo que hacían el desarrollo encontraron un pequeño error y el primero de abril de 1974 se pudo lazar al mercado la primera producción del nuevo microprocesador. Este microprocesador se caracteriza principalmente por poseer una unidad de control, un decodificador de instrucciones y un registro de instrucciones. A continuación se detalla un poco el contenido de la ALU y los registros de trabajo. La sección de la ALU consta de: • ALU para el tratamiento de palabras de 8 bits en paralelo. • Acumulador principal de 8 bits, denominado A. • Acumulador temporal de 8 bits, denominado ACT. • Registro temporal de 8 bits, denominado TMP. 1 5. 5 registros de 1 bit, que configuran el denominado registro de estado y actúan como indicadores de: signo, acarreo, paridad, acarreo intermedio y cero. A través del acumulador temporal y el registro temporal se introducen los datos que serán tratados por la ALU; los resultados de dicho tratamiento, normalmente, son depositados en el acumulador o pasan directamente al bus interno de la CPU. En la sección de registros se encuentra el contador de programas (PC), el cual sirve para direccionar la posición de la memoria de instrucciones, donde se encuentra el programa; consiste en un registro de 16 bits, capaz de direccionar 2 posiciones de memoria, equivalentes a 65536 palabras de 8 bits (64 K). En esta sección también se encuentra el stack que es un registro de 16 bits, empleado para direccionar cualquier zona de memoria LIFO (último en entrar, primero en salir). Su principal misión es salvar el contenido de los registros principales de la CPU, cuando se rompe la secuencia de un programa y, posteriormente, hay que regresar al estado en que había quedado el microprocesador, cuando se produjo el salto. Además del PC y el stack, existen otros 4 registros más, también de 16 bits, divididos en 6 porciones de 8 bits cada uno. La organización de los registros B, C, D, E, H y L, está diseñada para su actuación en parejas, mientras que W y Z actúan como registros temporales. Los registros B, C, D, E, H y L, básicamente se utilizan como elementos de apoyo en el direccionamiento de la memoria. Si trabajan como contenidos individuales, transfieren su contenido de 8 bits al bus interno; mientras que si actúan en parejas, los 16 bits pasan de forma directa hasta el buffer de dirección y luego al bus que controla. Todos los registros tienen como característica común la de poder ser incrementados o decrementados fácilmente. Modos de direccionamiento del 8080 El microprocesador 8080 puede ser direccionado de 4 modos diferentes: • Inmediato: el byte, que sigue al código de la instrucción, expresa el operando que maneja la instrucción. • Directo: los 2 bytes, que siguen al código de la instrucción, proporcionan la dirección de la memoria donde se encuentra almacenado él operando. • Por registro: la instrucción determina cual de los registros, tanto individual como en parejas, contiene el dato u operando. • Por par de registros indirectos: la instrucción determina la pareja de registros: b−c, d−e, o h−l, que contiene la dirección de la memoria en donde se encuentra el operando, se suele usar los registros h−l (que contienen los 8 bit de mas peso y de menos peso respectivamente) para direccionar la memoria. CONJUNTO DE INSTRUCCIONES DEL 8080 MOV R1, R2 MOV M, R MOV R, M HLT MVI R MVI m INR R DCR R INR M DCR M Mover registro a registro Mover registro a memoria Mover memoria a registro Alto Mover registro inmediato Mover memoria inmediata Incrementar registro Decrementar registro Incrementar memoria Decrementar memoria 2 ADD R ADC R SUB R SBB R ANA R XRA R ORA R CMP R ADD M ADC M SUB M ANA M XRA M ORA M CMP M ADI ACI SUI SBI ANI XRI ORI CPI RLC RRC RAL RAR JMP JC JNC JZ JNZ JP JM JPE JPO CALL CC CNC CZ CNZ CP CM Sumar registro A Sumar registro a A con arrastre Restar registro de A Restar registro de A con rebose AND registro con A EXCLUSIVE−OR registro con A OR registro con A Comparar registro con A Sumar memoria a A Sumar memoria a A Restar memoria de A AND memoria con A EXCLUSIVE−OR Memoria con A OR memoria con A Comparar memoria con A Suma inmediato a A Suma inmediato a A con arrastre Resta inmediato de A Resta inmediato de A con arrastre AND inmediato con A EXCLUSIVE−OR inmediato con A OR inmediato con A Comparar inmediato con A Desplazar cíclicamente A a la izquierda Desplazar cíclicamente A a la derecha Desplazar cíclicamente A a la izquierda con arrastre Desplazar ciclicamente A a la derecha con arrastre Bifurcación incondicional Bifurcación sobre arrastre Bifurcación sobre no arrastre Bifurcación sobre cero Bifurcación sobre no cero Bifurcación sobre positivo Bifurcación sobre negativo Bifurcación sobre paridad par Bifurcación sobre paridad impar Llamada incondicional Llamada sobre arrastre Llamada sobre no arrastre Llamada sobre cero Llamada sobre no cero Llamada sobre positivo Llamada sobre negativo 3 CPE CPO RET RC RNC RZ RNZ RP RM RPE RPO RST IN OUT LXI B LXI D LXI H LXI SP PUSH B PUSH D PUSH H PUSH PSW POP B POP D POP H POP PSW STA LDA XCHG XTHL SPHL PCHL DAD B DAD D DAD H DAD SP STAX B STAX D LDAX B LDAX D INX B INX D INX H Llamada sobre paridad par Llamada sobre paridad impar Vuelta Vuelta sobre arrastre Vuelta sobre no arrastre Vuelta sobre cero Vuelta sobre no cero Vuelta sobre positivo Vuelta sobre negativo Vuelta sobre paridad par Vuelta sobre paridad impar Reiniciar Entrada Salida Cargar inmediato el registro par B y C Cargar inmediato el registro par D y E Cargar inmediato el registro par H y L Cargar inmediato el puntero de pila Introducir en la pila el registro par B y C Introducir en la pila el registro par D y E Introducir en la pila el registro par H y L Introducir en la pila A y los banderines Sacar de la pila el registro par B y C Sacar de la pila el registro par D y E Sacar de la pila el registro par H Y L Sacar de la pila A y los banderines Almacenar directo A Cargo directo a A Cambiar los registros D y E, H y L Cambiar el extremo superior de la pila H y L al puntero de pila H y L al contador del programa Sumar B y C a H y L Sumar D y E a H y L Sumar H y L a H y L Sumar el puntero de pila a H y L Almacenar A indirecto Almacenar A indirecto Cargar A directo Cargar A directo Incrementar los registros B y C Incrementar los registros D y E Incrementar los registros H y L 4 INX SP DCX B DCX D DCX H DCX SP CMA STC CMC DAA SHLD LHLD EI DI NOP Incrementar el puntero de pilas Decrementar B y C Decrementar D y E Decrementar H y L Decrementar el punto de pila Complementar A Poner arrastre Complementar arrastre Ajustar decimal A Almacenar H y L directo Cargar H y L directo Habilitar interrupción Inhabilitar interrupción No operación, instrucción Nota: Si bien todas las instrucciones del 8008 están incluidas en el 8080, un programa grabado en ROM para el primer procesador no correrá para el segundo ya que los códigos de operación de las instrucciones son diferentes, por lo que se deberá volver a ensamblar el código fuente para que pueda funcionar en el 8080. EL MICROPROCESADOR 8085 Historia del 8085 El siguiente microprocesador creado por Intel fue el 8085 en 1977. La alimentación es única: requiere solo +5v. Esto se debe a la nueva tecnología utilizada para la fabricación llamada HMOS (High performanceN−channels MOS) que además permite una mayor integración con mas de diez mil transistores. Tiene incorporado el generador de pulsos de reloj con lo que solo hace falta un cristal de cuarzo y un par de capacitores externos (para el 8080 se necesitaba el circuito integrado auxiliar que lleva el código 8224). Además esta mejorado en cuanto a las interrupciones. Incluye las instrucciones del 8080 y posee dos adicionales (RIM y SIM) referidas a este sistema de interrupciones y a la entrada y salida serie. El bus de datos esta multiplexado con los 8 bits menos significativos del bus de direcciones, con lo que permite tener mas pines libres para el bus de control del microprocesador. El 8085 consta de tres bloques fundamentales: • Conjunto de registros, formado por el contador de programas (16 bits), el stack pointer (16) y las tres parejas de registros de 8 bits cada uno, junto con la búsqueda que incrementa o decrementa el contenido de todos los registros. • La ALU, en combinación con el acumulador y un registro temporal, así como los 5 bits que actúan como flags o señalizadores de estado. • El registro de instrucciones, combinado con el decodificador de instrucciones y el circuito de control y de tiempo. Una característica muy peculiar del 8085 la constituye el multiplexado de los 8 bits de menos peso del bus de direcciones con los 8 bits del bus de datos. Esto quiere decir que por los mismos pines que sale la información del bus de datos salen también, en otros momentos, los 8 bits de menos significación de la información del bus de direccionamiento. Esta propiedad proporciona 8 pines más para las funciones de control del sistema. Este detalle es muy importante, dada la limitación del número de pines que tienen los fabricantes. Dicha limitación impide el aumento de control de la CPU, ya que al destinar 16 pines para el bus de direcciones, 8 5 para el bus de datos, 2 para la alimentación y 2 para el control del generador del reloj interno, sólo quedan 12 pines libres para las funciones de interrupción, control, sincronización, etc. Para aumentar esta potencia, el 8080 multiplexa en el bus de datos la información de su estado interno y el 8085 multiplexa también en el bus de datos los 8 bits de menos peso del bus de direcciones. Si se está efectuando una operación de lectura, el microprocesador genera la señal READ y el elemento de memoria o de I/O seleccionado coloca en el bus de datos/direcciones. Si se trata de un ciclo de escritura, el microprocesador genera una señal WRITE y en un flanco positivo de memoria direccionada almacena el dato desde el bus. CONJUNTO DE INSTRUCCIONES DEL 8085 Además de contener las 111 instrucciones del 8080, posee 2 nuevas: SIM RIM Sirve para poner mascara de interrupción de RST 5.5, RST 6.5, RST 7.5 y para enviar un dato por la puerta serie (terminal SOD). Sirve para leer la mascara de interrupción general, y de RST 5.5, RST 6.5, RST 7.5, las instrucciones pendientes y para leer el dato de la puerta serie (terminal SID). MICROPROCESADOR 8086/8088 Historia del 8086/8088 En junio de 1978 Intel lanzó al mercado el primer microprocesador de 16 bits: el 8086. En junio de 1979 apareció el 8088 (internamente igual que el 8086 pero con bus de datos de 8 bits) y en 1980 los coprocesadores 8087 (matemático) y 8089 (de entrada y salida). El primer fabricante que desarrollo software y hardware para estos chips fue la propia Intel. Reconociendo la necesidad de dar soporte a estos circuitos integrados, la empresa invirtió una gran cantidad de dinero en un gran y moderno edificio en Santa Clara, California, dedicado al diseño, fabricación y venta de sus sistemas de desarrollo. De esta manera la empresa Intel desarrolló una serie completa de software que se ejecutaba en una microcomputadora basada en el 8085 llamada Intellec Microcomputer Development System. Arquitectura Interna del 8086/8088 Estos microprocesadores poseen dos procesadores en el mismo chip, que se denominan: Unidad de Ejecución (EU) y la Unidad de Interfaz del Bus (BIU). Cada uno de ellos dispone de sus propios registros y de su propia sección aritmético − lógica, trabajando asincrónicamente con el otro, para lograr la máxima potencia del cómputo. La unidad de interfaz del bus, BIU, es la encargada de buscar las instrucciones, guardarlas en la cola de espera para ser ejecutadas y facilitar el direccionamiento de la memoria, lo que realiza a través del bus de direcciones, que posee 20 líneas. El tratamiento de la cola, en la que se guardan los códigos de las instrucciones que esperan a ser ejecutadas por la EU, es responsabilidad de la BIU: aun cuando dos o más bytes de la cola estén vacantes, la unidad de interfaz del bus fuerza automáticamente un ciclo de búsqueda de instrucción, para que la cola se mantenga lo más llena posible. Esta cola consta de 4 registros en el 8088, mientras que en el 8086 son 6 registros. Independientemente del microprocesador, cada registro de la cola es de 8 bits, de tipo RAM y con estructura FIFO. La unidad de ejecución no tiene que esperar a la búsqueda de la instrucción y puede trabajar a su 6 máxima velocidad. La unidad de ejecución tiene la responsabilidad de ejecutar las instrucciones, siendo posible considerarla como una CPU clásica. Posee una ALU con un registro de estado con varios flags asociados y un conjunto de registros de trabajo. Los primeros 4 registros de la EU, de 16 bits que pueden usarse como 8 de 8 bits, tienen una actuación muy similar a la de los acumuladores. Por ejemplo, el AH se emplea en multiplicaciones, divisiones, entradas/salidas, etc; el BH, como el registro base para el direccionamiento de memoria; el CH, como contador de datos y el DH, como direccionador indirecto de puertas de entrada y salida. Los otros registros de la EU, también de 16 bits, conforman el grupo de registros punteros. SI y DI actúan como índices asociados al registro DS. El registro BP actúa como base de la dirección de la pila; mientras que SP es su puntero. Los registros BP y SP funcionan combinadamente con el SS. El grupo de registros de segmentos está formado por 4 de 16 bits. Los 16 bits, que implementan las 16 líneas de más peso de la dirección de 20 bits que se genera por el bus correspondiente proceden de un registro de segmento; los cuales son: CS, que hace referencia al segmento del código de instrucciones; DS, que hace referencia al segmento para datos; SS, como base del segmento de la pila y ES, como base de un segmento extra o suplementario. El registro puntero de instrucción (IP) contiene un valor de 16 bits que es un desplazamiento sobre la dirección del registro CS. CONJUNTO DE INSTRUCCIONES DEL 8086/8088 ROL ROR SAL SAR SHL SHR STC STD STI LOCK WAIT JA JAE JB JBE JCXZ JE JG JGE JL JLE JNA Rotación a la izquierda Rotación a la derecha Desplazamiento aritmético a la izquierda Desplazamiento aritmético a la derecha Desplazamiento lógico a la izquierda Desplazamiento lógico a la derecha Pone a uno el indicador de acarreo Pone a uno el indicador de dirección Pone a uno el indicador de interrupción Bloqueo de bus Espera hasta la activación de la línea Test Salto si superior Salto si superior o igual Salto si inferior Salto si inferior o igual Salto si CX (contador)=0 Salto si igual Salto si mayor que Salto si mayor o igual Salto si menor Salto si menor o igual Salto si no superior 7 JNAE JNB JNBE JNE JNGE JNL JNLE JNO JNS JNP JS LOOP LAHF POPF PUSHF SAHF AAA DAS DEC NEG AAM IMUL MUL AAD CBW CWD DIV IDIV CMPS LODS MOVS OUTS REP REPE REPNE REPNZ REPZ SCAS STOS AND OR NOT TEST Salto si no superior o igual Salto si no inferior Salto si no inferior o igual Salto si no igual Salto si no mayor o igual Salto si no menor Salto si no menor o igual Salto si no desbordamiento Salto si no signo Salto si no paridad Salto si signo Bucle Carga a AH con los indicadores Extrae los indicadores de la pila Introduce los indicadores en la pila Almacena AH en el registro de indicaciones Ajuste ASCII para la suma Ajuste decimal para la resta Decremento Negación Ajuste ASCII para la multiplicación Multiplicación entera Multiplicación sin signo Ajuste ASCII para la división Convierte byte en palabra Convierte palabra en palabra doble División sin signo División entera Compara cadenas Carga cadena Transferencia de cadena Salida de cadena Repetición Repetición mientras igual Repetición mientras no igual Repetición mientras no cero Repetición mientras cero Explora cadena Almacena cadenas Intersección lógica O lógico No lógico Comparación lógica 8 XOR O exclusivo lógico MICROPROCESADORES 80186/80188 Los Intel 80186/80188 son las versiones mejoradas del microprocesador anterior 8086/8088. Los 80186/80188 son todos los microprocesadores de 16 bits que son compatibles al 8086/8088. Aun la arquitectura de estos microprocesadores es semejante a la de versiones anteriores. Las mejoras realizadas a los procesadores 80186/80188 en comparación a las versiones anteriores fueron las siguientes: Se le agregó un generador del reloj que esta vez es interno y reemplaza al generador externo utilizado con la versión anterior, lo que reduce el numero de componentes en un sistema. Además un controlador programable de interrupciones quien sirve de arbitro a todas las interrupciones internas y externas, controla hasta dos PC externos. Ahora contiene tres temporizadores de 16 bits totalmente programables (0 y 1 controla los procesos internos y el último sirve de reloj para vigilar si se desea interrumpir al microprocesador después de cierta cantidad de tiempo). Se suman a los componentes de los antiguos microprocesadores, dos unidades programables de DMA, las cuales pueden transferir datos entre localidades de la memoria, entre la memoria y las E/S, o entre los periféricos de E/S. Y la unidad de señales de habilitación programable. En cuanto a la arquitectura son casi idénticos, entre si, y con las versiones anteriores. La única diferencia entre el 80186 y el 80188 es el ancho de sus canales para datos. El 80186 (como el 8086) contiene un canal de datos de 16 bits, mientras que el 80188 (como el 8088) contiene un canal para datos de 8 bits. La estructura de los registros es casi idéntica a la versión anterior. La única diferencia es que contienen vectores de interrupción adicionales reservados y algunas muy poderosas características de entrada y salida integradas. Los 80186/80188 son llamados a menudo controladores dedicados debido a su aplicación, que no es como una computadora basada en un microprocesador, sino como un controlador. MICROPROCESADOR 80286 Historia del 80286 El microprocesador 80286 fue liberado en febrero de 1982. Para su ensamblaje se utilizaron los componentes del 80186/80188, para así lograr la configuración con multitarea (ejecución simultánea de varios programas). El 80286 opera de dos modos diferentes: modo real y modo protegido. En el modo real, se comporta igual que un 8086, y en modo protegido, necesita un nivel de integración mucho mayor. El microprocesador contiene 134.000 transistores (mucho mas que el 8086), y ejecuta alrededor de 1,2 millones de instrucciones por segundo. El microprocesador 80286 añadió un nuevo nivel de satisfacción a la arquitectura básica del 8086, incluyendo una gestión de memoria con la extensión natural de las capacidades de direccionamiento del procesador. El 80286 contiene el juego de instrucciones del 80186, así como la extensión del espacio direccionable a 16 MB, utilizando 24 bits para direccionar (2 = 16.777.216). Este microprocesador está diseñado para usar un sistema operativo con varios niveles de privilegio. Estos sistemas operativos tienen un núcleo que es su parte más interna. El núcleo tiene el máximo privilegio y los programas de aplicaciones el mínimo. La protección de datos en este tipo de sistemas se lleva a cabo teniendo segmentos de código (que incluye las instrucciones), datos (que incluye la pila aparte de las variables de los programas) y del sistema (que indican los derechos de acceso de los otros segmentos). 9 Para un usuario normal los registros de segmentación (CS, DS, ES, SS) parecen tener los 16 bits usuales, pero en cambio estos registros no apuntan directamente a la memoria, como lo hacían en el 8086. A los 16 bits, cada registro de segmento del 80286 mantiene otros 57 bits invisibles para el usuario. 8 bits mantienen los derechos de acceso (solo lectura, solo escritura, otros), otros bits mantienen la dirección real (24 bits) del principio del segmento y otros mantienen la longitud permitida del segmento (16 bits, para tener la longitud máxima de 64 KB). La arquitectura interna que presenta este microprocesador es la siguiente: • Unidad de decodificación de instrucciones. • Unidad de ejecución • Unidad de direccionamiento • Unidad de interfaz con el bus La unidad de interfaz del bus (BIU) dirige operaciones relacionadas con el bus local (dirección de datos y control), esta busca en memoria instrucciones y les mete en la cola de espera en el momento de que no recibe la orden de la unidad de ejecución (EU) la cual puede necesitar operandos o almacenar resultados. La unidad de decodificación de instrucciones (IU), recibe los códigos desde la cola de espera, los decodifican y los almacena en la cola de microinstrucciones que alimenta la EU. La EU ejecuta instrucciones, cuando necesitan cambiar de celda de memoria, localizar un operador o almacenar un resultado se comunican con la unidad de direccionamiento (AU). La forma en que se llevan a cabo los procesos en este microprocesador, es denominada PIPELINE o proceso en tubería. Debido a que cada unidad trabaja de manera individual, es decir, no tiene que esperar a que termine la ejecución completa de una instrucción para comenzar la otra. Mientras que una instrucción se encuentra en la unidad de direccionamiento, simultáneamente se está ejecutando otra en la EU y a la vez la unidad de instrucciones se encuentra preparando la cola de tres instrucciones ya decodificadas, y la unidad del bus mantiene siempre llena su cola de 6 instrucciones. Gracias a este proceso de tubería, aumenta la velocidad de ejecución de un programa, ya que cada una de las unidades se encuentran actuando de forma simultanea, lo que contribuye a que ninguna de las unidades deba perder tiempo esperando por el trabajo de la otra. CONJUNTO DE INSTRUCCIONES DEL 80286 Además de las instrucciones de su antecesor, es decir, las del 8086/8088 más las agregadas 80186 (PUSHA, POPA, INS, OUTS, BOUND, ENTER, LEAVE, la multiplicación inmediata, así como conteo para corrimientos/rotaciones); han sido incorporadas 17 nuevas instrucciones al conjunto del 80286 (todas corresponden al modo protegido). CLTS LDGT SGDT LIDT SIDT LLDT SLDT LMSW SMSW LAR Desactiva la bandera de conmutación de tareas Carga el registro para la tabla del descriptor global Almacena el registro de la tabla de descriptores globales Carga el registro de la tabla del descriptor conmutador Almacena el registro de la tabla del descriptor conmutador Carga el registro de la tabla del descripto local Almacena el registro de la tabla del descriptor local Carga la palabra del estado de la maquina Almacena la palabra del estado de la maquina Carga los derechos de acceso 10 LSL SAR ARPL VERR VERW LTR STR Cerca el limite del segmento Almacena los derechos de acceso Ajusta el nivel de privilegio solicitado Verifica el acceso a ruta Verifica el acceso a escritura Carga el registro de tarea actual Almacena el registro de tarea actual MICROPROCESADOR 80386 Historia del 80386 En octubre de 1985 Intel lanza al mercado su primer procesador con una arquitectura de 32 bits, el 80386, el cual constituyó una gran revisión del modelo anterior. Arquitectura del 80386 El 80386 posee una unidad central de proceso (CPU), una unidad de manejo de memoria (MMU) y una unidad de interfaz con el bus (BIU). La CPU está compuesta por la unidad de ejecución y la unidad de instrucciones. La unidad de ejecución contiene los 8 registros de 32 bits de propósito general que se utilizan para el cálculo de direcciones y operaciones con datos y un barrel shifter de 64 bits que se utilizan para acelerar las operaciones de desplazamiento, rotación, multiplicación y división. La unidad de instrucción decodifica los códigos de operación (opcodes) de las instrucciones que se encuentran en una cola (cuya longitud es de 16 bytes) y los almacena decodificados (hay espacio para 3 instrucciones). El sistema de control de la unidad de ejecución es el encargado de decodificar las instrucciones que les envía la cola y enviarle las ordenes a la unidad aritmética lógica según una tabla que tiene almacenada en ROM llamada CROM (Control Read Only Memory). La unidad de manejo de memoria (MMU) consiste en una unidad de segmentación (similar a la del 80286) y una unidad de paginado (nuevo en este microprocesador). La segmentación permite el manejo del espacio de direcciones lógicas agregando un componente de direccionamiento extra, el cual permite que el código y los datos puedan reubicar fácilmente. El mecanismo de paginado opera por debajo y es transparente al proceso de segmentación, para permitir el manejo del espacio de direcciones físicas. Cada segmento se divide en una o más paginas de 4 KB. Para implementar un sistema de memoria virtual (aquel donde el programa tiene un tamaño mayor que la memoria física y debe cargarse por partes o páginas desde el disco rígido), el 80386 permite seguir ejecutando los programas después de haberse detectado fallos de segmento o de páginas. Registros del usuario • Registro de propósito general (8): conjunto de 8 registros de 32 bits, que se usa como acumuladores en operaciones lógicas y aritméticas, también como registro de almacenamiento de dirección y datos, estos registros pueden manejar información de 32 o 16 bits, se puede dividir en 4 partes con datos de 8 bits. • Registros de apuntador de instrucciones y registros de señalizadores (2): es un registro de 32 bits que guarda el desplazamiento sobre la base del segmento de código, para apuntar así la dirección de la siguiente instrucción a ejecutar. • Registros de segmentos (6): los 6 registros de segmento son de 16 bits y guarda la dirección de comienzo de segmento de código, los SS apunta al segmento de la pila y los registros DS, ES, FS y GS, almacenan las 11 direcciones iniciales de los distintos segmentos de datos en modo real. Registros del sistema: • Registros de control (4): son 4 registros de control cada uno de 32 bits, este grupo contiene el estado operativo de la maquina de forma global, cuando se emplea para todas las tareas que soporta y no refiriéndose en forma concreta. • Registros del sistema de direccionamiento (4): 4 registros encargados de referenciar las tablas que manejan las direcciones del sistema. • Registros de depuración (6): 6 registros de 32 bits que accesibles al programador y que constituyen una extraordinaria herramienta para la puesta a punto de los sistemas lógicos. • Registros de pruebas (2): 2 registros de 32 bits, que se emplean en el control y pruebe de la RAM−CAM (memoria direccionable por contenido). Bus de datos: se compone de 32 líneas llamadas D0−D31, es bidireccional y triestado, puede transferir información de 16 y 32 bits, usando elementos de control. Bus de direcciones: lo conforman 32 líneas triestado de salida. Este bus tiene la dirección física de una posición de la memoria principal de una E/S, puede direccionar unos 4000 millones de bytes (4 GB). Finalmente, el 80386 al igual que el 80286 también cuenta con una estructura de PIPELINE. Diferencia con respecto al 8086 y al 80286 • El 80386 es un CPU de 32 bits, lo que significa un considerable incremento en la capacidad de procesamiento. • A nivel de registros, todos los datos y direcciones (punteros) existentes en el 80286 extiende su longitud a 32 bits en el 80386. • Dispone de un bus de direcciones de 32 líneas, lo que permite el direccionamiento de 2 = 4 GB de memoria principal. • El numero de segmentos que soporta la memoria virtual es 16.384, o sea el mismo que el 80286. Sin embargo, los segmentos admiten un tamaño de 4 GB, lo que supone una capacidad máxima de 64 TB (TB: tetabyte, es decir, un trillón de bytes). • Todas las instrucciones del 80286 que manejaban operando de 16 bits, han sido modificadas para operar con 32 bits. • El 80386 admite nuevos tipos de datos y una frecuencia de trabajo de 50MHz. • Incorpora nuevos registros de segmento, el FS y el GS, que colaboran con el segmento extra ES en la manipulación de datos. • Trabaja en modo real y en modo protegido, en primer caso no contempla mejoras con respecto al 80286, pero en el modo protegido soporta grandes avances, especialmente, derivados del aumento de la capacidad de memoria virtual y física; además tiene la posibilidad de trabajar en modo virtual 8086, que permite ejecutar un programa para el 8086 en modo protegido como si se tratase de una tarea independiente. • Optativamente, la memoria virtual soporta la paginación. Versiones del 80386 80386SX: para facilitar la transición entre las computadoras de 16 bits basada en el 80286, apareció en junio de 1988 el 80386sx con bus de datos de 16 bits y 24 bits de direcciones (al igual que en el caso del 286). Este microprocesador permitió el armado de computadoras en forma económica que pudieran correr programas de 32 bits. 80386SL: en 1990 Intel introdujo el miembro de alta integración de la familia 80386, el 80386SL, con varias 12 características extras (25 MHz, frecuencia reducida ó 0 MHz, interfaz para caché opcional externo de 16, 32 ó 64 KB, soporte de LIM 4.0 −memoria expandida− por hardware, generación y verificación de paridad, ancho de bus de datos de 8 ó 16 bits) que lo hacen ideal para equipos portátiles. CONJUNTO DE INSTRUCCIONES DEL 80386 Aparte del conjunto de instrucciones del 80286, el 80386 tiene las siguientes nuevas instrucciones: BSF BSR BT BTC BTR BTS CDQ CWDE JECXS LFS LGS LSS MOVSX MOVZX POPAD POPFD PUSHAD PUSHFD SHLD SHRD Búsqueda de un bit hacia adelante Búsqueda de un bit hacia atrás Prueba de un bit Prueba de un bit y complemento Prueba de un bit y puesta a 0 Prueba de un bit y puesta a 1 Convertir doble palabra a palabra cuádruple Convertir palabra a doble palabra extendida Salta si el registro ECX=0 Cargar puntero en el registro F Cargar puntero en el registro G Cargar puntero en el registro S Mover byte, palabra o doble palabra con extensión de signo Mover byte, palabra o doble palabra con extensión de cero Saca todos los registros de la pila Saca el registro de señalizadores de la pila Cargar el contenido de todos los registros en la pila Cargar el registro EFLAGS en la pila Doble desplazamiento a la izquierda Doble desplazamiento a la derecha MICROPROCESADOR 80486 Historia de 80486 Este procesador fue lanzado en Abril de 1989. Posee 32 bits, 1025 millones de transistores, ejecuta 20 millones de instrucciones por segundo, posee multiprocesamiento de datos con velocidades de 25, 33, 50 MHz incluye un cache, un procesador de punto flotante incorporado y una unidad de administración. Arquitectura del 80486 El procesador 80486 es básicamente un 80386 pero contiene una unidad de punto flotante, un cache de memoria de 8 KB adicionales, y una unidad para la administración de la memoria (MMU). El procesador 80486 esta compuesto por los siguientes bloques: • Unidad de ejecución: incluye los registros de uso general de 32 bits, la unidad lógica − aritmética t un barrel shifter de 64 bits. La unidad de ejecución esta mejorada con lo que se necesita un solo ciclo de reloj para las instrucciones mas frecuentes. 13 • Unidad de segmentación: que incluye los registros de segmento, los caches de descriptores y la lógica de protección. Esta unidad no tiene diferencias con respecto al 80386. • Unidad de paginación: es la traductora de las direcciones lineales (generadas por la unidad anterior) en direcciones físicas. • Unidad de cache: debido a la evolución de las memorias el tiempo de acceso de las mismas decreció lentamente, mientras que la velocidad de los microprocesadores aumento significativamente. Por lo que, el acceso a la memoria representaba el cuello de la botella. La idea del cache es tener una memoria relativamente pequeña con la velocidad del procesador. La mayoría del código que se ejecuta lo hace dentro de ciclos, con lo que, si se tiene el ciclo completo dentro del cache, no seria necesario acceder a la memoria externa. Con los datos pasó algo similar: también ocurre un efecto de localidad. El cache se carga rápidamente mediante un proceso como `ráfaga', con el que se pueden transferir cuatro bytes por ciclo de reloj. • Interfaz con el bus: incluye los manejadores del bus de direcciones con salidas de A31−A2 y BE0# a BE3# (mediante esto último cada byte del bus de datos se habilita por separado), bus de datos de 32 bits, y bus de control. • Unidad de instrucciones: incluye la unidad de prebusqueda que le pide a los bytes de instrucciones al cache (ambos se comunican mediante un bus interno de 128 bits), una cola de instrucciones de 32 bytes, la unidad de decodificación, la unidad de control, y la ROM de control (que indican lo que deben hacer las instrucciones). • Unidad de punto flotante: incluye 8 registros de punto flotante de 80 bits y la lógica necesaria para realizar operaciones básicas, raiz cuadrada y transcendentes de punto flotante. Versiones de 80486 • 80486DX: en abril de 1989 Intel presentó su nuevo procesador el 80486DX, que poseía 1,2 millones de transistores a bordo, el doble de la velocidad del 80386 y el 100% de compatibilidad con los microprocesadores anteriores. • 80486SX: en abril de 1991 se presentó el 80486SX, un producto de menor costo que el anterior sin el coprocesador matemático que posee el 80486DX (bajando la cantidad de transistores a 1.185.000). • 80486SL: en 1992 apareció el 80486SL con características especiales en cuanto a ahorro de energía. CONJUNTO DE INSTRUCCIONES DEL 80486 BSWAP CMPXCHG dest,src INVD INVLPG WBINVD XADD dest,src Cambia el orden de los bytes Compara el acumulador con dest Vacía el cache interno Invalida una entrada de página en el buffer de conversión por búsqueda Realiza los cambios indicados en el cache en la memoria externa y luego lo invalida Suma los operandos fuente y destino, poniendo el resultado en el destino. MICROPROCESADOR PENTIUM Historia del PENTIUM El 19 de octubre de 1992, Intel anunció que la quinte generación de su línea de procesadores compatibles (cuyo código interno era el P5) llevaría el nombre de PENTIUM en vez de 586 u 80586, como todo el mundo estaba esperando. Esta fue una estrategia de Intel para poder registrar la marca y así poder diferir el nombre de sus procesadores del de sus competidores (AMD y Cyrix principalmente). 14 Este microprocesador se presentó el 22 de marzo de 1993 con velocidades iniciales de 60 y 66 MHz (112 millones de instrucciones por segundo en el último caso), 3.100.00 transistores (fabricados con el proceso BICMOS −BipolarCMOS−), cache interno de 8 KB para datos y 8 KB para instrucciones, verificación interna de paridad para asegurar la ejecución de las instrucciones, una unidad de punto flotante mejorada, bus de datos de 64 bits para una comunicación más rápida con la memoria externa y, lo mas importante, permite la ejecución de dos instrucciones simultáneamente. El chip se empaqueta en formato PGA (Pin Grid Array) de 273 pines. Luego para el 7 de marzo de 1994 Intel presentó la segunda generación de PENTIUM. Se introdujo con las velocidades de 90 y 100 MHz aplicando una nueva tecnología de 0.6 micrones y posteriormente se introdujeron las versiones de 120,133,150,160 y 200 MHz con tecnologia de 0,35 micrones. Arquitectura del PENTIUM El microprocesador PENTIUM esta conformado por 7 unidades que permiten alta prestaciones, compatibilidad y el mantenimiento de los datos. Estas unidades se dividen en: Unidad de enteros superescalar: Posee en su interior 2 unidades de enteros de 32 bits que operan en paralelo, las cuales constan de segmentación − instrucciones de 5 etapas: prebusqueda de instrucciones, decodificación, calculo, ejecución yescritura de los resultados, cada una de ellas es capaz de funcionar independiente de las otras, dando la sensación de que se encuentran dos procesadores trabajando al mismo tiempo con posibilidades de proporcionar dos resultados enteros por ciclo de reloj. Cada unidad de proceso interno tiene su propia unidad aritmética − lógica, su circuito de generación de direcciones exclusiva e interfaz con la memoria cache de datos. Los resultados de las operaciones se almacenan en la cache interna y no se transfiere a la memoria principal si no es necesario. Estas unidades no son completamente iguales, una de ellas puede solamente procesar solo operaciones simples o de núcleo RISC, y la otra puede realizar instrucciones de compatibilidad y de microprogramas. Existe un bloqueo de la ejecución paralela de instrucciones que se realiza de forma totalmente transparente al software y al usuario, esto se produce cuando hay dependencias entre los operandos de las instrucciones, pero se hacen lo imposible para que siempre haya paralelismo en la ejecución de las instrucciones, siempre y cuando se cumpla todos los requisitos para no perder ningunos datos. Unidades de memoria cache Esta memoria está dividida en dos subsistemas de memoria cache totalmente independientes, son del mismo tamaño 8 octetos. Uno se dedica a almacenar las instrucciones (códigos) y el otro los datos, esto permite la aceleración de la capacidad de transferencia del procesador, organizada como memorias asociativas de dos vías, mucho más eficiente que si fuera de correspondencia directa, el tamaño de la línea es de 32 octetos, el doble que el 486 debido a que el bus externo es de 64 bits. De esta forma permite un acceso de tipo ráfaga que pueda llenar una línea completa de la cache, los buses independientes que abastecen a las caches internas, desde la unidad de bus externa son de 64 bits cada una. Cada cache tiene su propia interfaz con cada una de las unidades de enteros, por lo que se puede proveer de datos o de instrucciones al mismo tiempo a las dos unidades de ejecución para la realización de dos operaciones independientes en un mismo ciclo de reloj, el bus que parte de la cache de datos es de 64 bits y conecta a la cache de instrucciones con los registros de prebusqueda de 256 bits. Los ciclos de ejecución del bus tienen valores medios correspondientes a un 36% de búsqueda de instrucción, 15 un 21% de alturas de datos, un 30% de estructuras de datos y un 7 % de escrituras obligadas de datos. El tipo de ciclo de bus de ráfaga permite cargar 256 bits (32 octetos) en la cache de datos de una vez. El bus externo de 64 bits es capaz de transferir datos entre la memoria y el procesador a velocidades que pueden llegar a 528 octetos por segundo. Unidad de interconexión con el bus Tiene un bus de direcciones de 32 bits pero el bus de datos externos es de 64 bits, el subsitema de memoria esta organizado en ocho grupos de bit cada uno, es decir, 64 bits para adecuarse al bus del procesador, esta organizado en dos bancos de 64 bits cada una de forma que un acceso se haya en un banco y el siguiente en el otro para permitir la recuperación de los chips de memoria y obtener un mejor tiempo de acceso. Consta de una pagina de memoria de cuatro MB, la cual permite un mejor trabajo en entornos gráficos, adaptadores de vídeo del tipo `frame buffer' y sistemas operativos multilaterales, evitando los frecuentes cambios de paginas y disminuyendo en gran medida la probabilidad de ausencia en memoria de la pagina perdida. Al use de grandes objetos esta característica eleva el rendimiento en gran medida. Unidad de predicción de bifurcaciones Esta encargada de hacer una predicción dinámica de donde van a bifurcar las instrucciones del salto condicional, consultando en la BTB (cache especifica de 256 posiciones, buffer de destino de bifurcación) las ultimas 256 instrucciones de este tipo por las que el flujo de ejecución del código haya pasado. Cuando una instrucción produce un salto, la BTB recuerda dicha instrucción y la dirección de salto efectuado, prediciendo en que dirección se va a producir el salto de la próxima vez que se ejecute, si es correcta la divulgación se realiza en 0 ciclos de reloj, si no hay una penalización de tiempo pues hay que anular todas las operaciones efectuadas con las instrucciones que sigan al salto, esto permite un aumento del flujo de ejecución de instrucciones en un 20%. Unidad de punto flotante Se incorpora un cause segmentado de instrucciones de 8 etapas, que permite obtener resultados partiendo de instrucciones de punto flotante en cada ciclo de reloj. Las cuatro primeras etapas son las mismas que posee las unidades de enteros. La quinta y sexta, corresponde a la ejecución de las instrucciones de punto flotante. La séptima etapa se encarga de escribir los resultados en los registros adecuados y la octava realiza el informe de posibles errores que se hayan producido. En cuanto al banco de registros de trabajo, dispone de 16 registros ocho de los cuales actúan como registros de propósito general (EAX, EXB, ECX, EDX, ESP, ESI, EBP y EDI), 6 registros de segmentos (CS, DS, ES, FS, GS y SS), un registro puntero de instrucciones (EPI) y un registro de señalizadores (EFLAGS), como señalizadores de estado (CF, PF, AF, ZF, SF y OF) y señalizadores de estado (TF, IF, ID, IOPL, NT, RM, VM, AC, VIF y VIP). El Pentium sigue el mismo modelo de vía de acceso del 80486. La secuencia de funcionamiento de la vía de datos es: • Prebusqueda: el procesador precapta instrucciones de la cache de instrucciones. • Decodificación 1: el procesador decodifica la instrucción para determinar el código de operación y la información de direccionamiento. Esta etapa también realiza la comprobación de emparejamiento (es decir si las dos instrucciones son sencillas como para ser ejecutadas en un paralelo) y la predicción de 16 salto. • Decodificación 2: genera las direcciones de referencias a memoria. • Ejecución: el procesador accede a la cache de datos o calcula resultados en la ALU o en otras unidades. • Retroescritura: esta etapa actualiza los registros e indicadores con los resultados de la instrucción. CONJUNTO DE INSTRUCCIONES DEL PENTIUM Aparte de las instrucciones del 80486, PENTIUM posee las siguientes nuevas instrucciones CMPXCHG8B CPUID RDMSR RDTSC RSM WRMSR Compara y cambia 8 bits Informa al software acerca del modelo del procesador que se esta utilizando Leer del modelo especifico de registro Copia el resultado en EDX:EAX (Pentium tiene un contador de 64 bits, que se incrementa con cada ciclo de reloj) El estado del procesador se restaura utilizando la copia que se creo al entrar Escribe en el modelo especifico del registro MICROPROCESADOR PENTIUM MMX Para enero de 1998 Intel saca al mercado un nuevo procesador el Pentium MMX, el cual fue lazado al mercado con velocidades de 166, 200, 233 MHz para ordenadores de escritorio, versiones de 150, 166, 200, 233 y 266 MHz para portátiles y versiones OVERDRIVE para equipos de sobremesa 125, 150, 166, 180 y 200 MHz. Con respecto al Pentium Clásico ofrece las siguientes mejoras: • 57 nuevas instrucciones internas diseñadas para procesar con más eficacia datos gráficos, de audio y vídeo. • SIMD (Single Instruction Multiple Data), que permite realizar la misma operación con diferentes datos simultáneamente, especialmente útil con imágenes gráficas, vídeo, audio y animaciones. • Capacidad de realizar dos instrucciones multimedia (MMX)en cada ciclo de reloj. • Doble cantidad de cache: 16KB para datos y 16KB para instrucciones. • Doble de los buffer de escritura y mejora de ejecución de instrucciones en paralelo. • Voltaje menor (2,8 V sólo para el corazón del procesador). Esto da lugar a un menor calentamiento, pero el funcionar con doble voltaje 2,8 V/ 3,3 V indica que algunas placas no l soportan, y por tanto estos procesadores exigen placas modernas. Los procesadores MMX para portátiles funcionan a 1,8 V y 2,0 V internamente. La mejora de prestaciones sobre el Pentium Clásico a igual velocidad no solo se nota ejecutando instrucciones multimedia, puesto que el simple doblaje de la cantidad de cache supone un incremento importante de rapidez de proceso. 17 MICROPROCESADOR PENTIUM II Este procesador fue lanzado al mercado en versiones de 233, 266 y 300 MHz, y mas tarde llega una versión de 333 MHz. Sus características diferenciales con respecto a las anteriores versiones son las siguientes: • Arquitectura del bus dual independiente, que permite múltiples transacciones simultaneas • Incluye instrucciones MMX al igual que el Pentium MMX, para acelerar las operaciones gráficas y 3D, así como las aplicaciones de sonido, vídeo y juegos. • Ejecución dinámica, para acelerar las aplicaciones. • Encapsulado en cartucho SEC (Single Edge Contact − contacto por un solo lado), incluyendo dentro del cartucho el procesador y la cache de segundo nivel, llamado SLOT 1. • Cache de segundo nivel de 512KB funcionando a la mitad de la velocidad del procesador. La versión 333MHz integra dos nuevas instrucciones : FXSAVE y FXSTOR, destinadas ambas a acelerar todos los procesos del sistema operativo. Dichas instrucciones sirven para acelerar el cambio entre operaciones de instrucciones MMX (multimedia) y operaciones del coprocesador matemático integrado en el procesador, pues ambos tipos de operaciones no pueden se ejecutadas simultáneamente. MICROPROCESADOR PENTIUM III La arquitectura de la Pentium III con velocidad de 450 y500 MHz, con cache L2, de 512 K a media velocidad y el mismo gabinete básico Slots, ofrece una característica en su arquitectura SSE (Straming SIMD Extensions) que proporcionan un conjunto de instrucciones y extensiones de microarquitectura que mejoran el desempeño de ciertas aplicaciones de punto flotante intensivo, beneficia a las gráficas 3D, imágenes 2−D, reconocimiento de voz, codificación MPEG−2, aplicaciones científicas y de ingeniería. La SSE tiene 4 avances principales: 8 nuevos registros de punto flotante de 128 bits accesibles en forma directa, 50 nuevas instrucciones diseñadas para operaciones de punto flotante SIMD, 8 nuevas instrucciones enfocadas en el flujo de datos desde y hacia la memoria, 12 integradas de SIMD. Esto le permite tener la capacidad de cuatro valores de punto flotante de precisión individual de 32 bits para empacarse en un registro de 128 bits. Una sola instrucción SSE operaria en 2 de estos registros, efectuando cuatro cálculos de punto flotante simultaneas, también ejecuta instrucciones MMX como SSE, instrucciones de punto flotante estándar SSE. Los registros SSE son accesibles de manera directa sin cuellos de botella, a diferencia de las correspondientes a punto flotante X86. Las instrucciones de flujo de memoria permiten la búsqueda previa de memoria , permitiendo así que los elementos de datas del tamaño de una línea del cache se busquen de la memoria al CPU, con el control de la aplicación un poco antes de que se necesiten en realidad, controlando la ubicación del cache, ayudando a ocultar las latencias de memoria. El bus externo, esta diseñado para manejar múltiples transacciones importantes de bus canalizado en mejora al desempeño de las funciones de búsqueda previa. También existe el flujo de almacenes que permite que el procesador escriba un flujo de datos. Combinación de escritura permite que se combinen múltiples escrituras parciales en localizaciones sucesivas de la memoria en una sola operación de escritura de estallido del tamaño de línea del cache, en los buffer de escritura, mejorando el cual de procedimiento cuando se usa en combinación con el canal de escritura del Pentium III. Su ancho de banda de combinación de escritura del Pentium III en 790 MBps, velocidad que se 18 aproxima al máximo teórico de 800 MBps para su bus a 100 MHz. También implementaron un nuevo serial en su arquitectural, el cual tendrá una identificación digital que si se activa se puede leer en red, siendo una característica de seguridad. CONCLUSION En este trabajo se pudo precisar la arquitectura interna, funcionamiento, avances tecnológicos de los microprocesadores, estudiamos desde el 8080 hasta llegar al Pentium, observando la similitud en las arquitecturas, pero notando sus cambios y avances para lograr mayor seguridad, rapidez, manejo de datos más eficiente y mayor capacidad de almacenamiento. Tomando en cuenta toda esta información podemos concluir que a pesar de los avances de la tecnología, con respecto a los microprocesadores, los cambios que se han dado en su estructura nunca han sido del todo radical, lo que se observa claramente a través de los diagramas de bloques; donde podemos ver correcciones a los anteriores e incorporación de nuevos elementos (para lograr ejecución a mayor velocidad y direccionar mayor cantidad de memoria, pero se puede ver la continuidad de elementos como: la entrada de información a través de direcciones al microprocesador, la unidad de memorias (los registros), la unidad central del proceso donde se ejecutan las instrucciones, y la de salida que regresa el resultado de la ejecución. Así podemos observar que se mantienen los lineamientos básicos a través de la evolución de los microprocesadores. BIBLIOGRAFIA Angulo, José Ma. Microprocesadores. Editorial Paraninfo. Madrid (1984). Brey, BARRY. Los Microprocesadores Intel. Prentice Hall. 3era edicion. (1994)., México. Dollhoff , Terry . 16 bits Microprocessor Architecture. RESTON. Virginia. Hurray , William H. Manual de microprocesador 80386. Editorial Mc Graw Hill 1998 Taub, Herbert. Circuitos digitales y microprocesadores. Editorial Mc Graw Hill 1983 Urunuela, José Ma. Microprocesadores, Programación e interconexión. 2da Edición 1989. INDICE INTRODUCCION .................................................................................... EL MICROPROCESADOR 8080 ............................................................ Historia del 8080 ........................................................................... Conjunto de instrucciones del 8080 .............................................. EL MICROPROCESADOR 8085 ............................................................ Historia del 8085 ........................................................................... Conjunto de instrucciones del 8085 .............................................. EL MICROPROCESADOR 8086/8088 ................................................... 3 4 4 6 9 9 10 10 19 Historia del 8086/8088 .................................................................. Arquitectura interna ....................................................................... Conjunto de instrucciones del 8086/8088 ..................................... EL MICROPROCESADOR 80186/80188 ............................................... EL MICROPROCESADOR 80286 .......................................................... Historia del 80286 ......................................................................... Conjunto de instrucciones del 80286 ............................................ EL MICROPROCESADOR 80386 .......................................................... Historia del 80386 ......................................................................... Arquitectura interna ....................................................................... Versiones del 80386 ..................................................................... Conjunto de instrucciones del 80386 ............................................ EL MICROPROCESADOR 80486 .......................................................... Historia del 80486 ......................................................................... Arquitectura interna ....................................................................... Versiones del 80486 ..................................................................... Conjunto de Instrucciones ............................................................. EL MICROPROCESADOR PENTIUM .................................................... Historia del Pentium ...................................................................... Arquitectura interna ....................................................................... Conjunto de instrucciones de Pentium .......................................... EL MICROPROCESADOR PENTIUM MMX ........................................... EL MICROPROCESADOR PENTIUM II ................................................. EL MICROPROCESADOR PENTIUM III ................................................ DIAGRAMAS DE BLOQUE DE LOS PROCESADORES ....................... CONCLUSION ........................................................................................ BIBLIOGRAFIA ....................................................................................... 10 11 12 14 15 15 16 17 17 17 20 21 21 21 22 23 23 24 24 24 27 28 29 29 31 38 39 36 24 16 64 b 256 b 32 b 32 b 32 b 32 b 20 32 b 32 b 32 b 64 b 64 b 64 b Cache de Datos Registros Unidad de ejecución ALU de enteros ALU de enteros Unidad de interfaz del Bus (BUI) Unidad de Coma flotante Buffer de Prefetch de instrucciones y unidad de decodificación SSE Cache de código Unidad de predicción de ramificaciones 21