arquitectura_computadoras_ISC - Servidor de Apoyo al Sistema

Anuncio

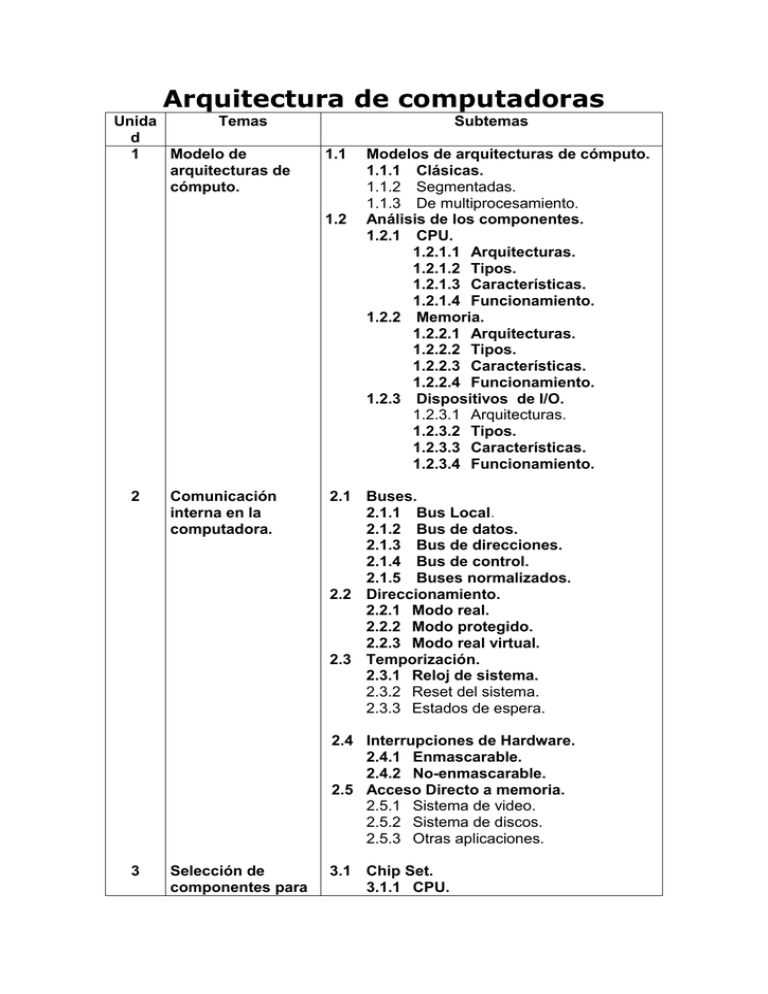

Arquitectura de computadoras

Unida

Temas

d

1

Modelo de

arquitecturas de

cómputo.

Subtemas

1.1

1.2

2

Comunicación

interna en la

computadora.

Modelos de arquitecturas de cómputo.

1.1.1 Clásicas.

1.1.2 Segmentadas.

1.1.3 De multiprocesamiento.

Análisis de los componentes.

1.2.1 CPU.

1.2.1.1 Arquitecturas.

1.2.1.2 Tipos.

1.2.1.3 Características.

1.2.1.4 Funcionamiento.

1.2.2 Memoria.

1.2.2.1 Arquitecturas.

1.2.2.2 Tipos.

1.2.2.3 Características.

1.2.2.4 Funcionamiento.

1.2.3 Dispositivos de I/O.

1.2.3.1 Arquitecturas.

1.2.3.2 Tipos.

1.2.3.3 Características.

1.2.3.4 Funcionamiento.

2.1 Buses.

2.1.1 Bus Local.

2.1.2 Bus de datos.

2.1.3 Bus de direcciones.

2.1.4 Bus de control.

2.1.5 Buses normalizados.

2.2 Direccionamiento.

2.2.1 Modo real.

2.2.2 Modo protegido.

2.2.3 Modo real virtual.

2.3 Temporización.

2.3.1 Reloj de sistema.

2.3.2 Reset del sistema.

2.3.3 Estados de espera.

2.4 Interrupciones de Hardware.

2.4.1 Enmascarable.

2.4.2 No-enmascarable.

2.5 Acceso Directo a memoria.

2.5.1 Sistema de video.

2.5.2 Sistema de discos.

2.5.3 Otras aplicaciones.

3

Selección de

componentes para

3.1 Chip Set.

3.1.1 CPU.

ensamble de

equipos de

cómputo.

4

3.1.2

3.1.3

3.1.4

3.1.5

3.1.6

Controlador del Bus.

Puertos de E/S.

Controlador de Interrupciones.

Controlador de DMA.

Circuitos de temporización y

control.

3.1.7 Controladores de video.

3.2 Aplicaciones.

3.2.1 Entrada/ Salida.

3.2.2 Almacenamiento.

3.2.3 Fuente de alimentación.

3.3 Ambientes de servicios.

3.3.1 Negocios.

3.3.2 Industria.

3.3.3 Comercio electrónico.

Microcontroladores 4.1 Arquitectura.

.

4.1.1 Terminales.

4.1.2 CPU.

4.1.3 Espacio de Memoria.

4.1.4 Entrada/ Salida.

4.1.5 Características especiales.

4.2 Programación.

4.2.1 Modelo de programación.

4.2.2 Conjunto de instrucciones.

4.2.3 Modos de direccionamiento.

4.2.4 Lenguaje ensamblador.

4.3 Aplicaciones.

4.3.1 Como sistema independiente.

4.3.2 Como subsistema de una

computadora.

Unidad 1. Modelo de arquitecturas de

cómputo.

1.1 Modelos de arquitecturas de cómputo.

2

3

Tecnologías RISC y CISC:

RISC: (Reduced Instruction Set Computer) computadora de conjunto de

instrucciones reducido

Arquitectura de computadoras que ejecuta un número limitado de

instrucciones. El concepto es que la mayoría de los programas usan

generalmente unas pocas instrucciones, y si se acelera la ejecución de

esas instrucciones básicas, se mejora el rendimiento.

La arquitectura RISC elimina una capa de carga operativa llamada

"microcódigo", que se emplea normalmente para facilitar la agregación

de nuevas y complejas instrucciones a una computadora. Las

computadoras RISC poseen un pequeño número de instrucciones

montadas en los circuitos de nivel inferior, que trabajan a máxima

velocidad.

Aunque las máquinas RISC son sólo de un 15% a un 50% más veloces

que sus contrapartidas CISC

CISC: (Complex Instruction Set Computer) Computadora de conjunto de

instrucciones complejo Computadoras que poseen un conjunto de

instrucciones muy extenso. Las máquinas CISC tienen de doscientas a

trescientas instrucciones, que están grabadas en microcódigo.

http://www.monografias.com/trabajos/refercomp/refercomp.shtml

3.1.1 Clásicas.

El Concepto de von Neumann.

Los primeros computadores se programaban en realidad recableándolos. Esto

prácticamente equivalía a reconstruir todo el computador cuando se requería

de un nuevo programa. La tarea era simplificada gracias a un panel de

contactos (muy similar al de los primeros conmutadores telefónicos que eran

atendidos por operadoras, y que hoy en día sólo llegamos a ver en viajes

películas en blanco y negro. Ver fig. 1) con el que era posible enlazar circuitos

para crear secciones dedicadas a una actividad específicas. La programación

del computador se llevaba a cabo, literalmente, reconstruyéndolo.

Fig 1.- ENIAC, primer computador electrónico y su panel de conexiones

Mientras que el recablear al computador establecía una clara distinción entre

los datos (representados por los estados o señales eléctricas que serín

mantenidas por los relevadores o a través de los bulbos que conformaban al

computador) y el programa (las conexiones que serían establecidas entre estos

componentes del hardware) la labor de "programación" requería sino del propio

creador del computador si a un verdadero experto y conocedor de electrónica,

principios de lógica digital y del problema mismo. Esto vino a cambiar con el

concepto del programa almacenado, un concepto teórico muy importante que

fue establecido por el matemático John von Neumann el 30 de junio de 1945 en

un borrador sobre el diseño de la EDVAC. A diferencia de los primeros

computadores, von Neumann proponía que tanto el programa como sus datos

fueran almacenados en la memoria del computador. Esto no solo simplificaba

la labor de programación al no tener que llevar a cabo el recableado del

computador sino que además libraba y generalizaba el diseño del hardware

para hacerlo independientede cualquier problema y enfocado al control y

ejecución del programa. Este concepto fue tan importante y decisivo que dio

lugar al concepto de la arquitectura de von Neumann, aún presente en

nuestros días.

La arquitectura de von Neumann se compone de tres elementos:

1. La Unidad Central de Procesamiento (CPU, por sus siglas en inglés), que es

considerada como el cerebro y corazón del computador. Internamente consiste de una

Unidad Aritmético-Lógica (ALU), un conjunto de registros y una Unidad de Control

(CU). La ALU es donde se realizan todas las operaciones que involucran un

procesamiento matemático (particularmente aritmético) o lógico (operaciones

booleanas). Los registros permiten el almacenammiento de datos para estas

operaciones y sus resultados. En la CU es donde se ejecutan todo el resto de las

operaciones (decisión, control, movimiento de datos). Una CPU con todos estos

elementos implementada en un solo chip recibe el nombre de microprocesador.

2. La memoria, que es donde datos y programa es almacenado. La memoria puede ser

visto como un arreglo unidimensional finito en la que cada localidad es identificada por

un valor asociado a su posición y que es comunmente llamado dirección. Existen

diversos tipos de memoria, identificados por el tipo de tecnología usada, aunque para

un computador son generalmente clasificadas en dos grandes grupos por tipo de uso al

que de destina. La memoria RAM (Random Access Memory, Memoria de Acceso

Aleatorio) y que es aquella destinada al almacenamiento de datos y programas

(incluyendo al sistema operativo), es considerada temporal o de tipo volátil ya que

pierde si contenido cuendo el computador es apagadoo reinicializado. La memoria

ROM es aquella de tipo permanente, aun cuando el computador sea desenergizado

mantendrá su contenido. Es usada principalmente para el almacenamiento de

pequeños programas destinados a la adminsitración básica de recursos, especialmente

de entrada y salida.

3. Las interfaces de entrada y salida (I/O). destinadas a liberar de trabajo a la CPU en la

comunidación con dispositivos de entrada (teclados, ratones), salida (impresoras) y

entrada-salidas (discos, cintas).

Estos tres elementos están interconectados a través de un conjunto de líneas

que llevan instrucciones (control bus), datos (data bus) y que permiten dar los

valores de direcciones de memoria y dispositivos (memory bus).

Fig 2.- Esquema de la arquitectura de von Neumann.

http://homepage.mac.com/eravila/computerII.html

La arquitectura von Neumann se refiere a las arquitecturas de computadoras que

utilizan el mismo dispositivo de almacenamiento tanto para las intrucciones como para

los datos (a diferencia de la arquitectura Harvard). El término se acuñó en el documento

First Draft of a Report on the EDVAC (1945), escrito por el conocido matemático John

von Neumann, que propuso el concepto de programa almacenado. Dicho documento fue

redactado en vistas a la construcción del sucesor de la computadora ENIAC, y su

contenido fue desarrollado por Presper Eckert, John Mauchly, Arthur Burks, y otros

durante varios meses antes de que Von Neumann redactara el borrador del informe.

Los ordenadores con arquitectura Von Neumann constan de cinco partes: La unidad

aritmético-lógica o ALU, la unidad de control, la memoria, un dispositivo de

entrada/salida y el bus de datos que proporciona un medio de transporte de los datos

entre las distintas partes.

Un ordenador con arquitectura von Neumann realiza o emula los siguientes pasos

secuencialmente:

1. Obtiene la siguiente instrucción desde la memoria en la dirección indicada por el

contador de programa y la guarda en el registro de instrucción.

2. Aumenta el contador de programa en la longitud de la instrucción para apuntar a

la siguiente.

3. Descodifica la instrucción mediante la unidad de control. Ésta se encarga de

coordinar el resto de componentes del ordenador para realizar una función

determinada.

4. Se ejecuta la instrucción. Ésta puede cambiar el valor del contador del programa,

permitiendo así operaciones repetitivas. El contador puede cambiar también

cuando se cumpla una cierta condición aritmética, haciendo que el ordenador

pueda 'tomar decisiones', que pueden alcanzar cualquier grado de complejidad,

mediante la aritmética y lógica anteriores.

5. Vuelve al paso 1.

Hoy en día, la mayoría de ordenadores están basados en esta arquitectura, aunque

pueden incluir otros dispositivos adicionales, (por ejemplo, para gestionar las

interrupciones de dispositivos externos como ratón, teclado, etc).

http://www.programacion.com/blogs/44_diario_de_un_profesor_de_informtica/a

rchive/409_que_es_la_arquitectura_informtica.html

Arquitectura Harvard

El término Arquitectura Harvard originalmente se refería a las arquitecturas de

computadoras que utilizaban dispositivos de almacenamiento físicamente separados

para las instrucciones y para los datos (en oposición a la Arquitectura von Neumann). El

término proviene de la computadora Harvard Mark I, que almacenaba las instrucciones

en cintas perforadas y los datos en interruptores.

Todas las computadoras constan principalmente de dos partes, la CPU que procesa los

datos, y la memoria que guarda los datos. Cuando hablamos de memoria manejamos

dos parámetros, los datos en sí, y el lugar donde se encuentran almacenados (o

dirección). Los dos son importantes para la CPU, pues muchas instrucciones frecuentes

se traducen a algo así como "coge los datos de ésta dirección y añádelos a los datos de

ésta otra dirección" , sin saber en realidad qué es lo que contienen los datos.

En los últimos años la velocidad de las CPUs ha aumentado mucho en comparación a la

de las memorias con las que trabaja, así que se debe poner mucha atención en reducir el

número de veces que se accede a ella para mantener el rendimiento. Si, por ejemplo,

cada instrucción ejecutada en la CPU requiere un acceso a la memoria, no se gana nada

incrementando la velocidad de la CPU - este problema es conocido como 'limitación de

memoria'.

Se puede fabricar memoria mucho más rápida, pero a costa de un precio muy alto. La

solución, por tanto, es proporcionar una pequeña cantidad de memoria muy rápida

conocida con el nombre de caché. Mientras los datos que necesita el procesador estén en

la caché, el rendimiento será mucho mayor que si la caché tiene que obtener primero los

datos de la memoria principal. La optimización de la caché es un tema muy importante

de cara al diseño de computadoras.

La arquitectura Harvard ofrece una solución particular a este problema. Las

instrucciones y los datos se almacenan en cachés separadas para mejorar el rendimiento.

Por otro lado, tiene el inconveniente de tener que dividir la cantidad de caché entre los

dos, por lo que funciona mejor sólo cuando la frecuencia de lectura de instrucciones y

de datos es aproximadamente la misma. Esta arquitectura suele utilizarse en DSPs, o

procesador de señal digital, usados habitualmente en productos para procesamiento de

audio y video.

"http://es.wikipedia.org/wiki/Arquitectura_Harvard"

Arquitectura Harvard

El procesador de los modernos microcontroladores responde a la arquitectura RISC

(Computadores de Juego de Instrucciones Reducido), que se identifica por poseer un repertorio

de instrucciones máquina pequeño y simple, de forma que la mayor parte de las instrucciones

se ejecutan en un ciclo de instrucción.

Otra aportación frecuente que aumenta el rendimiento del computador es el fomento del

paralelismo implícito, que consiste en la segmentación del procesador (pipe-line),

descomponiéndolo en etapas para poder procesar una instrucción diferente en cada una de

ellas y trabajar con varias a la vez.

http://www.unicrom.com/Tut_PICs1.asp

La arquitectura Harvard dispone de dos memorias independientes una, que

contiene sólo instrucciones y otra, sólo datos. Ambas disponen de sus

respectivos sistemas de buses de acceso y es posible realizar operaciones de

acceso (lectura o escritura) simultáneamente en ambas memorias. Figura 1.3.

Figura 1.3. La arquitectura Harvard dispone de dos memorias independientes

para datos y para instrucciones, permitiendo accesos simultáneos.

http://www.monografias.com/trabajos12/microco/microco.shtml

ARQUITECTURA HARVARD

Arquitectura Harvard, que utiliza antememorias de instrucciones y datos separadas. Esta técnica,

denominada Arquitectura Harvard, en cierto modo contrapuesta a la idea de Von Newmann, ya que utiliza

memorias caché separadas para código y datos. Esto tiene algunas ventajas .

ARQUITECTURA VECTORIAL

El encadenamiento aumenta la velocidad de proceso, pero aún se puede mejorar añadiendo técnicas

como el supersescalado. Esta técnica permite hacer paralelas las mismas etapas sobre instrucciones

diferentes. Un procesador superescalar puede ejecutar más de una instrucción a la vez. Para ésto es

necesario que existan varias unidades aritmético-lógicas, de punto flotante y de control. El proceso que

sigue el micro es transparente al programa, aunque el compilador puede ayudar analizando el código y

generando un flujo de instrucciones optimizado. Veamos cómo se ejecutarían las instrucciones en un

procesador superescalar de que tiene duplicadas las subunidades que lo componen:

Aunque esto mejora la velocidad global del sistema, los conflictos de datos crecen. Si antes las

instrucciones se encontraban muy próximas, ahora se ejecutan simultaneamente. Esto hace necesario un

chequeo dinámico para detectar y resolver los posibles conflictos.

ARQUITECTURA PIPE-LINE

Paralelismo Temporal: Pipe-Line “Lineal”

La arquitectura pipe-line se aplica en dos lugares de la maquina, en la CPU y en la UAL.

Veamos en que consiste el pipe-line y tratemos de entender porque el pipe-line mejora el rendimiento de

todo el sistema.

Veamos una CPU no organizada en pipe-line:

Si se trata de una instrucción a ser ejecutada por la ALU podemos decir que la CPU realiza a lo largo del

ciclo de maquina estas 5 tareas.

Una vez que termina de ejecutar una instrucción va a buscar otra y tarda en ejecutarla un tiempo T, es

decir cada T segundos ejecuta una instrucción.

¿Qué sucede si dividimos en 5 unidades según las 5 cosas que realiza la CPU?

Supongamos la CPU dividida en 5 unidades, de tal forma que c/u tarde lo mismo en realizar su partecita.

Es decir c/u tardará T/5.

Para que una instrucción se ejecute se necesita T segundos entonces para que usar pipe-line.

Si ocurre esto en una CPU normal a una con pipe-line, la cantidad de instrucciones que se hacen por

segundo aumenta, es decir aumenta el flujo de instrucciones que se ejecutan por segundo.

http://html.rincondelvago.com/computadores_arquitectura-harvard-pipelinevectorial.html

Arquitectura PIPE-LINE.

Ya hemos mencionado que una de las formas de lograr operaciones concurrentes en un

procesador se utilizan dos técnicas básicas: paralelismo y pipelining.

El paralelismo conseguía la concurrencia multiplicando la estructura del hardware tantas veces

como sea posible, de modo que las diferentes etapas del proceso se ejecuten

simultáneamente.

Pipelining consiste en desdoblar la función a realizarse en varias partes, asignándole al

hardware correspondiente a cada una de las partes también llamadas etapas. Así como el agua

fluye a través de una tubería (pipeline) las instrucciones o datos fluyen a través de las etapas

de un computador digital pipeline a una velocidad que es independiente de la longitud de la

tubería (numero de etapas del pipeline) y depende solamente de la velocidad a la cual los

datos e instrucciones pueden ingresar al pipeline.

Esta velocidad a su vez depende del tiempo que tarde el dato en atravesar una etapa. Este

tiempo puede ser significativo ya que el computador no solo desplaza los datos o instrucciones

de etapa en etapa sino que en cada una de ellas se realiza alguna operación sobre los mismos.

Como ejemplo en el caso de las instrucciones tendremos operaciones de búsqueda,

decodificación y ejecución.

Pipeline Físico:

Pipeline digital.

Mientras un ítem en particular fluye a través del pipeline, éste ocupa sólo una etapa por vez. A

medida que transcurre el tiempo la etapa que quedo vacante por un ítem, será ocupada por el

siguiente.

Este uso concurrente de diferentes etapas por diferentes ítems se lo conoce por solapamiento.

El resultado neto es que la máxima velocidad a la cual los nuevos ítems pueden ingresar al

pipeline depende exclusivamente del tiempo máximo requerido para atravesar una etapa y no

del número de éstas.

La utilización del pipeline se traduce en una mejora del comportamiento o performance del

procesador. Si una función se lleva a cabo en T segundos en un procesador de diseño

convencional, al utilizar un procesador pipeline de N etapas esa misma función podrá realizarse

en T/N segundos. Esto a nivel teórico, ya que la mejora de performance dependerá de la

cantidad de operaciones que puedan estructurarse en pipeline y también de calidad de la

partición o subdivisión de cada una de esas operaciones. La estructuración en pipeline de un

procesador se realiza en diferentes niveles como aritmética de punto flotante, ciclo de

instrucción, procesador de entrada/salida, etc.

Esta división o partición de una función en varias subfunciones se podrá realizar si se dan las

siguientes condiciones:

1. La evaluación de la función básica es equivalente a la evaluación secuencial de las

subfunciones que la constituyen.

2. Las entradas a una subfunción provienen únicamente de las salidas de subfunciones previas

en la secuencia de evaluación.

3. Excepto el intercambio de entradas y salidas no existe otra vinculación entre las

subfunciones.

4. Debe disponerse del hardware necesario para la evaluación de dichas subfunciones.

5. El tiempo requerido por estas unidades de hardware para evaluar las subfunciones es

aproximadamente el mismo.

Este hardware mencionado en el punto 4 es el correspondiente o asociado con las distintas

etapas del pipeline.

A diferencia del pipeline físico (tubería), el digital no maneja los datos en forma continua. Este

maneja los datos en forma interrumpida y los va desplazando de etapa en etapa sincronizando

con un reloj.

Dado que la lógica que realiza el procesamiento en cada etapa generalmente carece de

memoria y dado el carácter discontinuo de la aparición de los datos en las etapas se impone la

utilización de un elemento de memoria en la entrada y salida de cada etapa. De esta manera,

bajo el control del reloj asociado a cada elemento de memoria, evitamos que los datos ingresen

a una etapa antes que haya finalizado el proceso anterior.

Pipeline vs. Solapamiento.

Los conceptos de pipelining y solapamiento tienen significados parecidos pero no son

equivalentes, pese a que en algunos casos se los utiliza indistintamente. Ambos se basan en la

idea de partición o subdivisión de una función, pero se aplican en distintos entornos.

Se dice que podrá existir pipeline cuando se den las siguientes condiciones:

1. Cada evaluación de la función básica es independiente de las anteriores.

2. Cada evaluación requieren aproximadamente la misma secuencia de subfunciones.

3. Cada subfunción se encadena perfectamente con las anterior.

4. Los tiempos utilizados para evaluar las distintas subfunciones son aproximadamente iguales.

Solapamiento se podrá utilizar cuando se den las siguientes condiciones:

1. Existe dependencia entre las distintas evaluaciones.

2. Cada evaluación puede requerir una secuencia diferente de subfunciones.

3. Cada subfunción tiene un propósito distinto.

4. El tiempo por etapa no es necesariamente constante, sino que depende de la etapa y de los

datos que la atraviesan.

En muchos casos el pipeline propiamente dicho y que detallamos en primer lugar se lo suele

llamar sincrónico o estático, por otra parte el solapamiento se lo suele llamar pipeline

asincronico o dinámico.

Un ejemplo de pipeline estático es el de una unidad destinada a realizar sumas en punto

flotante sobre datos provenientes de otra unidad. Aquí la función básica, suma en punto flotante

es relativamente simple, el resultado de una sumo depende del anterior, próximo o de cualquier

otro. Además una vez que se realizó la partición, todas las sumas siguen la misma secuencia.

El ejemplo más simple de solapamiento o pipeline dinámico se da en un procesador donde la

entrada/salida es manejada por un procesador, los cómputos por otro y la comunicación se

realiza a través de un modulo de memoria común.

La realización de una función en este procesador alternara entre el procesador de computo y el

de entrada/salida.

En otros casos la evaluación de una función sólo requerira de un procesador. En este caso

vemos

que las distintas operaciones están menos sincronizadas que en el caso del sumador en punto

flotante. La

participación de la función básica varía dinámicamente y aún el tiempo empleado en cada

etapa es difícil de

predecir.

Otro ejemplo de operación por solapamiento es el de ejecución de instrucciones de CPU's de

alta

velocidad. En este caso el hardware podrá estar dividido en un número fijo de etapas como en

el caso del

sumador de punto flotante, pero de acuerdo con las diferencias de formato de las instrucciones

cada una

puede desarrollar un camino diferente a través del pipeline.

Pipeline en maquinas SISD.

Dependencia entre instrucciones y riesgos.

En una maquina secuencial clásica todas las operaciones que involucran la ejecución de una

instrucción se completan antes que comience la próxima. En el caso de las maquinas SISD

podemos intentar realizar pipeline a nivel de ejecución de instrucciones.

Esto consistirá en solapar la ejecución de las mismas de manera que algunas de las

operaciones necesarias para las instrucciones i+1, i+2, .... puedan realizarse antes que finalice

la ejecución de la instrucción i. Puede ocurrir que las operaciones realizadas por i+1, i+2,

dependan de los resultados de i que aún no fue completada. Esta dependencia entre

instrucciones crea riesgos que deben evitarse y resolverse.

Se reconocen tres clases de riesgos, read-after-write, write-after-read y write-after-write.

Veamos las diferencias considerando este segmento de código de programa:

Almacenar en x

Sumar x

Almacenar en x

Almacenar en x

El riesgo read-after-write entre dos instrucciones i y j (siendo j posterior a i) se presentara

cuando j trata de leer un operando que es modificado por i. Si la operación en i que modifica el

operando no se completa antes que j lo acceda, entonces j leerá el valor erróneo. En el ejemplo

el riesgo existirá entre el primer almacenar en x y el sumar x, si el sumar x extrae el operando

antes que haya sido actualizado por almacenar.

El write-after-read ocurre cuando la instrucción j desea modificar un operando que es leído por

i. Si j modifica el operando antes que i lo haya leído, este dato así leído será erróneo. Este

riesgo puede existir entre el sumar y el segundo almacenar en x.

Finalmente el write-after-write existe cuando i y j tratan de actualizar el mismo operando, en el

caso que j lo haga en primer lugar. En nuestro ejemplo se el segundo almacenar se realiza

después del tercero, obviamente el valor en x no es el que el programa espera.

3.1.2 Segmentadas.

3.1.3 De multiprocesamiento.

3.2 Análisis de los componentes.

3.2.1 CPU.

Unidad central de proceso o UCP (conocida por sus siglas en inglés, CPU),

circuito microscópico que interpreta y ejecuta instrucciones. La CPU se ocupa

del control y el proceso de datos en las computadoras. Generalmente, la CPU

es un microprocesador fabricado en un chip, un único trozo de silicio que

contiene millones de componentes electrónicos. El microprocesador de la CPU

está formado por una unidad aritmético-lógica que realiza cálculos y

comparaciones, y toma decisiones lógicas (determina si una afirmación es

cierta o falsa mediante las reglas del álgebra de Boole); por una serie de

registros donde se almacena información temporalmente, y por una unidad de

control que interpreta y ejecuta las instrucciones. Para aceptar órdenes del

usuario, acceder a los datos y presentar los resultados, la CPU se comunica a

través de un conjunto de circuitos o conexiones llamado bus. El bus conecta la

CPU a los dispositivos de almacenamiento (por ejemplo, un disco duro), los

dispositivos de entrada (por ejemplo, un teclado o un mouse) y los dispositivos

de salida (por ejemplo, un monitor o una impresora).

Los factores relevantes de los chips de UCP son:

Compatibilidad: No todo el soft es compatible con todas las UCP. En algunos

casos se pueden resolver los problemas de compatibilidad usando software

especial.

Velocidad: La velocidad de una computadora está determinada por la velocidad

de su reloj interno, el dispositivo cronométrico que produce pulsos eléctricos

para sincronizar las operaciones de la computadora. Las computadoras se

describen en función de su velocidad de reloj, que se mide en mega hertz. La

velocidad también está determinada por la arquitectura del procesador, es decir

el diseño que establece de qué manera están colocados en el chip los

componentes individuales de la CPU. Desde la perspectiva del usuario, el

punto crucial es que "más rápido" casi siempre significa "mejor".

El Procesador: El chip más importante de cualquier placa madre es el

procesador. Sin el la computadora no podría funcionar. A menudo este

componente se determina CPU, que describe a la perfección su papel dentro

del sistema. El procesador es realmente el elemento central del proceso de

procesamiento de datos.

Los procesadores se describen en términos de su tamaño de palabra, su

velocidad y la capacidad de su RAM asociada.

Tamaño de la palabra: Es el número de bits que se maneja como una unidad

en un sistema de computación en particular.

Velocidad del procesador: Se mide en diferentes unidades según el tipo de

computador:

MHz (Megahertz): para microcomputadoras. Un oscilador de cristal controla la

ejecución de instrucciones dentro del procesador. La velocidad del procesador

de una micro se mide por su frecuencia de oscilación o por el número de ciclos

de reloj por segundo. El tiempo transcurrido para un ciclo de reloj es

1/frecuencia.

MIPS (Millones de instrucciones por segundo): Para estaciones de trabajo,

minis y macrocomputadoras. Por ejemplo una computadora de 100 MIPS

puede ejecutar 100 millones de instrucciones por segundo.

FLOPS (floating point operations per second, operaciones de punto flotante por

segundo): Para las supercomputadoras. Las operaciones de punto flotante

incluyen cifras muy pequeñas o muy altas. Hay supercomputadoras para las

cuales se puede hablar de GFLOPS (Gigaflops, es decir 1.000 millones de

FLOPS).

Capacidad de la RAM: Se mide en términos del número de bytes que puede

almacenar. Habitualmente se mide en KB y MB, aunque ya hay computadoras

en las que se debe hablar de GB.

http://www.monografias.com/trabajos12/comptcn/comptcn.shtml#UCP

3.2.1.1

Arquitecturas.

Arquitectura interna del CPU

La CPU contiene un conjunto de localidades de almacenamiento temporal de datos de alta

velocidad llamada registro. Algunos de los registros están dedicados al control, y solo la unidad

de control tiene acceso a ellos. Los registros restantes son los registros de uso general y el

programador es el usuario que tiene acceso a ellos.

Dentro del conjunto básico de registros de control se deben incluir a los siguientes:

Contador de programa (PC).

Registro de direcciones de la memoria (MAR).

Registro de datos (RD).

Registro de instrucciones (ER).

Palabra de estado de programa (PSW).

(PC): La función del PC consiste en seguir la pista de la instrucción por buscar (capturar) en

el siguiente ciclo de maquina, por lo tanto contiene la dirección de la siguiente instrucción por

ejecutar. El PC es modificado dentro del ciclo de búsqueda de la instrucción actual mediante la

suma de una constante. El numero que se agrega al PC es la longitud de una instrucción en

palabras.

Por lo tanto, si una instrucción tiene una palabra de longitud se agrega 1 al PC, si una

instrucción tiene dos palabras de largo se agrega 2, y así sucesivamente.

Registro de direcciones de la memoria (MAR): funciona como registro de enlace entre

la CPU y el canal de direcciones. Cuando se logra el acceso a la memoria la dirección es

colocada en el MAR por la unidad de control y ahí permanece hasta que se completa la

transacción. El numero de bit que hay en el MAR es igual al del canal de direcciones.

La diferencia que existe entre el PC y el MAR es que durante el ciclo de ejecución de una

instrucción, el PC y el MAR sirven al mismo fin. Sin embargo, muchas de las instrucciones de la

maquina hacen referencia a la memoria y operan con los datos que están en ella. Como la

dirección de los datos suele ser diferente de la instrucción siguiente se necesita el MAR.

Registro de datos: la función del RD consiste en proporcionar un área de almacenamiento

temporal (memoria intermedia, acumulada o buffer) de datos que se intercambian entre la PCU

y la memoria. Los datos pueden ser instrucciones (obtenidos en el ciclo de ejecución) o datos

del operando (obtenidos en el ciclo de ejecución). Debido a su conexión directa con el canal de

datos el RD contiene el mismo numero de bit que dicho canal.

Registro de instrucciones (ER): es un registro que conserva el código de operación de la

instrucción en todo el ciclo de la maquina. El código es empleado por la unidad de control de la

CPU para generar las señales apropiadas que controla le ejecución de la instrucción. La longitud

del ER es la longitud en bit del código de operación.

Palabra de estado de programa (PSW): la palabra de estado o condición de programa

almacena información pertinente sobre el programa que este ejecutándose. Por ejemplo al

completarse una función de la unidad aritmética lógica se modifica un conjunto de bit llamados

códigos (o señales de condición). Estos bit especifican si el resultado de una operación

aritmética fue 0 o negativo o si el resultado se desbordó.

El programa puede verificar estos bit en las instrucciones siguientes cambiar en forma

condicional su flujo de control según su valor.

Además el PSW contiene bit que hacen posible que la computadora responda a solicitudes de

servicio asincrónicas generadas por dispositivos de Entrada-Salida, o condiciones de error

interno. Estas señales se denominan interrupciones.

Los registros restantes que se pueden encontrar en un microprocesador son de uso general.

Estos se utilizan para almacenar información en forma temporal. También retienen operandos

que participan en operaciones de la ULA.

Algunas veces el conjunto de instrucciones de la computadora y el esquema de

direccionamiento de la arquitectura restringe el uso de alguno de estos registros.

Si bien en todas las maquinas la información contenida en el registro puede manipularse como

datos ordinarios durante la ejecución de algunas instrucciones los datos se utilizan en forma

explícita para decidir una dirección de la memoria. La ventaja de usar registros para retener

datos de operaciones es la velocidad.

http://html.rincondelvago.com/arquitectura-interna-de-la-cpu.html

Elementos que la componen

1. Unidad de control: controla el funcionamiento de la CPU y por tanto de el

computador.

2. Unidad aritmético-lógica (ALU): encargada de llevar a cabo las funciones de

procesamiento de datos del computador.

3. Registros: proporcionan almacenamiento interno a la CPU.

4. Interconexiones CPU: Son mecanismos que proporcionan comunicación entre la

unidad de control, la ALU y los registros.

Unidad de Control.

La Unidad de Control (UC) coordina la actividad de todos los elementos que deben

intervenir en un proceso concreto. Dirige todas las señales eléctricas del ordenador, es

decir, es responsable del correcto funcionamiento de todos los componentes de la CPU.

De esta forma, debe gobernar el funcionamiento de los periféricos de entrada, salida y

almacenamiento, al mismo tiempo que el acceso a la memoria principal y la ALU. Por

esta razón la UC es la encargada de interpretar el programa, del que recibe las

instrucciones codificadas convenientemente, así como de enviar las órdenes oportunas a

las unidades periféricas implicadas.

La UC utiliza una señal generada por un reloj interno con objeto de sincronizar el

funcionamiento operativo de cada elemento. Esta tarea es fundamental, ya que, en caso

contrario, no podría establecerse un ritmo de operación adecuado que controle la

velocidad de trabajo de cada componente. Se comprende fácilmente que la mayor o

menor frecuencia del reloj interno, determinará la capacidad de hacer un número mayor

o menor de instrucciones por segundo. Esta velocidad se suele medir actualmente en

gigahertzios (GHz). No todas las instrucciones que tenga que ejecutar la UC consumen

el mismo número de señales generadas por el reloj, sino que las instrucciones complejas

necesitarán más ciclos que las instrucciones simples.

En cualquier caso, la UC se encargará de las siguientes funciones:

Determinar si el ordenador está en fase de introducción o en fase de ejecución de

programa. En el primer caso, la UC activa la unidad de entrada de datos y

controla que las sucesivas instrucciones que componen el programa vayan

siendo almacenadas en posiciones contiguas de memoria. En la fase de ejecución

del programa, la UC decodifica la primera instrucción del programa y según el

tipo de instrucción pide su ejecución al dispositivo adecuado: las entradas y

salidas a los periféricos y las operaciones aritméticas y lógicas a la ALU.

Decodificar la instrucción en curso y, según su código de operación, mandar una

señal para que actúe la Unidad Aritmético-Lógica o una Unidad de entrada o de

salida.

Verificar la transferencia de información entre los registros y la memoria

principal y viceversa.

Controlar qué instrucción se está ejecutando en cada momento y qué instrucción

deberá seguirle a continuación.

Unidad Aritmético-Logica.

La Unidad Aritmético-Lógica (ALU, Arithmetic-Logical Unit) es la encargada de

ejecutar las operaciones aritméticas básicas (suma, resta, multiplicación y división) y

lógicas (AND, OR, NOT). Sólo con estas operaciones básicas es procesada toda la

información y se obtienen los resultados. Los datos sobre los que opera esta unidad

provienen de la memoria principal y pueden estar almacenados temporalmente en

algunos registros internos de la propia unidad.

La UC se encarga de enviarle los datos correspondientes e indicarle qué operación tiene

que realizar.

3.2.1.2

Tipos.

Tipos

Básicamente nos encontramos con dos tipos de diseño de los microprocesadores: RISC

(Reduced-Instruction-Set Computing) y CISC (complex-instruction-set computing). Los

microprocesadores RISC se basan en la idea de que la mayoría de las instrucciones para

realizar procesos en el computador son relativamente simples por lo que se minimiza el

número de instrucciones y su complejidad a la hora de diseñar la CPU. Algunos ejemplos de

arquitectura RISC son el SPARC de Sun Microsystem’s, el microprocesador Alpha diseñado

por la antigua Digital, hoy absorbida por Compaq y los Motorola 88000 y PowerPC. Estos

procesadores se suelen emplear en aplicaciones industriales y profesionales por su gran

rendimiento y fiabilidad.

Los microprocesadores CISC, al contrario, tienen una gran cantidad de instrucciones y por

tanto son muy rápidos procesando código complejo. Las CPU´s CISC más extendidas son las

de la familia 80x86 de Intel cuyo último micro es el Pentium II. Últimamente han aparecido

otras compañías como Cirix y AMD que fabrican procesadores con el juego de instrucciones

80x86 y a un precio sensiblemente inferior al de los microprocesadores de Intel. Además,

tanto Intel con MMX como AMD con su especificación 3D-Now! están apostando por

extender el conjunto de instrucciones de la CPU para que trabaje más eficientemente con

tratamiento de imágenes y aplicaciones en 3 dimensiones.

3.2.1.3

Características.

La CPU ha de cumplir dos características bien definidas:

1. Ser capaz de reconocer y ejecutar una serie de instrucciones elementales

(programa) en base a las cuales se puede realizar cualquier proceso de datos

deseado, por complejo que sea.

2. Tener separados dos estados diferentes. En una primera fase ha de poder recibir

y memorizar las instrucciones que configuran el proceso pedido (introducción

del programa) y en segunda fase debe ejecutar en secuencia las instrucciones

recibidas (ejecución del programa). Al realizar esta ejecución se leerán los datos

que se necesiten a través de un dispositivo de entrada de datos en el momento en

que sean requeridos, realizando las operaciones que forman el proceso hasta la

obtención de los resultados, los cuales serán enviados al usuario a través de un

dispositivo de salida.

3.2.1.4

Funcionamiento.

Funciones que realiza

La Unidad central de proceso o CPU, se puede definir como un circuito microscópico

que interpreta y ejecuta instrucciones. La CPU se ocupa del control y el proceso de

datos en los ordenadores. Habitualmente, la CPU es un microprocesador fabricado en

un chip, un único trozo de silicio que contiene millones de componentes electrónicos. El

microprocesador de la CPU está formado por una unidad aritmético-lógica que realiza

cálculos y comparaciones, y toma decisiones lógicas (determina si una afirmación es

cierta o falsa mediante las reglas del álgebra de Boole); por una serie de registros donde

se almacena información temporalmente, y por una unidad de control que interpreta y

ejecuta las instrucciones. Para aceptar órdenes del usuario, acceder a los datos y

presentar los resultados, la CPU se comunica a través de un conjunto de circuitos o

conexiones llamado bus. El bus conecta la CPU a los dispositivos de almacenamiento

(por ejemplo, un disco duro), los dispositivos de entrada (por ejemplo, un teclado o un

mouse) y los dispositivos de salida (por ejemplo, un monitor o una impresora).

3.2.2 Memoria.

Se denomina memoria a los circuitos que permiten almacenar y recuperar la información. En

un sentido más amplio, puede referirse también a sistemas externos de almacenamiento, como

las unidades de disco o de cinta. Memoria de acceso aleatorio o RAM (Random Access

Memory) es la memoria basada en semiconductores que puede ser leída y escrita por el

microprocesador u otros dispositivos de hardware. El acceso a las posiciones de

almacenamiento se puede realizar en cualquier orden.

Los chips de memoria son pequeños rectángulos negros que suelen ir soldados en grupos a

unas plaquitas con "pines" o contactos. La diferencia entre la RAM y otros tipos de memoria de

almacenamiento, como los disquetes o los discos duros, es que la RAM es muchísimo más

rápida, y que se borra al apagar el ordenador, no como éstos.

El interior de cada chip se puede imaginar como una matriz o tabla, en la cual cada

celda es capaz de almacenar un bit. Por tanto, un bit se puede localizar directamente

proporcionando una fila y una columna de la tabla. En realidad, la CPU identifica cada

celda mediante un número , denominado dirección de memoria. A partir de una

dirección, se calcula cuál es la fila y columna correspondiente, con lo que ya se puede

acceder a la celda deseada. El acceso se realiza en dos pasos: primero se comunica la

fila y luego la columna, empleando los mismos terminales de conexión. Obviamente,

esta técnica (denominada multiplexado) permite emplear menos terminales de conexión

para acceder a la RAM, lo que optimiza la relación entre el tamaño del chip y la

capacidad de almacenamiento.

Realmente, la CPU no suele trabajar con bits independientes, sino más bien con

agrupaciones de los mismos en forma de palabras binarias. Esto hace que la RAM no se

presente en un solo chip, sino más bien en agrupaciones de los mismos.

Hemos de tener muy en cuenta que esta memoria es la que mantiene los programas

funcionando y abiertos, por lo que al ser Windows 95/98 un sistema operativo multitarea,

estaremos a merced de la cantidad de memoria RAM que tengamos dispuesta en el ordenador.

En la actualidad hemos de disponer de la mayor cantidad posible de ésta, ya que estamos

supeditados al funcionamiento más rápido o más lento de nuestras aplicaciones diarias. La

memoria RAM hace unos años era muy cara, pero hoy en día su precio ha bajado

considerablemente.

Cuando alguien se pregunta cuánta memoria RAM necesitará debe sopesar con qué

programas va a trabajar normalmente. Si únicamente vamos a trabajar con aplicaciones de

texto, hojas de cálculo y similares nos bastará con unos 32 Mb de ésta (aunque esta cifra se ha

quedado bastante corta), pero si trabajamos con multimedia, fotografía, vídeo o CAD, por poner

un ejemplo, hemos de contar con la máxima cantidad de memoria RAM en nuestro equipo

(unos 128 Mb o más) para que su funcionamiento sea óptimo, ya que estos programas son

auténticos devoradores de memoria. Hoy en día no es recomendable tener menos de 64 Mb,

para el buen funcionamiento tanto de Windows como de las aplicaciones normales, ya que

notaremos considerablemente su rapidez y rendimiento, pues generalmente los equipos

actuales ya traen 128 Mb de RAM.

3.2.2.1

Arquitecturas.

Elementos que la componen

Una memoria vista desde el exterior, tiene la estructura mostrada en la figura 3-1. Para

efectuar una lectura se deposita en el bus de direcciones la dirección de la palabra de

memoria que se desea leer y entonces se activa la señal de lectura (R); después de cierto

tiempo (tiempo de latencia de la memoria), en el bus de datos aparecerá el contenido de

la dirección buscada. Por otra parte, para realizar una escritura se deposita en el bus de

datos la información que se desea escribir y en el bus de direcciones la dirección donde

deseamos escribirla, entonces se activa la señal de escritura (W), pasado el tiempo de

latencia, la memoria escribirá la información en la dirección deseada. Internamente la

memoria tiene un registro de dirección (MAR, memory address register), un registro

buffer de memoria o registro de datos (MB, memory buffer, o MDR, memory data

register) y, un decodificador como se ve en la figura 3-2. Esta forma de estructurar la

memoria se llama organización lineal o de una dimensión. En la figura cada línea de

palabra activa todas las células de memoria que corresponden a la misma palabra.

Por otra parte, en una memoria ROM programable por el usuario con organización

lineal, las uniones de los diodos correspondientes a lugares donde deba haber un "0"

deben destruirse. También se pueden sustituir los diodos por transistores y entonces la

célula de memoria tiene el esquema de la figura 3-3 en este caso la unión que debe

destruirse para grabar un "0" es la del emisor.

En el caso de una memoria RAM estática con organización lineal cada célula de

memoria toma la forma mostrada en la figura 3-4. En este esquema las primeras puertas

AND sólo son necesarias en el una de las células de cada palabra. Se debe comentar la

necesidad de la puerta de tres estados a la salida del biestable: esta puerta se pone para

evitar que se unan las salidas de los circuitos de las células de diferentes palabras a

través del hilo de bit. Si esa puerta no se pusiera (o hubiera otro tipo de puerta en su

lugar, como una puerta AND) la información correspondiente a la palabra activa

entraría por los circuitos de salida de las demás células, lo que los dañaría.

Organizar 1a memoria de esta forma, tiene el inconveniente de que la complejidad del

decodificador crece exponencialmente con el número de entradas y, en una memoria de

mucha capacidad, la complejidad del decodificador la hace inviable. Esto hace necesaria

una alternativa que simplifique los decodificadores. Esta alternativa la constituye la

organización en dos dimensiones en que los bits del registro de dirección se dividen en

dos partes y cada una de ellas va a un decodificador diferente. En este caso, las líneas

procedentes de ambos decodificadores (X e Y) se cruzan formando un sistema de

coordenadas en que cada punto de cruce corresponde a una palabra de memoria. Dado

que en cada decodificador sólo se activa una línea, sólo se activará la palabra

correspondiente al punto de cruce de las dos líneas activadas. Fácilmente se puede

comprender que los decodificadores se simplifican mucho ya que cada uno tiene la

mitad de entradas que en el caso anterior. Hay que decir, sin embargo, que la célula de

memoria se complica un poco porque hay que añadir una puerta AND en cada palabra

para determinar si coinciden las líneas X e Y.

La organización de la memoria en dos dimensiones también es útil para las memorias

dinámicas ya que el refresco de estas memorias se realiza por bloques y éstos pueden

coincidir con una de las dimensiones (la que corresponda a los bits de dirección de

mayor peso).

En la práctica, las memorias dinámicas son más lentas que las estáticas y además son de

lectura destructiva, pero resultan más baratas, aunque necesiten circuitos de refresco, si

la memoria no es de mucha capacidad.

3.2.2.2

Tipos.

Tipos

y

Funcionamiento

Todas hacen la misma función, pero entre ellas las diferenciamos por el tiempo de acceso y la

capacidad, o por el modo como trabajan:

· Registros del microprocesador: Interaccionan continuamente con la CPU, puesto que forman

parte de ella, su tiempo de acceso es muy pequeño y una capacidad mínima, normalmente igual a

la

"palabra"

del

microprocesador

(de

1

a

8

bytes).

· Registros intermedios: Básicamente es un paso intermedio entre dos memorias, un buffer. Tiene

capacidad

muy

pequeña

y

un

tiempo

de

acceso

también

muy

pequeño.

· Memoria caché: Es la más utilizada por la CPU, y la más importante entre la principal y el

microprocesador. Aunque sean de pequeña capacidad, normalmente una fracción de la memoria

principal máxima posible, está continuamente intercambiando información tanto con el procesador

como con la memoria principal, aunque normalmente se utiliza para guardar la dirección de la

memoria principal, en vez de almacenar el archivo entero, así tarda menos a pasar la información

hacia la CPU, que si lo hiciera mediante la caché.

Y es por esta razón, que a menudo (excepto modelos especiales como Celeron y Duron), hay

dos de memorias caché, dos niveles: Uno en el interior del microprocesador (L1), y el otro entre la

principal y la CPU (L2), al exterior del "micro" de más capacidad que la de dentro.

· Memoria central o principal: Donde se almacenan programas y datos. La CPU lee y escribe en ella

aunque en menos cantidades que en las anteriores. Tiempo de acceso relativamente rápido y gran

capacidad.

· Memorias de masas o auxiliares: Son dispositivos exteriores al ordenador o conectados a la placa

base por un controlador de bus (disco duro, disquetes, etc.). Dónde se almacenen todos los

programas y archivos para un uso posterior. En caso de que la memoria principal sea insuficiente,

se hacen servir como apoyo para ésta, denominada "memoria virtual".

Como he mencionado anteriormente, las memorias además de clasificarse por su tiempo de

acceso y capacidad, también se pueden clasificar por la forma en que se modifican los datos y la

tecnología empleada. Así, encontramos que hay dos grandes grupos:

1. Memorias RAM (Random Acces Memory): Son memorias en las que se puede leer y escribir. Se

componen electrónicamente por chips, dónde se pueden subdividir en:

·

SRAM

(Static

RAM):

Su

célula

está

basada

en

un

biestable.

· DRAM (Dinamic RAM): Su célula está basada en un pequeño condensador, carga del cual

representa la información almacenada. Estas necesitan circuitos adicionales de refresco, puesto

que como los condensadores son de baja capacidad, a través de la s fugas, la información se podría

perder; son de lectura destructiva.

2. Memorias ROM (Read Only Memory): Son memorias en las que sólo se puede leer. Hay de varios

tipos:

· ROM: programadas por máscara, la información es grabada enla fábrica y no tiene posible

modificación.

·

PROM,

o

ROM:

programable

una

sola

vez.

· EPROM (Erasable PROM) o RPROM (Reprogramable ROM): su contenido puede ser borrado

mediante

rayos

ultravioletas,

para

acto

seguido

regrabarlas.

· EAROM (Electrically Alterable ROM) o EEROM (Electrically Erasable ROM), son la frontera entre

las RAM y las ROM, su contenido puede ser regrabado eléctricamente, se diferencian de las RAM en

que

no

son

volátiles.

· Memoria FLASH, denominada así por la velocidad en la que se puede reprogramar (en tan solo

segundos), usan el borrado eléctrico.

Básicamente las ROM se basan en una matriz de diodos unidos, esta unión puede ser destruida

por una sobretensión. De esta forma, salen de la fábrica con las uniones juntas y para grabarlas se

rompen dónde se quieran poner ceros.

Aparte de los módulos de memoria aquí mencionados también existen, aunque ya en desuso, de

otros como los SIMM (Single In<-Line Memory Module) y los SIP (Single In-Line Packages), los

cuales no son nada más que chips de memoria soldados entre ellos para formar un único conjunto.

También hay modelos más nuevos como el DDR (DobleData Rate) que se usa básicamente en

equipos basados en microprocesadores AMD, ahora implementados también en equipos Intel,

aunque principalmente se usan en las tarjetas gráficas, aunque Intel ya posee la del tipo RAMBUS.

La DDR es el mismo que la SDR pero en doble sentido, de ida y de vuelta, mientras que la

segunda(SDR) solamente puede hacer servir un sentido ida o vuelta.

http://www.hardware12v.com/conocimientospc/5.php

Tipos de Memoria RAM

DRAM (Dynamic Random Access Memory): Es la memoria de trabajo, también llamada

RAM, esta organizada en direcciones que son reemplazadas muchas veces por segundo. Esta

memoria llegó a alcanzar velocidades de 80 y 70 nanosegundos (ns), esto es el tiempo que

tarda en vaciar una dirección para poder dar entrada a la siguiente, entre menor sea el número,

mayor la velocidad, y fué utilizada hasta la época de los equipos 386.

FPM (Fast Page Mode): El nombre de esta memoria procede del modo en el que hace

la transferencia de datos, que también es llamado paginamiento rápido. Hasta hace

aproximadamente un año ésta memoria era la más popular, era el tipo de memoria normal para

las computadores 386, 486 y los primeros Pentium®, llegó a fabricarse en velocidades de 60ns

y la forma que presentaban era en módulos SIMM de 30 pines, para los equipos 386 y 486 y

para los equipos Pentium® era en SIMM de 72 pines.

EDO (Extended Data Output): Esta memoria fue una innovación en cuestión de transmisión de

datos pudiendo alcanzar velocidades de hasta 45ns, dejando satisfechos a los usuarios. La

transmisión se efectuaba por bloques de memoria y no por instrucción como lo venía haciendo

las memorias FPM. Se utiliza en equipos con procesadores Pentium®, Pentium Pro® y los

primeros Pentium II®, además de su alta compatibilidad, tienen un precio bajo y es una opción

viable para estos equipos. Su presentación puede ser en SIMM ó DIMM.

SDRAM (Synchronous DRAM): Esta memoria funciona como su nombre lo indica, se

sincroniza con el reloj del procesador obteniendo información en cada ciclo de reloj, sin tener

que esperar como en los casos anteriores. La memoria SDRAM puede aceptar velocidades de

BUS de hasta 100Mhz, lo que nos refleja una muy buena estabilidad y alcanzar velocidades de

10ns. Se presentan en módulos DIMM, y debido a su transferencia de 64 bits, no es nesesario

instalarlo en pares.

RDRAM (Rambus DRAM): Esta memoria tiene una transferencia de datos de 64 bits

que se pueden producir en ráfagas de 2ns, además puede alcanzar taza de tranferencia de 533

Mhz con picos de 1.6Gb/s. Muy pronto alcanzará dominio en el mercado, ya que se estará

utilizando en equipos con el nuevo procesador Pentium 4®. Es ideal ya que evita los cuellos de

botella entre la tarjeta gráfica AGP y la memoria del sistema, hoy en día se pueden encontrar

éste tipo de memorias en las consolas NINTENDO 64®. Será lanzada al mercado por

SAMSUNG® e HITACHI®.

Tipos de Memoria ROM

EPROM (Erasable Programmable Read-Only Memory): Se utiliza para corregir errores

de última hora en la ROM, el usuario no la puede modificar y puede ser borrada exponiendo la

ROM a una luz ultravioleta.

EEPROM (Electrically Erasable Programmable Read-Only Memory): Esta memoria puede ser

borrada y volver a ser programada por medio de una carga eléctrica, pero sólo se puede

cambiar un byte de información a la vez.

MEMORIA FLASH: Es un tipo de memoria EEPROM que es reprogramable, su

utilización por lo regular es en BIOS de ahí su nombre.

Otros tipos de memoria RAM

BEDO (Burst Extended Data Output): Fue diseñada para alcanzar mayores velocidades

de BUS. Trabaja de igual forma que la SDRAM, ó sea, la transferencia de datos se hace en

cada ciclo de reloj, pero esta memoria lo hace en ráfagas (burst), haciendo que los tiempos de

entrega desaparezcan casi totalmente.

DDR SDRAM (Double Data Rate SDRAM ó SDRAM-II): Esta memoria tendrá el mismo

aspecto que un DIMM, pero la diferencia estará en que tendrá más pines, pasando de 168

pines del actual DIMM a 184 pines, además de tener sólo una muesca en la tableta. Viendo un

poco de voltaje, la DDR trabajará con tan sólo 2.5V, siendo ésta una reducción del 30%

respecto a los actuales 3.3V de la SDRAM. Trabajará a velocidades de 200Mhz.

VRAM: Es como la memoria RAM normal, pero la diferencia reditúa en que podrá ser

accedida al mismo tiempo por el monitor y el procesador de la tarjeta de video, se podrá leer y

escribir en ella al mismo tiempo.

SGRAM (Synchronous Graphic RAM): Ofrece las mismas capacidades de la memoria

SDRAM pero para las tarjetas gráficas, se utiliza en las nuevas tarjetas gráficas aceleradoras

3D.

http://www.monografias.com/trabajos14/dispositivos/dispositivos.shtml#

Jerarquía de memoria

En un ordenador hay una jerarquía de memorias atendiendo al tiempo de acceso y a la

capacidad que. normalmente son factores contrapuestos por razones económicas y en

muchos casos también físicas. Comenzando desde el procesador al exterior, es decir en

orden creciente de tiempo de acceso y capacidad, se puede establecer la siguiente

jerarquía:

Registros de procesador: Estos registros interaccionan continuamente con la CPU

(porque forman parte de ella). Los registros tienen un tiempo de acceso muy pequeño y

una capacidad mínima, normalmente igual a la palabra del procesador (1 a 8 bytes).

Registros intermedios: Constituyen un paso intermedio entre el procesador y la

memoria, tienen un tiempo de acceso muy breve y muy poca capacidad.

Memorias caché: Son memorias de pequeña capacidad. Normalmente una pequeña

fracción de la memoria principal. y pequeño tiempo de acceso. Este nivel de memoria se

coloca entre la CPU y la memoria central. Hace algunos años este nivel era exclusivo de

los ordenadores grandes pero actualmente todos los ordenadores lo incorporan. Dentro

de la memoria caché puede haber, a su vez, dos niveles denominados caché on chip,

memoria caché dentro del circuito integrado, y caché on board, memoria caché en la

placa de circuito impreso pero fuera del circuito integrado, evidentemente, por razones

físicas, la primera es mucho más rápida que la segunda. Existe también una técnica,

denominada Arquitectura Harvard, en cierto modo contrapuesta a la idea de Von

Newmann, que utiliza memorias caché separadas para código y datos. Esto tiene

algunas ventajas como se verá en este capítulo.

Memoria central o principal: En este nivel residen los programas y los datos. La CPU

lee y escribe datos en él aunque con menos frecuencia que en los niveles anteriores.

Tiene un tiempo de acceso relativamente rápido y gran capacidad.

Extensiones de memoria central: Son memorias de la misma naturaleza que la

memoria central que amplían su capacidad de forma modular. El tiempo de similar, a lo

sumo un poco mayor, al de la memoria central y su capacidad puede ser algunas veces

mayor.

Memorias de masas o auxiliares: Son memorias que residen en dispositivos externos

al ordenador, en ellas se archivan programas y datos para su uso posterior. También se

usan estas memorias para apoyo de la memoria central en caso de que ésta sea

insuficiente (memoria virtual). Estas memorias suelen tener gran capacidad pero pueden

llegar a tener un tiempo de acceso muy lento. Dentro de ellas también se pueden

establecer varios niveles de jerarquía.

Clasificación de memorias semiconductoras de acceso aleatorio

Las memorias se clasifican, por la tecnología empleada y, además según la forma en que

se puede modificar su contenido, A este respecto, las memorias se clasifican en dos

grandes grupos:

1) Memorias RAM: Son memorias en las que se puede leer y escribir, si bien su nombre

(Random access memory) no representa correctamente este hecho. Por su tecnología

pueden ser de ferritas (ya en desuso) o electrónicas, Dentro de éstas últimas hay

memorias estáticas (SRAM, static RAM), cuya célula de memoria está basada en un

biestable, y memorias dinámicas (DRAM, dinamic RAM, en las que la célula de

memoria es un pequeño condensador cuya carga representa la información almacenada.

Las memorias dinámicas necesitan circuitos adicionales de refresco ya que los

condensadores tienen muy poca capacidad y, a través de las fugas, la información puede

perderse, por otra parte, son de lectura destructiva.

2) Memorias ROM (Read 0nly Memory): Son memorias en las que sólo se puede leer.

Pueden ser:

a. ROM programadas por máscara, cuya información se graba en fábrica

y no se puede modificar.

b. PROM, o ROM programable una sola vez.

c. EPROM (erasable PROM) o RPROM (reprogramable ROM), cuyo

contenido puede borrarse mediante rayos ultravioletas para regrabarlas.

d. EAROM (electrically alterable ROM) o EEROM (electrically erasable

ROM), que son memorias que está en la frontera entre las RAM y las

ROM ya que su contenido puede regrabarse por medios eléctricos,

estas se diferencian de las RAM en que no son volátiles. En ocasiones

a este tipo de memorias también se las denomina NYRAM (no volátil

RAM).

e. Memoria FLASH, denominada así por la velocidad con la que puede

reprogramarse, utilizan tecnología de borrado eléctrico al igual que las

EEPROM. Las memorias flash pueden borrarse enteras en unos

cuantos segundos, mucho más rápido que las EPROM.

Básicamente las memorias ROM se basan en una matriz de diodos cuya unión se puede

destruir aplicando sobre ella una sobretensión (usualmente comprendida ente -12.5 y 40 v.). De fábrica la memoria sale con 1's en todas sus posiciones, para grabarla se

rompen las uniones en que se quieran poner 0's. Esta forma de realizar la grabación se

denomina técnica de los fusibles.

Los tipos más usados de memoria RAM son los siguientes:

DRAM (Dinamic-RAM): La primera memoria hasta la aparición de los 386, era algo

lenta (70 ó 80 ns). En formato DIMM o SIMM de 30 contactos.

Fast Page (FPM o DRAM): Algo más rápida que la anterior (70 ó 60 ns). Se presenta

en formato SIMM de 30 ó 72 contactos.

EDO-RAM (Extended Data Output-RAM): Permite empezar a introducir nuevos datos

mientras los anteriores están saliendo (70, 60 ó 50 ns), lo que la hace algo más rápida

(un 5% más que la FPM). Vienen en SIMMs de 72 contactos, aunque también los hay

en DIMM de 168.

SDRAM (Sincronic-RAM): Funciona sincronizadamente con la velocidad de la placa (de

50 a 66 MHz), para lo que debe ser rapidísima (de 25 a 10 ns) y se presenta en forma

de DIMMs de 168 contactos.

PC100 (SDRAM de 100 MHz): Memoria SDRAM que funciona a 100 MHz, que utilizan

los micros más modernos.

Según los tipos de conectores que lleve la memoria, al conjunto de éstos se les denominan

módulos, y éstos a su vez se dividen en:

SIMM (Single In-line Memory Module): Pequeña placa de circuito impreso con varios

chips de memoria integrados. Se fabrican con diferentes velocidades de acceso

capacidades (4, 8, 16, 32, 64 Mb) y son de 30 ó 72 contactos. Se montan por pares

generalmente.

DIMM: Son más alargados, cuentan con 168 contactos y llevan dos muescas para

facilitar su correcta colocación. Pueden montarse de 1 en 1.

Tipos de memoria RAM.

La memoria RAM del ordenador suele ser la más abundante del sistema, ya que permite

la grabación y posterior recuperación de la información contenida en la misma.

Podemos dividir la memoria RAM en función del modo en el que trabaja: memoria

RAM estática (SRAM: Static RAM) y memoria RAM dinámica (DRAM: Dynamic

RAM). Ambos tipos de memoria almacenan los datos utilizando cargas eléctricas. Se

diferencian en que utilizan métodos distintos para almacenarlos.

La memoria SRAM suele estar basada en transistores de tecnología MOS

(Semiconductor de Oxido-Metal), que permiten el almacenamiento de una alta densidad

de información. En este tipo de memoria la información se almacena en una red de

osciladores biestables, es decir, osciladores que sólo permiten dos estados: cero o uno.

La principal característica de las memorias RAM estáticas radica en que una vez

introducida la información, ésta se mantiene dentro de la memoria hasta que se

desconecte la fuente de alimentación.

Las memorias DRAM, por el contrario, almacenan la información en forma de una

carga eléctrica en un condensador, el cual sólo puede almacenar una pequeña cantidad

de carga que, unido a las inevitables fugas, provoca que la información se pierda a los

pocos milisegundos. Para evitar el citado inconveniente, este tipo de memorias, que por

otro lado son las más extendidas por ser las más económicas y por ser las que mayor

densidad de información permiten, necesitan que se les refresque la información cada

cierto tiempo.

Hay que destacar que mientras la SRAM necesita un mínimo de siete transistores por

cada bit de información, la memoria DRAM solamente necesita un transistor MOSFET

y un condensador para la celda. El pequeño condensador, que se debe recargar o

refrescar miles de veces por segundo, necesita de una circuitería adicional bastante

compleja para sostener la información. Pero esta complejidad se ve compensada por lo

reducido del tamaño y del coste de cada celda de memoria.

En general, se emplea la DRAM como el sistema principal de almacenamiento de

código y de datos, ya que es la más barata de fabricar. La SRAM se utiliza cuando sólo

se necesitan pequeñas cantidades de memoria, tal como en el caso de las memorias

cachés.

La memoria caché es un tipo de memoria de acceso aleatorio especialmente rápida que

suele estar localizada, incluso, dentro del propio microprocesador. Suele ser de pequeño

tamaño y almacena la información manejada con mayor frecuencia por la CPU. Los

nuevos procesadores Pentium cuentan con dos memorias cachés independientes, una

para datos y otra para códigos.

A continuación se describen brevemente las tecnologías de DRAM existentes en la

actualidad:

EDO (Extended Data Output). Incorpora varias innovaciones que permiten

acelerar hasta un 15% la velocidad de acceso a memoria.

SDRAM (DRAM Síncrona). Emplea una señal de reloj, sincronizada con la

señal de reloj de la CPU, para coordinar las transferencias. Consigue superar la

velocidad de la memoria EDO en un 25%.

DDR (Double Data Rate) o SDRAM II. Segunda generación de las memorias

SDRAM. Aprovecha tanto el estado alto como el bajo de la señal de reloj para

sincronizar las transferencias. Consigue duplicar la velocidad de transferencia

sin modificar la frecuencia del reloj (es decir, con la misma CPU).

RDRAM (Rambus DRAM). Esta tecnología consigue multiplicar por 10 la

velocidad de transferencia de una DRAM estándar, gracias a una tecnología

exclusiva denominada RSL (Rambus Signaling Logic).

SLDRAM (synclink). Tecnología desarrollada por un consorcio de doce

compañías. Es una extensión de la SDRAM, que permite ampliar el número de

bancos de 4 a 16.

Por supuesto, para aprovechar una de estas tecnologías, el PC debe estar preparado para

ello. Valgan como ejemplo los procesadores Pentium 4, que por medio de un acuerdo

entre Rambus e Intel, vienen preparados para emplear RDRAM.

http://aib.umh.es/1_InTroduccion_Informatica/tema2/ElPCpordentro.htm

3.2.2.3

Características.

Características de la Memoria:

El tiempo de almacenamiento: (volátil o no).

Velocidad de acceso en operaciones de lectura / escritura.

Capacidad de almacenamiento.

Sin embargo: A mas velocidad mayor costeSOLUCIÓNUtilizar distintos tipos de memoria

organizada de forma jerárquica.

Tipos:

Memorias de solo lectura ROM: PROM y EPROM

Memorias de lectura / escritura RAM: SDRAM y DRAM

Memorias Magnéticas / ópticas: Discos duros, CDROM, DVD

Jerarquía de memoria, Niveles:

NIVEL 0 Cache +VELOCIDAD

NIVEL 1 Ram/Rom ……..……………….

NIVEL 2 Magnético / óptico +CAPACIDAD

un sistema de memoria se puede clasificar en función de muy diversas características.

Entre ellas se pueden destacar las siguientes: localización de la memoria, capacidad,

método de acceso y velocidad de acceso. En el caso de la memoria RAM, también

denominada memoria principal o primaria, los valores de estas características son:

Localización: interna, se encuentra en la placa base.

Capacidad: hoy en día no es raro encontrar PC equipados con 128 o 256 MB de

memoria RAM.

Método de acceso: memoria de acceso aleatorio. Además, permite el acceso para

lectura y escritura de información.

Velocidad de acceso: actualmente se pueden encontrar sistemas de memoria

RAM capaces de realizar transferencias a frecuencias del orden de los Gbps

(gigabits por segundo).

También es importante anotar que la RAM es una memoria volátil y por tanto requiere

de alimentación eléctrica para mantener la información.

Características

Tienen matriz: Lugar físico en el que se almacena información. Un punto es el

lugar físico donde se almacena un bit. 8 puntos es una celda Byte.

Cada celda tiene asociada una dirección, que indica la ubicación física de la

celda.

Capacidad: número de bytes que puede almacenar.

Tiempo de acceso: El tiempo que transcurre desde que el P solicita un dato y

la memoria se lo entrega (en ns).

CARACTERISTICAS DE LA MEMORIA

CAPACIDAD

Cantidad de información que puede almacenar en una memoria en concreto. Hay dos tipos:

*Util: LA que puede almacenar el usuario.

*Bruta: Número total de unidades de información (bits ó bytes) que pueden ser

almacenadas en un dispositivo.

VELOCIDAD

Indica el tiempo desde que se solicita un dato hasta que se recibe. Dos grupos:

* De acceso aleatorio: Si se tarde lo mismo independientemente de la situación del dato.

De acceso no aleatorio: Influye el tiempo de búsqueda y el de latencia.

DURACION DE LA INFORMACION

Capacidad de retener la información a lo largo del tiempo. Tiene que ver con la permanencia ó

no del suministro de energía eléctrica.

*Volátiles: Pierden su contenido sin electricidad. Están basadas en semiconductores.

*No volátiles: Permanentes.

COSTES

Se divide en precio/unidad de información y depende fuertemente de forma antagónica con la

velocidad de acceso.

Precio T.acceso Coste

Registros 20000 pts/MB 10 ns

RAM 5000 pts/MB 70 ns

Disco duro 100 pts/MB 10 ms

Disquetes 50 pts/MB 2 s

Cintas Streamer 10 pts/MB 20 s

Papel digital 0,01 pts/MB 2 min. Tiempo

MODO DE ACCESO

Se refiere a como se indica la dirección de la posición de memoria a la que se quiere acceder y

como se organiza la información en el interior de la memoria.

JERARQUIAS DE MEMORIA

Lo que interesa es utilizar memorias rápidas, pero son muy costosas, por lo que se utilizan

dispositivos caros(rápidos) para los que operan en la CPU y dispositivos baratos(lentos) pero

con mayor capacidad de almacenar información que no se procesa en ese momento

determinado.

ns REGISTRO En la CPU

decenas de ns MEMORIA CACHE

MEMORIA PRINCIPAL Placa base

de ms a seg. MEMORIA SECUNDARIA Fuera del ordenador

3.2.2.4

Funcionamiento.

Función

Formada por condensadores, que continuamente se están cargando y descargando, hacen

posible almacenar los ceros y unos (ausencia y presencia de corriente respectivamente), el

tiempo que tarden a volverse a cargar una vez se descargan recibe el nombre de tiempo de

refresco; también hay otro tiempo establecido, es el tiempo de acceso.

La memoria de trabajo (normalmente compuesta de chips RAM), hace de cajón o caja al

microprocesador dónde guarda los datos que necesita para operar con ellos, así sí la CPU

necesita algún dato, el disco duro la busca, y este lo envía a la memoria de trabajo, y éste va

a la CPU cuando se la pide. Así pues vemos que es una memoria temporal, puesto que

además, al apagar el PC se pierde toda la información que hay.

http://www.hardware12v.com/conocimientospc/5.php

Funciones que realiza

La memoria de un computador se puede definir como los circuitos que permiten

almacenar y recuperar la información. En un sentido más amplio, puede referirse

también a sistemas externos de almacenamiento, como las unidades de disco o de cinta.

Hoy en día se requiere cada vez más memoria para poder utilizar complejos programas

y para gestionar complejas redes de computadores.

3.2.3 Dispositivos de I/O.

Las unidades de E/S constan de dos elementos:

MECÁNICO: denominado “DISPOSITIVO DE E/S”.

ELECTRÓNICO: denominado “CONTROLADORES”.

Los dispositivos de E/S que se conectan al ordenador se clasifican en:

BLOQUE: La información se almacena en bloques, esos bloques son de

tamaño fijo. Donde cada bloque tiene una dirección que lo identifica. Se

puede leer o escribir en un bloque independiente de los demás.

Por ejemplo: disquete, CD, DVD, disco duro.

CARÁCTER: La información que se generan o reciben son flujos de

caracteres (no bloques). Accede a los datos en secuencia: o sea, para

acceder a determinados datos, la lectura y escritura se debe hacer

seguido de los datos anteriores.

Por ejemplo: teclado, pantalla, cinta, ratones, interfaz de

comunicación.

La línea de separación no es rígida, hay dispositivos que pueden ser

del tipo bloque (cintas Magnéticas) aunque son considerados del tipo carácter.

Con esta clasificación, un dispositivo que está fuera de ellas, el

“RELOJ”, no es orientado ni a bloque ni de carácter. Si es un dispositivo

especial, ya que lo único que hace es generar interrupciones.

Otros aspectos importantes que hacen la diferencia entre dispositivos

son:

Comportamiento: entrada, salida, almacenamiento.

Tasa de transferencia: tasa de peak de transferencia entre

dispositivos y memoria.

El siguiente cuadro hace referencia, a las grandes diferencias entre las

clases de dispositivos:

DISPOSITIVO

TECLADO

MOUSE

SCANNER

VOS (Salida)

IMPRESORA

COMPORTAMIENTO

Entrada

"

"

Salida

"

CLASIFICACION

Carácter

"

"

"

"

TASA KB/SEG.

0,01

0,02

400

0,6

1,0

(Línea)

IMPRESORA

(Láser)

MODEM

RED LAN

FLOPPY

CD

CINTA

MAGNETICA

DISCO

MAGNETICO

"

"

200

Entrada / salida

"

Almacenamiento

"

"

"

"

Bloque

"

"

2,0-8,0

500-6000

100

1000

2000

"

"

2000-10000

Existen otros factores que hacen a su distinción:

UNIDADES DE CONTROL

REPRESENTACIÓN DE DATOS

CONDICIÓN DE ERROR

http://exa.unne.edu.ar/depar/areas/informatica/SistemasOperativos/MonogSO/

GESTES02.htm

Principios del Software de E / S

La idea básica es organizar el software como una serie de capas donde [23,

Tanenbaum]:

Las capas inferiores se encarguen de ocultar las peculiaridades del hardware a

las capas superiores.

Las capas superiores deben presentar una interfaz agradable, limpia y regular a

los usuarios.

Objetivos del Software de E / S

Un concepto clave es la independencia del dispositivo:

Debe ser posible escribir programas que se puedan utilizar con archivos en

distintos dispositivos, sin tener que modificar los programas para cada tipo de

dispositivo.

El problema debe ser resuelto por el S. O.

El objetivo de lograr nombres uniformes está muy relacionado con el de independencia

del dispositivo.

Todos los archivos y dispositivos adquieren direcciones de la misma forma, es decir

mediante el nombre de su ruta de acceso.

Otro aspecto importante del software es el manejo de errores de e / s: