Digital II – Primer parcial (2 fecha) – 12/10/2013

Anuncio

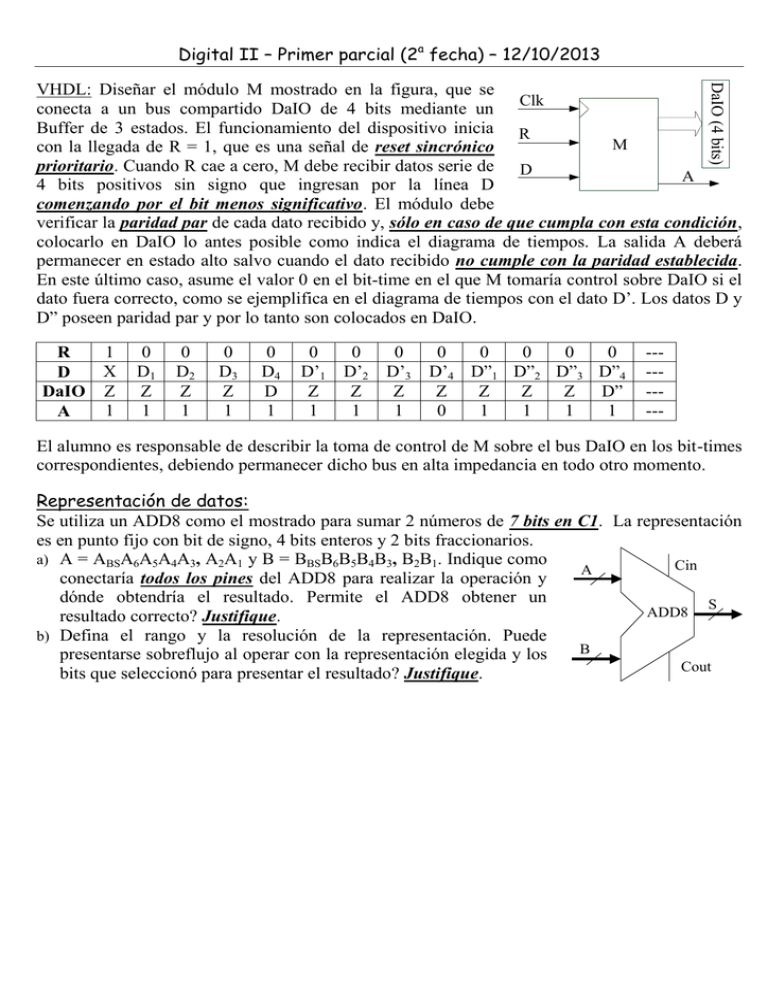

Digital II – Primer parcial (2a fecha) – 12/10/2013 DaIO (4 bits) VHDL: Diseñar el módulo M mostrado en la figura, que se Clk conecta a un bus compartido DaIO de 4 bits mediante un Buffer de 3 estados. El funcionamiento del dispositivo inicia R M con la llegada de R = 1, que es una señal de reset sincrónico prioritario. Cuando R cae a cero, M debe recibir datos serie de D A 4 bits positivos sin signo que ingresan por la línea D comenzando por el bit menos significativo. El módulo debe verificar la paridad par de cada dato recibido y, sólo en caso de que cumpla con esta condición, colocarlo en DaIO lo antes posible como indica el diagrama de tiempos. La salida A deberá permanecer en estado alto salvo cuando el dato recibido no cumple con la paridad establecida. En este último caso, asume el valor 0 en el bit-time en el que M tomaría control sobre DaIO si el dato fuera correcto, como se ejemplifica en el diagrama de tiempos con el dato D’. Los datos D y D” poseen paridad par y por lo tanto son colocados en DaIO. 1 R X D DaIO Z 1 A 0 D1 Z 1 0 D2 Z 1 0 D3 Z 1 0 D4 D 1 0 0 0 0 0 0 0 0 D’1 D’2 D’3 D’4 D”1 D”2 D”3 D”4 Z Z Z Z Z Z Z D” 1 1 1 0 1 1 1 1 --------- El alumno es responsable de describir la toma de control de M sobre el bus DaIO en los bit-times correspondientes, debiendo permanecer dicho bus en alta impedancia en todo otro momento. Representación de datos: Se utiliza un ADD8 como el mostrado para sumar 2 números de 7 bits en C1. La representación es en punto fijo con bit de signo, 4 bits enteros y 2 bits fraccionarios. a) A = ABSA6A5A4A3, A2A1 y B = BBSB6B5B4B3, B2B1. Indique como Cin A conectaría todos los pines del ADD8 para realizar la operación y dónde obtendría el resultado. Permite el ADD8 obtener un S ADD8 resultado correcto? Justifique. b) Defina el rango y la resolución de la representación. Puede B presentarse sobreflujo al operar con la representación elegida y los Cout bits que seleccionó para presentar el resultado? Justifique.