Arquitecturas RISC versus CISC

Anuncio

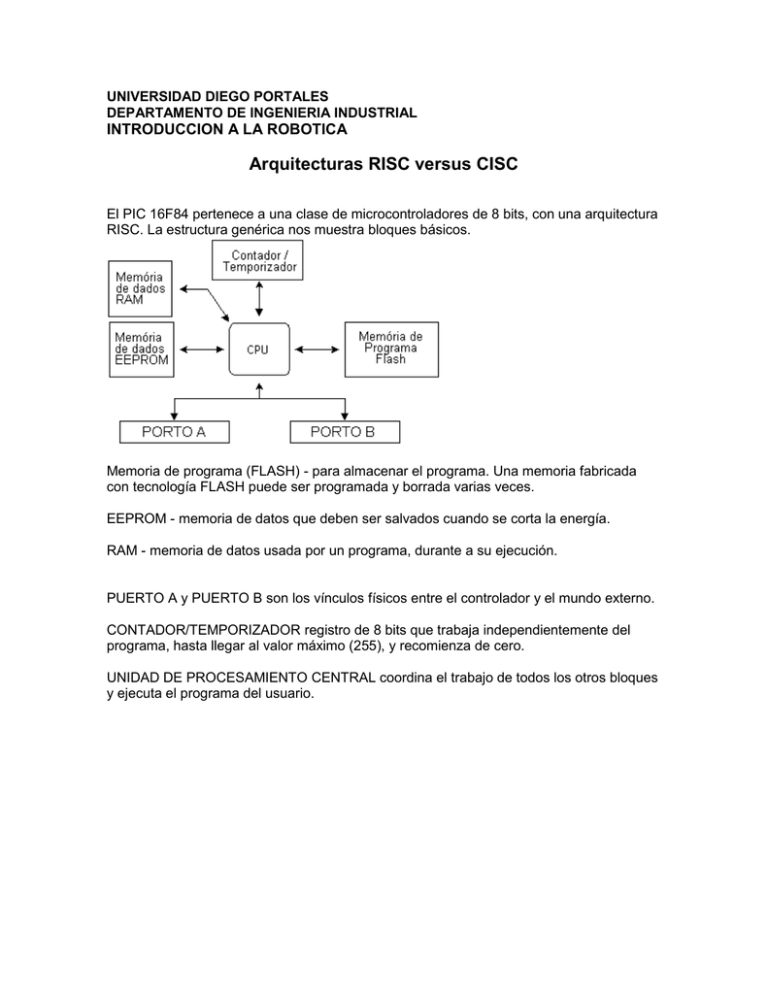

UNIVERSIDAD DIEGO PORTALES DEPARTAMENTO DE INGENIERIA INDUSTRIAL INTRODUCCION A LA ROBOTICA Arquitecturas RISC versus CISC El PIC 16F84 pertenece a una clase de microcontroladores de 8 bits, con una arquitectura RISC. La estructura genérica nos muestra bloques básicos. Memoria de programa (FLASH) - para almacenar el programa. Una memoria fabricada con tecnología FLASH puede ser programada y borrada varias veces. EEPROM - memoria de datos que deben ser salvados cuando se corta la energía. RAM - memoria de datos usada por un programa, durante a su ejecución. PUERTO A y PUERTO B son los vínculos físicos entre el controlador y el mundo externo. CONTADOR/TEMPORIZADOR registro de 8 bits que trabaja independientemente del programa, hasta llegar al valor máximo (255), y recomienza de cero. UNIDAD DE PROCESAMIENTO CENTRAL coordina el trabajo de todos los otros bloques y ejecuta el programa del usuario. Esquema do microcontrolador PIC16F84 Arquitecturas Harvard versus von Neumann CISC, RISC La arquitectura Harvard o RISC se desarrollo por la necesidad de trabajar más rápidamente. En esta arquitectura la memoria de datos esta SEPARADA de la memoria del programa. Así se logra un flujo de datos mas elevado por la CPU. El PIC 16F84 usa palabras de 14 bits para cada instrucción, y las instrucciones ocupan sólo una palabra. Es típico de la arquitectura RISC tener un repertorio de menos instrucciones que el CISC y esas instrucciones se ejecutan (generalmente) en un ciclo de reloj. RISC = REDUCED INSTRUCTION SET COMPUTER CISC = COMPLEX INSTRUCTION SET COMPUTER = HARVARD = VON NEUMANN El microcontrolador PIC16F84 posee 35 instrucciones que se ejecutan en un unico ciclo, excepto en las instrucciones de salto y ramificación. Reloj / ciclo de instrucción El reloj da la señal de partida para el microcontrolador y se obtiene del oscilador (externo). La señal de entrada (OSC1) es dividida en 4 fases Q1, Q2, Q3 e Q4 no sobrepuestas. Estos cuatro pulsos constituyen un ciclo de instrucción (Tb. llamado de máquina), durante el cual se ejecuta una instrucción. La ejecución de una instrucción sigue una secuencia muy precisa de eventos, incluyendo lectura de la instrucción de la memoria (para saber de donde extraer la instrucción se usa el PC, que contiene la dirección de la siguiente instrucción a ser ejecutada) La decodificación y ejecución de la instrucción se realiza dentro del período Q1 a Q4 siguiente a la lectura. Pipelining La extracción del código de una instrucción de la memoria de programa se realiza en un ciclo de instrucción y su decodificación y ejecución se realiza en el ciclo de instrucción siguiente. Debido a la superposición, ya que el microcontrolador al tiempo que extrae el código de la instrucción siguiente ejecuta la instrucción extraída previamente, es que se puede considerar que cada instrucción demora un ciclo de instrucción en ser ejecutada. Este pipeline se rompe para el caso de las instrucciones que involucren saltos en la secuencia (incluyendo loas llamadas a subrutinas), las cuales se deben considerar como de dos ciclos de duración. Flujograma de las instrucciones del Pipeline TCY0: se lee de memoria el código de la instrucción MOVLW 55h (no nos interesa la instrucción que está siendo ejecutada). TCY1: se ejecuta MOVLW 55h y se lee de memoria la instrucción MOVWF PORTB. TCY2: se ejecuta MOVWF PORTB y se lee la instrucción CALL SUB_1. TCY3: se ejecuta la llamada (call) CALL SUB_1 y se lee la instrucción BSF PORTA,BIT3. Como no es esta la instrucción que nos interesa en este momento, porque no es la primera instrucción de la subrutina, la lectura de una instrucción debe efectuarse de nuevo. TCY4: este ciclo de instrucción es ocupado totalmente para leer la primera instrucción del subprograma (en la dirección asociada a SUB_1). TCY5: se ejecuta la primera instrucción de la subrutina SUB_1 y se lee la instrucción siguiente.