UNIDAD III Electrónica Digital

Anuncio

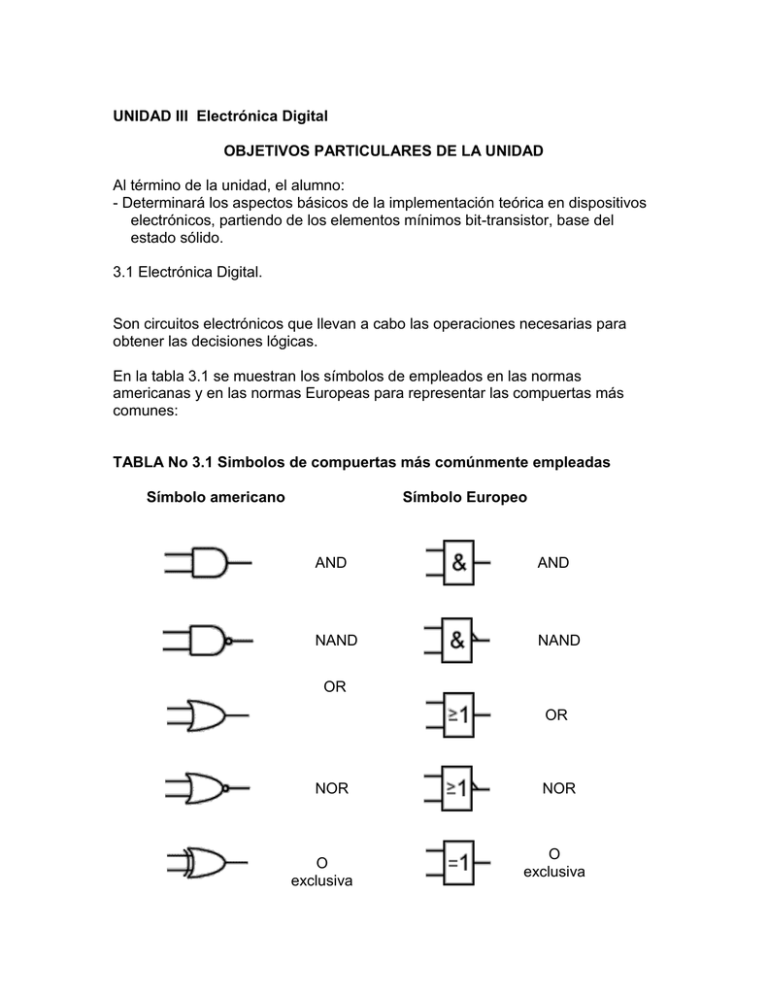

UNIDAD III Electrónica Digital OBJETIVOS PARTICULARES DE LA UNIDAD Al término de la unidad, el alumno: - Determinará los aspectos básicos de la implementación teórica en dispositivos electrónicos, partiendo de los elementos mínimos bit-transistor, base del estado sólido. 3.1 Electrónica Digital. Son circuitos electrónicos que llevan a cabo las operaciones necesarias para obtener las decisiones lógicas. En la tabla 3.1 se muestran los símbolos de empleados en las normas americanas y en las normas Europeas para representar las compuertas más comunes: TABLA No 3.1 Simbolos de compuertas más comúnmente empleadas Símbolo americano Símbolo Europeo AND AND NAND NAND OR OR NOR O exclusiva NOR O exclusiva Y exclusiva Realiza funciones de AND y NAND Inversor Diferencial Puerta triestado Realiza funciones de OR y NOR Inversor Inversor schmitt Buffer Buffer triestado Buffer negado Driver 3.2 Circuitos combinacionales. Circuito combinacional Un circuito combinacional es un circuito cuya salida es función exclusivamente del estado del valor lógico de sus entradas. Está compuesto por compuertas lógicas y no deben presenta realimentación, es decir, ninguna salida de ningún componente debe usarse como entrada del circuito. Se diseña atendiendo a las reglas de lógica combinacional. Un circuito combinacional puede describirse utilizando una fórmula con álgebra de Boole en la que las salidas sean dependientes solamente de las entradas. Existen muchos circuitos combinacionales típicos. Algunos de ellos son: Codificadores: Convierten una señal binaria en otra señal binaria de distintas características. Multiplexores y Demultiplexores: Seleccionan una salida entre varias señales de entrada o al contrario, de una señal de entrada se obtienen varias salidas. Comparadores: comparan 2 números en código binario. Unidades aritméticas: suman, restan, multiplican, números binarios. En los siguientes apartados se presentan estos circuitos con mayor detalle 3.2.1 Familias de circuitos lógicos. Familia TTL (Lógica de Transistor - Transistor) Esta fue la primera familia de éxito comercial, se utilizó entre 1965 y 1985. Los circuitos TTL utilizan transistores bipolares y algunas resistencias de polarización. La tensión nominal de alimentación de los circuitos TTL son 5 V DC. Niveles Lógicos TTL En el estudio de los circuitos lógicos, existen cuatro especificaciones lógicos diferentes: VIL, VIH, VOL y VOH. En los circuitos TTL, VIL es la tensión de entrada válida para el rango 0 a 0.8 V que representa un nivel lógico 0 (BAJO). El rango de tensión VIH representa la tensiones válidas de un 1 lógico entre 2 y 5 V. El rango de valores 0.8 a 2 V determinan un funcionamiento no predecible, por la tanto estos valores no son permitidos. El rango de tensiones de salida VOL, VOH se muestra en la figura Figura 3.1Nivel lógico de entrada de un circuito TTL Circuitos Lógicos CMOS (Metal Óxido Semiconductor Complementario) La tecnología CMOS es la más utilizada actualmente para la construcción de circuitos integrados digitales, como las compuertas, hasta los circuitos como las memorias y los microprocesadores. La tensión nominal de alimentación de los circuitos CMOS son +5 V y +3,3 V. Niveles Lógicos CMOS En la figura 3.2 se muestran las tensiones VIL, VIH, VOL, VOH válidas para los dispositivos CMOS de nivel +5 VDC. figura 3.2 Nivel Lógico de Entrada de un circuito CMOS +5 V Familias lógicas Los circuitos digitales emplean componentes encapsulados, los cuales pueden albergar puertas lógicas o circuitos lógicos más complejos. Estos componentes están estandarizados, para que haya una compatibilidad entre fabricantes, de forma que las características más importantes sean comunes. De forma global los componentes lógicos se engloban dentro de una de las dos familias siguientes: TTL: diseñada para una alta velocidad. CMOS: diseñada para un bajo consumo. Actualmente dentro de estas dos familias se han creado otras, que intentan conseguir lo mejor de ambas: un bajo consumo y una alta velocidad. Tabla 3.2 Comparación de las familias TTL Schottky de baja potencia (LS) Fairchild 4000B CMOS (con Vcc=5V) Fairchild 4000B CMOS (con Vcc=10V) 5 ns 40 ns 20 ns PARAMETRO TTL TTL estándar 74L Tiempo de propagación 10 ns 33 ns Frecuencia máxima de funcionamiento 35 MHz 3 45 MHz MHz 8 MHz 16 MHz Potencia disipada 10 mW 1 mW 2 mW 10 nW 10 nW Margen de ruido admisible 1V 1V 0'8 V 2V 4V Fan out 10 10 20 50 (*) 50 (*) (*) O lo que permita el tiempo de propagación admisible Dentro de la familia TTL encontramos las siguiente sub-familias: L: Low power = disipación de potencia muy baja LS: Low power Schottky = disipación y tiempo de propagación pequeño. S: Schottky = disipación normal y tiempo de propagación pequeño. AS: Advanced Schottky = disipación normal y tiempo de propagación extremadamente pequeño. TENSION DE ALIMENTACION CMOS: 5 a 15 V (dependiendo de la tensión tendremos un tiempo de propagación). TTL: 5 V. Parámetros de compuerta Las compuertas lógicas no son dispositivos ideales, por lo que vamos a tener una serie de limitaciones impuestas por el propio diseño interno de los dispositivos lógicos. Internamente la familia TTL emplea transistores bipolares , por lo que tienen mayor consumo de potencia, mientras que la familia CMOS emplea transistores MOS por lo que presentan bajo consumo de potencia). MARGEN DEL CERO Es el rango de tensiones de entrada en que se considera un cero lógico: VIL máx: tensión máxima que se admite como cero lógico. VIL mín: tensión mínima que se admite como cero lógico. MARGEN DEL UNO Es el rango de tensiones de entrada en que se considera un uno lógico: VIH máx: tensión máxima que se admite como uno lógico. VIH mín: tensión mínima que se admite como uno lógico. MARGEN DE TRANSICION Se corresponde con el rango de tensiones en que la entrada es indeterminada y puede ser tomada como un uno o un cero. Esta zona no debe ser empleada nunca, ya que la puerta se comporta de forma incorrecta. MT = VIH mín - VIL máx AMPLITUD LOGICA Debido a que dos puertas de la misma familia no suelen tener las mismas características debemos emplear los valores extremos que tengamos, utilizando el valor de VIL máx más bajo y el valor de VIH mín más alto. AL máx: VH máx - VL mín AL mín: VH mín - VL máx RUIDO El ruido es el elemento más común que puede hacer que nuestro circuito no funcione habiendo sido diseñado perfectamente. El ruido puede ser inherente al propio circuito (como consecuencia de proximidad entre pistas o capacidades internas) o también como consecuencia de ruido exterior (el propio de un ambiente industrial). Si trabajamos muy cerca de los límites impuestos por VIH y VIL puede que el ruido impida el correcto funcionamiento del circuito. Por ello debemos trabajar teniendo en cuenta un margen de ruido: VMH (margen de ruido a nivel alto) = VOH mín - VIH mín VML (margen de ruido a nivel bajo) = VIL máx - VOL máx VOH y VOL son los niveles de tensión del uno y el cero respectivamente para la salida de la puerta lógica. Supongamos que trabajamos a un nivel bajo de VOL = 0'4 V con VIL máx = 0'8 V. En estas condiciones tendremos un margen de ruido para nivel bajo de: VML = 0'8 - 0'4 = 0'4 V FAN OUT Es el máximo número de puertas que podemos excitar sin salirnos de los márgenes garantizados por el fabricante. Nos asegura que en la entrada de las puertas excitadas: VOH es mayor que VOH mín VOL es menor que VOL mín Para el caso en que el FAN OUT sea diferente a nivel bajo y a nivel alto, escogeremos el FAN OUT más bajo para nuestros diseños. Si además nos encontramos con que el fabricante no nos proporciona el FAN OUT podemos calcularlo como: FAN OUT = IOL máx / IIL máx Donde IOL e IIL son las corrientes de salida y entrada mínimas de puerta. POTENCIA DISIPADA Es la media de potencia disipada a nivel alto y bajo. Se traduce en la potencia media que la puerta va a consumir. TIEMPOS DE PROPAGACION Definimos como tiempo de propagación el tiempo transcurrido desde que la señal de entrada pasa por un determinado valor hasta que la salida reacciona a dicho valor. vamos a tener dos tiempos de propagación: Tphl = tiempo de paso de nivel alto a bajo. Tplh = tiempo de paso de nivel bajo a alto. Como norma se suele emplear el tiempo medio de propagación, que se calcula como: Tpd = (Tphl + Tplh)/2 FRECUENCIA MAXIMA DE FUNCIONAMIENTO Se define como: Fmáx = 1 / (4 * Tpd) 3.2.2 Conmutadores lógicos. Los conmutadores lógicos o más comúnmente llamados compuertas lógicas son dispositivos o circuitos electrónicos que permiten implementar las operaciones lógicas AND, OR Y NOT. En lo general con base a estos circuitos simples se construyen todas las compuertas que existen en el mercado y cuyos símbolos se muestran en la tabla 2. En teoría se pueden construir cualquier circuito lógico solamente con estas tres compuertas, obviamente dependiendo de la complejidad del circuito a implementar, puede resultar prácticamente incosteable hacerlo solo con estas compuertas por el tamaño y gran posibilidad de fallas. La tecnología actual permite que en un solo circuito integrado fabricar una gran cantidad de compuertas, que por el número de ellas se les conocen como de baja (SSI), media (MSI) y alta (LSI) integracion 3.2.3 Integración de compuertas. Los circuitos para las compuertas lógicas actualmente se fabrican para realizar desde funciones lógicas básicas AND, OR, NOT (SSI) , hasta aplicaciones muy complejas, (LSI) como son los dispositivos de lógica programable, memorias, microprocesadores, pasando por circuitos con funciones lógicas especificas (MSI) como son codificadores, decodificadores , multiplexores, demultiplexores, contadores, etc. 3.2.4 Codificadores y decodificadores Codificador En general, se puede decir que un codificador es un circuito hecho para pasar información de un sistema a otro con clave diferente, . En otras palabras, es un circuito integrado por un conjunto de componentes electrónicos con la habilidad para mostrar en sus terminales de salida una palabra binaria ( word binario 01101, 1100, etc.), equivalente al número presente en sus entradas, pero escrito en un código diferente. Por ejemplo, un codificador de Octal a Binario es un circuito codificador con ocho entradas (un terminal para cada dígito Octal, o de base 8) y tres salidas (un terminal para cada bit binario). Otro ejemplo es el codificador de teclado (Keyword encoder) que convierte la posición de cada tecla (9, 3, . 5, + , %, etc.) en su correspondiente palabra binaria (word) asignada previamente. Un ejemplo de lo anterior es el teclado codificador en ASCII (American Standard Code for Information Interchange), que genera lapalabra de 7 bits 0100101 cuando es presionada la tecla del porcentaje (%). Decodificador El decodificador es un circuito combinacional diseñado para convertir un número binario a un orden distinto, para ejecutar un trabajo especial. Esto es , la palabra binaria que sale, tiene un formato diferente, a la palabra que entró, aunque tenga la misma cantidad de bits. Ejemplo 34 El circuito lógico que convierte una entrada en código binario BCD a decimal Figura ejemplo 35 decodificador BCD a decimal En Electrónica Digital es a menudo necesario pasar un número binario a otro formato, tal como el requerido para energizar los siete segmentos de los “display” hechos con diodos emisores de luz, en el orden adecuado para que se ilumine la figura de un número decimal en particular.. Ejemplo. 36 El circuito que convierte una entrada en codigo BCD a un formato de salida para manejar un display de 7 segmentos se muestra en su tabla de verdad y esquema de la compuerta 74HC42. Figura ejemplo 36.- Decodificador BCD a 7 segmentos Los decodificadores son también usados en los microprocesadores para convertir instrucciones binarias en señales de tiempo, para controlar máquinas en procesos industriales o implementar circuitos lógicos avanzados 3.2.5 Multiplexores y demultiplexores. Multiplexor El multiplexor es el equivalente lógico digital de un interruptor giratorio de varias posiciones, tal como la llave que sirve para seleccionar las bandas de un receptor de radio. Un multiplexor típico en circuitos integrados es aquel que puede seleccionar cualquiera de varias líneas de entrada y comunicar a una línea común de salida el nivel lógico que allí encuentre. Mediante unas líneas auxiliares de control binario se le puede "direccionar" para que se "estacione" en determinada línea de entrada de datos (la primera, la quinta, séptima, etc.) con el fin de que aquellos sean comunicados a la línea de salida. Un integrado multiplexor común tiene 8 entradas de datos (bits), tres entradas direccionadas (address) y una sola línea para salida de datos. Cuando la dirección 101 -leer "uno- cero - uno" - es aplicada al multiplexor, la entrada 5 es "comunicada" con la salida. Una aplicación muy importante es la facilidad de implementar una función lógica usando un multiplexo. Ejemplo 36 a Implementar la función lógica Q = x’y’z +x’yz’+xyz’+xyz usando un circuito multiplexor. SOLUCION Q (xyz) = x’y’z +x’yz’+xyz’+xyz = ∑(1,2,6,7) Se emplea un multiplexor de 4 a 1 es decir 4 entradas (E0, E1, E2, E3) a una salida F, este circuito tiene entonces dos lineas de entrada de control S0 y S1 Conviene tener en cuenta que el circuito funciona de la siguiente manera: si la entradas S0 y S1 son 0 0 a la salida estará el valor de la entrada E0, de igual forma si S0 y S1 están con el valor 0 1 a la salida tendremos E1, y asi sucesivamente. Procedemos de la siguiente forma Las dos primeras dos variables x, y se aplican a las lineas de control en ese orden, x a entrada S1, y y a entrada S0. Los valores de las lineas de entrada E0, a E3 se deducen de la tabla de verdad de la función.(Ver figura 36 a de tabla de verdad) Cuando A B valen 0 0 a la salida deberá estar el valor F igual a E 0=0, por lo tanto a la entrada E0 pondremos el valor lógico de z. cuando A B valen 0 1 a la salida deberá estar el valor F igual a E1=z’, por lo tanto a la entrada E1 conectamos el valor de z’. cuando A B valen 1 0 el valor de F deberá ser 0 por lo que conectamos en E2, el valor lógico de 0 y finalmente si A B valen 11, F sera tanbien igual a 1 , por lo que nuevamente conectamos 1 a la entrada E 3 .Con esto ya se tiene el circuito que se muestra en la figura ejemplo 36 implementacion con multiplexor. Con este ejemplo se muestra la ventaja de que una función lógica de tres variables se puede implementar con una sola compuerta multiplexora y una compuerta inversora sin necesidad de reducir el circuito. En general se puede implementar cualquier función de n variables con un multiplexor de n-1 entradas de selección y 2n-1 entradas de datos. Ejemplo 36b Implementar con multiplexor la función F(ABCD) = ∑(1,3,4,11,12,13,14,15) Solucion. Se tiene una función con n = 4 variables, por tanto se requiere un multiplexor de 8 X 1, ocho entradas de datos por una salida, el cual tendrá 3 entradas de control A las entradas de control S2, S1, S0 les asignamos, el valor A,B,C respectivamente, y a las 8 entradas (E0, E1, E2, E3 ,E4, E5, E6, E7) los que se deducen de los valores que se muestran en la tabla de verdad de la figura ejemplo 36b. Figura del ejemplo 36b Implementacion de una función de 4 variables F(ABCD) = ∑(1,3,4,11,12,13,14,15) Aprovechando el fenómeno conocido como "persistencia visual", se emplean con mucha frecuencia circuitos multiplexor en el manejo de los visualizadores numéricos de las calculadoras y relojes electrónicos portátiles, ya que así se logra disminuir el consumo de corriente y la cantidad de pines (patas) que deberían llegar hasta el circuito activador. Por ejemplo, un display estático de 3 dígitos LED de 7 segmentos, tiene en total 24 pines (8 por cada dígito) y un consumo de corriente igual a la suma de lo gastado por cada segmento activado. En el mismo caso, un display dinámico (multiplexado) tiene solamente 10 pines (7 líneas que unen en paralelo los correspondientes segmentos en cada dígito, y 3 líneas de salida individual por dígito (el cátodo o el ánodo común, según sea la polaridad del display). El consumo total de corriente para iluminar digamos el 888 sería aproximadamente igual al gastado por un sólo dígito en la forma estática. Debido a la "persistencia visual" en nuestros ojos, es posible multiplexor los tres dígitos del display para que enciendan y apaguen sucesivamente en forma escalonada, sin que notemos parpadeo y dé la sensación de estar continuamente iluminados. Primero uno, luego el otro, y así sucesivamente hasta que le toca repetir al que inició el ciclo; a las veces que les toca repetir su encendido por cada segundo de tiempo, se les denomina RATA DE REPETICION o cantidad de CUADROS. Igual que en televisión, la rata no debe ser menor a 30 cuadros por segundo, pero se permite aumentar esta cifra hasta donde lo permitan los tiempos de propagación de las compuertas empleadas en la integración del multiplexor. Demultiplexor El demultiplexor funciona de manera contraria al multiplexor: tiene una sola línea para entrada de datos y dos o más salidas seleccionables. Tal como ocurre con el multiplexor, un conjunto de terminales de entrada conocidos como "address" direcciona o escoge la salida. El address necesita una cantidad de terminales suficientes para recibir la cantidad de bits que conforman el número binario equivalente al máximo de salidas. Así, por ejemplo, un demultiplexor de 1 línea a 8 líneas, requiere tres bits para poder "llevar" la entrada hasta la salida octava (address 111 es el número binario equivalente al decimal 7, pero corresponde a la posición octava por tener en cuenta que el 000 es la posición primera). Los dDeMUX se utilizan también como decodificadores de binario a un solo nivel de salida, tal como los decodificadores BINARIO a DECIMAL, o BINARIO a HEXADECIMAL: colocando un número binario en sus entradas de datos(address), se obtiene un estado distinto en la salida correspondiente. en otras palabras, colocando mediante un decodificador BCD un cierto número en los terminales de entrada, digamos 0101, podremos hacer que la salida sexta pase a nivel bajo, lógico "0 Una aplicación muy importante es la facilidad de implementar una o mas funciónes lógicas usando un solo demultiplexor . Ejemplo 37 Implementar la función lógica Q (XYZ) = ∑(3,5,6,) y F(XYZ) = ∑(5,7) Teniendo presente que un multiplexor, por ejemplo de 8 salidas, el cual requiere de 3 lineas de “adress” o de control de direccionamiento, y que el valor de estas definen el valor de salida. Esto es, si en la entrada esta el valor de 000 a la salida estará activo el valor en Y0, si fuese 011, a la salida estará activo el valor de Y3 y así sucesivamente. Solución. Se asigna el valor de las variables XYZ a las entradas de direccionamiento en el mismo orden de peso. Esto es, asignamos X a E2, Y a E1, y Z a E0 y para implementar el circuito basta con sumar lógicamente los miniterminos presentes en la función booleana para Q y para F respectivamente. Figura 1 para el ejemplo 37b Implementacion de una función con demultiplexores. Cabe señalar que si se usa una compuerta comercial por ejemplo la 74138 el peso de las entradas de direccionamiento son CBA en este orden y ademas se debe de tener en cuenta que cuando su salida es activa presenta el valor de 0. Por lo que para hacer la suma lógica de los miniterminos se debera usar una compuerta NAND. Se deja al lector realizar el diagrama esquematico de la solucion.. Ejemplo 37 Se muestra una relación de las compuertas TTL más comúnmente usadas NAND 7400 CUADRUPLE DE 2 ENTRADAS 7410 TRIPLE DE 3 ENTRADAS 7420 DUAL DE 4 ENTRADAS 7430 UNA DE 8 ENTRADAS AND 7408 CUADRUPLE DE 2 ENTRADAS NOR 7402 CUADRUPLE DE 2 ENTRADAS 7427 TRIPLE DE 3 ENTRADAS OR 7432 CUADRUPLE DE 2 ENTRADAS NOT O INVERSOR 7404 SEXTUPLE CODIFICADORES 74185 BINARIO A BCD DECODIFICADOR 7446 BCD A 7 SEGMENTOS COMUN A POSITIVO + 7448 BCD A 7 SEGMENTOS COMUN A NEGATIVO 74145 BCD A DECIMAL 74138 UNA 3 ENTRADAS A 8 SALIDAS 74139 DUAL 2 ENTRADAS A 4 SALIDAS FLIP-FLOP 7474 DOBLE TIPO D, CON SET/RESET 7476 DOBLE TIPO JK CON SET/RESET CONPARADOR 7485 DE 4 BITS 74521 DE 8 BITS REGISTROS 7491 REGISTRO DE DESPLAZAMIENTO SERIE DE 8 BITS 7495 REGISTRO DE DESPLAZAMIENTO PARALELO DE 4 BITS 74194 REGISTRO UNIVERSAL DE 4 BITS CONTADORES 7492 CONTADOR DECIMAL “UP/ DOWN” PROGRAMABLE 7493 CONTADOR BINARIO “UP/DOWN” PROGRAMABLE ARITMETICO 7483 SUMADOR COMPLETO DE 4 BITS 74181 ALU DE 4 BITS 3.2.6 Flip-flops, relojes, registros, contadores A los circuitos que son capaces de tener dos estados estables, los cuales se generan según sea el valor de las entradas de excitación se les conoce como Flip-Flops, estos circuitos como se vera mas adelante son fundamentales para realizar circuitos secuénciales los cuales a su vez son la base para la construcción de circuitos de las computadoras. En este apartado se muestra la construcción de los circuitos con compuertas y sus aplicaciones se veran más adelante. Flip-Flops Para un mismo FLIP-FLOP existen dos tipos de circuitos, según sea su respuesta. Flip-Flop ,estos responden una señal de reloj durante los cambios de 1 a 0 lógico o de 0 a 1 lógico,según sea respuesta por flanco de subida o de bajada respectivamente, notar que se dice solo responde al momento del cambio Flip-flop de cerrojo ( latch ) o asincronos los que su salidas responden a una señal de relog durante todo el tiempo que permanesca el 0 o 1 lógico en sus entradas. Flip-Flop S-R (Set-Reset) Este dispositivo es similar al cerrojo S-R, la diferencia radica en la inclusión de una señal de reloj, que actúa como señal de confirmación del paso de los datos hacia el circuito principal, el cuál se encarga de memorizar los datos. Su representación en los sistemas digitales es la que se muestra en la figura Este tipo de flip-flop no es muy comercial así que no se darán mas detalles sobre este dispositivo en este apartado. figura 3.3 Flip-flop S-R Flip-Flop D (Data) El flip-flop D es muy similar al cerrojo D, y su diferencia radica en que la señal habilitadora (enable) es reemplazada por el mecanismo del flip-flop maestro/esclavo, el cual actualiza los datos cada vez que la señal de reloj tiene una transición de 0 a 1 o 1 a 0 dependiendo del tipo de flip-flop. La estructura del flip-flop D y su representación simplificada se muestran en la figura figura 3.4 Flip-flop D La tabla 3.3 es la tabla de verdad de exitacion de este flip-flop, la cual indica que el valor de la entrada D se trasfiere a la salida cuando ocurre un pulso de reloj. D CLK Qi+1 0 ↑ 0 1 ↑ 1 Tabla 3.3 Tabla de excitación del flip-flop D La forma de operación de este flip-flop es muy sencilla: o o Cuando D=0 y se presenta un cambio de 0 a 1 lógico en la entrada de reloj del flip-flop la salida Q=0. Cuando D=1 y se presenta un cambio de 0 a 1 lógico en la entrada de reloj del flip-flop la salida Q=1. En otras palabras, el dato en D se transfiere y memoriza en Q cada vez que se presenta una transición de 0 a 1 lógico en la señal de reloj (CLK); esta condición se conoce con el nombre de transición por flanco positivo. La condición complementaria a la anterior es cuando la transición es de 1 a 0 lógico, en este caso se dice que la transición se da por flanco negativo. A este flip-flop tipo D, también se le denomina Espejo pues la salida es el reflejo de la entrada. Flip-Flop D Preset-Clear Este flip-flop es similar al flip-flop D, excepto que este tiene dos entradas asincrónicas activadas en bajo llamadas Preset y Clear. Estas entradas como su nombre lo indican sirven respectivamante para poner en 1 y 0 la salida Q del flipflop independientemente de la señal de reloj. La configuración de este flip-flop y su representación abreviada se describen en la figura 3.5. figura 3.5 Flip-flop D Preset-Clear La gran parte de los Circuitos Integrados que contienen flip-flops vienen con entradas asíncrónicas de inicialización y borrado (Preset y Clear), comunmente representados con las abreviaturas PRE y CLR. Flip-Flop J-K Este flip-flop es una versión modificada del flip-flop D, y su aplicación es muy difundida en el Análisis y Diseño de Circuitos Secuenciales. El funcionamiento de este dispositivo es similar al flip-flop S-R, excepto que en este no se presentan indeterminaciones cuando sus dos entradas se encuentran en 1 lógico, si no que el flip-flop entra en un modo de funcionamiento llamado modo complemento, en el cual, la salida Q cambia a su estado complementario después de cada pulso de reloj. La configuración de este flip-flop y su representación abreviada se muestran en la figura 3.6. y en la tabla 3.4 se indican la tabla de exitacion de entrada y salida de este flip-flop. figura 3.6 Representación del flip-flop J-K Note que las entradas J y K controlan el estado de este flip-flop de la misma manera que en el flip-flop D. Cuando las entradas son J=1 y K=1 no generan un estado indeterminado a la salida, sino que hace que la salida del flip-flop cambie a su estado complementario. J K CLK Qi+1 0 0 ↑ Qi 1 0 ↑ 1 0 1 ↑ 0 1 1 ↑ Q i' Tabla 3.4Estados del flip-flop J-K Flip-Flop T (Toggle) Este flip-flop recibe su nombre por la función que realiza (Toggle) cambiando el estado de la salida por su complemento. Es una modificación del flip-flop J-K limitándolo a cumplir exclusivamente esta función, la cual se logra uniendo las terminales J y K como se muestra en la figura 5.5.7. figura 3.7 flip-flop tipo T La tabla de verdad de este flip-flop se limita a las líneas 1 y 4 del flip-flop J-K. Ejercicio 7 Se deja al estudiante hacer una investigación sobre las Compuertas comerciales Que existen en el mercado nacional. La principal aplicación de los flip-flop es en los circuitos secuenciales y por su importancia, para su estudio se asigna la unidad IV que se estudiara mas adelante. Circuitos Integrados para Relojes Como hemos señalado los flip-flops necesitan recibir una señal de reloj para poder cumplir su función en los circuitos secuenciales. Los circuitos mas conocidos para desempeñar la función de reloj son los llamados osciladores o generadores de pulso. Los osciladores son circuitos que cambian el estado de sus salidas permanentemente entre dos estados lógicos (1 lógico y 0 lógico). Por esta razón estos circuitos son útiles para generar señales de reloj para los circuitos secuenciales sincrónos. Existen varios osciladores que se pueden construir para generar señales de reloj, mediante el uso resistencias, condensadores, inversores y compuertas. En la Figura 3.8 se observan algunas configuraciones que se pueden implementar haciendo uso de estos elementos. El esquema de la figura 3.8 (a), es un circuito generador de pulsos sin rebote y opera de forma manual. En la posición (1) la salida será 0 lógico y cuando el interruptor se ubica en la posición (2) la salida es 1 lógico. En las figuras (b) y (c) se muestran dos circuitos generadores de pulso que se pueden implementar usando inversores y compuertas. La frecuencia de oscilación depende básicamente de los valores de la resistencia y el condensador. Para este tipo de circuitos se recomienda el uso de circuitos CMOS de la serie B, ya que estos tienen tiempos de conmutación menores. figura 3.8 Circuitos generadores de relog A continuación se estudiaran dos tipos de osciladores cuyo uso es muy difundido en Electrónica Digital. Se mencionaran los aspectos básicos sobre su montaje sin tratar de explicar su funcionamiento, dejando como ejercició para el estudiante analizar su operación. Oscilador con Disparador de Schmitt En la Figura 3.9 se observa la configuración de este oscilador. La salida V o es una onda aproximadamente cuadrada y su forma depende de los valores de R y C. En la Tabla 3.5 se observa la relación entre los valores de R y C con la frecuencia para tres tipos de integrados con inversores tipo Schmitt, junto con los rangos de valores que debe tener R para que el circuito oscile. figura 3.9 Oscilador con disparador de Schmitt Integrado Frecuencia Valor de R 7414 0.8/RC 74LS14 0.8/RC 74HC14 1.2/RC R 500 Tabla 3.5 Frecuencia de oscilación según R y C Es importante señalar que la estabilidad en el funcionamiento de estos circuitos en lo que se refiere a mantener la frecuencia de salida es no mejor de un 10%, por lo que en la practica se usan solamente si en la aplicación especifica no se ve afectada por esta limitacion. Ejemplo.39 – 1 Cual es la frecuencia de operación para un circuito de reloj como se muestra en la figura 3.9 oscilador con disparador de Smith si C = .01 µF y R = 500 ohms y se usa la compuerta 74LS14 Solucion: F = 0.8/RC = 0.8 / (500 X .01 X 10-6 ) = 0.8 / 5 X 10-6 = 0.16 X 106 = 160 Khz En la practica este valor podrá estar en 160 ± 16 Khz. Se deja al estudiante corroborar o desmentir esta afirmación. Multivibrador astable con CI-555 El CI-555 es un dispositivo de tecnología TTL que funciona de varios modos. En la Figura 3.10 observamos la manera de conectar los componentes al Circuito Integrado de forma que opere como un Multivibrador Astable. La frecuencia de oscilación de la señal de salida depende de los valores de las resistencias RA, RB y C. figura 3.10 Multivibrador astable con CI-555 La señal de salida de este circuito es una onda cuadrada de las características que se indican en la Figura 3.11, donde los tiempos t1 y t2 están dados por las siguientes expresiones: figura 3.11 Señal de salida del CI-555 El periodo y al frecuencia de esta señal están dados por: Para que el circuito oscile es necesario que se se cumplan ciertos rangos para los valores de las resistencias y el condensador, los cuales se relacionan a continuación. Es de observarse que este circuito 555 es muy versátil tiene una infinidad de aplicaciones, se deja al estudiante hacer una investigación documental acerca de cuales podrían ser. Ejemplo 39 – 2 de aplicacion Diseñar un circuito de relog para una frecuencia de 5 Hz. Con 3 ciclos en valor alto y 2 ciclos en valor bajo. Solucion Ttotal = t1 + t2 = 5 t1 = 0.693 RB x C = 2 y t2 = 0.693 (R1 + R2) C = 3 Sea RB = 10 000 ohms → C = 2 / 0.693 RB = 2 / 0.639 X 10 000 = 3.13 x 10 -4 = .0313 µF para el calculo de RA t2 = 0.693 (RA + 10 000) X 3.13 x 10 -4 = (R1 + 10 000) X 2.17 x 10 -4 = 3 → R1 = (3 – 2.17 x 10 -4 x 10 000) / ( 2.17 x 10 -4) = 0.83/2.17 x 10 -4 = 3,824.88 los valores serán: → R1 = 3,824.88 → 3.8 Kohms R2 = 10 000 → 10K C = 0.313 µF Figura para el ejemplo 39 Registros Son dispositivos para el almacenamiento, o manipulación de información binaria Existen diversos tipos de registros, dependiendo de la función que desarrollen: - Registros de almacenamiento simple. Su función es básicamente la de almacenar una información. - Registros de conversión serie-paralelo. Son registros que realizan la conversión de la información que accede a ellos en serie, a un formato en paralelo. - Registros conversión paralelo-serie. Son registros que realizan la función inversa a los anteriores, es decir, a la información que accede a ellos en paralelo, le dan formato serie. - Registros de desplazamiento. Son registros que permiten el desplazamiento de la información que almacenan. También suelen servir para las funciones anteriores. Registros de desplazamiento Los registros de desplazamiento realizan fundamentalmente dos funciones : rotaciones, y aplazamientos propiarnente dichos. - ROTACIONES. Pueden ser a la derecha o la izquierda. Se realizan en bucle cerrado y se pueden utilizar para analizar el estado de un bit que forma parte de una información, y cuyo acceso solo es posible en una posición determinada. Los registros que realizan esta operación se denominan registros en anillo (un caso particular es el de los contadores en anillo, cuando aprovechamos el desplazamiento para realizar una cuenta). Vamos a ver los diversos tipos de rotación. Rotación a la izquierda (ROL). Veamos aplicándolo a un acumulador del microprocesador 6800 (tiene registros de 8 bits, y los testea a través de un biestable C). figura 3.12 Rotación a la izquierda Después de ocho desplazamientos, todos los bits, que conforman el contenido del AccA, pueden ser muestreados cuando pasan por "C" (acarreo). Rotación a la derecha (ROR). En este caso la rotación se hace a derechas. Siguiendo con cl ejemplo anterior, tenemos: figura 3.13 Rotación a la derecha Nuevamente, después de ocho desplazamientos todos los bits, que conformam el contenido del AccA, pueden ser muestreados cuando pasan por "C". - DESPLAZAMIENTOS. Tenemos dos tipos de desplazamientos: el lógico y el aritmético, según se vean o no implicados elementos ajenos al propio registro. Vamos a ver algunos tipos de desplazamientos: Desplazamiento aritmético a la izquierda (ASL). Básicamente realiza la siguiente función: figura 3.14 Desplazamiento aritmético a la izquierda (ASL Un desplazamiento a la izquierda equivale a una multiplicación por 2 en el sistema binario. Desplazamiento aritmético a la derecha (ASR). Básicamente realiza la función siguiente: figura 3.15 Desplazamiento aritmético a la derecha (ASR) Desplazamiento lógico a la derecha (LSR). Equivale a una division por 2 en binario. figura 3.16 Desplazamiento lógico a la derecha (LSR). Aquí, vemos que entra un "O" exterior al registro. CONVERTIDORES PARALELO/SERIE: Algunas veces es necesario convertir datos paralelos a datos serie, y viceversa. Dicho proceso es llevado a cabo fácilmente usando un registro para almacenar los datos, y luego transfiriendo los datos a su salida en la forma deseada. Ejemplo40 Se deja al alumno hacer una investigación documental de cuales convertidores serie – paralelo y viceversa existen en la familia TTL y como es que la realizan. Contadores. Un contador digital es constituido exactamente en igual forma que un divisor de frecuencia. En efecto, el circuito divisor-por-diez es en el fondo un contador, porque cuenta hasta diez pulsos y da una salida; se repone y queda listo para repetir el procedimiento de nuevo. Si se colocan varios flip-flops tipo JK en cascada, que inicien en el binario CERO, un BURST de pulsos en serie, colocados en la entrada, dejará los flip-flops en estados tales que ellos indiquen en forma binaria la cantidad de pulsos que arribaron al terminal de entrada. Notemos de nuevo que cada etapa debe cambiar de estado solamente cuando la anterior pasa de lógica 1 a lógica 0. Cuando en electrónica se menciona la expresión BURST, que traducida significa "ráfaga", "reventar", "porción", se quiere dar a entender que esos pulsos se presentan como un tren definido, "como una cierta cantidad de vagones unidos entre sí", iguales y mensurables en su cantidad. (En el estudio de televisión en color se encuentra con mucha frecuencia esta palabra BURST, y se refiere a los 8 o más pulsos encargados de sincronizar los circuitos de crominancia, los cuales vienen a manera de "ráfaga de metralleta" incluidos dentro de la onda portadora de TV). Los contadores digitales son un medio muy práctico para determinar FRECUENCIA, si la entrada del contador es "abierta" a una señal de frecuencia desconocida, durante un tiempo exactamente controlado (recordemos que "frecuencia" es la cantidad de ciclos que transcurren durante un segundo de tiempo). Los medios-ciclos (half-cycles) positivos de la frecuencia desconocida son contados, y su cantidad en el período de conteo permite establecer la frecuencia. Si el lado complementario del JK flip-flop es usado para manejar al que sigue, entonces el contador es conocido como un BACKWARD COUNTER (contador hacia atrás); esto es, el arranca en 1111 y cuenta sucesivamente hacia abajo, 1110, 1101, 1100, etc. Este tipo de contador es muy práctico cuando se quiere determinar la DIFERENCIA entre una frecuencia desconocida y una frecuencia asignada. El contador puede ser pre-cargado con la frecuencia de entrada. El resíduo positivo o negativo , a la izquierda del contador es la diferencia. La figura 3.17 muestra un contador de 4 bits, implementado con cuatro flip-flops tipo T (Toggles), a partir de integrados JK, recordemos que en este caso no se tiene en cuenta las entradas J y K, por lo que se deben dejar "al aire", en lógica 1 (muchos integrados digitales están internamente hechos para que sus entradas queden automáticamente en nivel alto cuando son dejados "al aire" sus terminales). Hay muchas clases distintas de flip-flops contadores en circuito integrado IC. El módulo de un contador especifica la máxima cuenta que el alcanza antes de reciclar. Los contadores módulo 10 son muy populares porque ellos reciclan después de caer el décimo pulso de entrada, y por lo tanto proveen una manera fácil de contar en decimal. Ellos son a menudo llamados CONTADORES DE DECADAS BCD (Binario Codificado a Decimal), y siempre tienen solamente cuatro terminales de salida (representan desde el 0000 hasta el 1001). Los contadores que están diseñados para aprovechar al máximo los cuatro bits del word nibble (medio byte) de salida, se llaman contadores HEXADECIMALES (representan desde el 0000 hasta el 1111). Los contadores pueden tener una variedad de controles de entrada. Un contador típico, por ejemplo, se puede programar para que cuente hacia arriba o hacia abajo (Up/Down). Puede también tener entradas de control para regresar la cuenta a 0's, iniciar la cuenta en cualquier valor deseado, o para indicar los momentos en los cuales el contador debe trabajar. Estos últimos terminales son los habilitadores, o entradas ENABLE. Debido a que los contadores almacenan la cuenta acumulada hasta que llegue el próximo pulso clock, ellos pueden ser considerados STORAGE REGISTERS. Los circuitos integrados TTL contadores más comunes son 74190 Contador sincrónico Up/Down, BCD, programable ( de 0 á 9) 74191 Contador binario Sincrono Programable 74192 Contador sincrónico Up/Down BCD, programable (de 0 á 9) 74193 Contador sincrónico de 4 bits binarios, programable, Up/Down Hay operación sincrónica cuando se tienen todos los flip-flops "clocked”.. Simultáneamente, de tal forma que sus salidas cambien al mismo tiempo cuando lo requiera el proceso lógico director. suministren los datos simultánea y paralelamente en las salidas Q3 , Q2, Q1, y Q0 ejemplo 41 de aplicación Ejemplo 41: Con un contador comercial diseñar un circuito secuencial que cuente en binario en base 8.es decir del 0000 al 0111. SOLUCION: Escogemos el contador 74192, en figura 1 para el ejemplo 41 se muestra la tabla de su modo de operación, Para hacer el circuito contador de 0000 a 0111, es necesario que el contador este en modo “UP” que inicie en 0000 y que al llegar la cuenta a 0111 el contador se ponga a cero “reset” y siga contando. Para lograrlo se requiere únicamente que se ponga un circuito con una compuerta AND de 4 entradas como detector de 0111 a la salida del contador y que se envíe su salida a la entrada CLR del contador. Es importante observar que la señal de reset debe ser un pulso positivo para permitir que el contador no detenga la cuenta esto se logra pues al detectar el circuito la entrada 0111 se genera un pulso HIGH e inmediatamente se “resetea” el circuito permitiendo que el contador siga su cuenta. Para poder observar la cuenta se usa un reloj de 1 pulso por segundo. El circuito completo del contador se deja como ejercicio al alumno. ejemplo 42 de aplicacion Con un contador diseñar un circuito que cuente en forma descendente de 1100 a 0000, que tenga una entrada E1 de inicio, que en cualquier momento de la cuenta esta se pueda suspender con una entrada E 2 y reiniciar en 1100, pero si la cuenta llagara a 0000 el contador se detenga. Solucion Seleccionamos el contador binario sincrono programable 74193, su tabla de modo de control se muestra en la figura 1 ejemplo 42. Y ademas usamos el circuito 7474 que es un FF tipo D doble con “preset” y “clear”. su tabla de modo de control se muestra en la figura 2 ejemplo 42. La entrada E2 para suspender se genera con un circuito de “push buton” de tal manera que a su salida normalmente tenga el valor lógico de 1 y solo cuando se accione el interruptor W1 se produzca un valor lógico de 0, esta señal es conectada en LD’ , lo que provocara que cada vez que se accione el contador se pondrá en el inicio con el dato de 1100 que se deberá poner permanentemente en las entradas D, C, B, y A Usamos el primer FF con entrada de inicio E1 en la entrada “clear” en este mismo circuito conectamos a la entrada “preset” la salida de un cicuito detector de cero El circuito completo del circuito se deja al alumno como ejercicio. 3.3 Circuitos de Aritmética. CIRCUITOS ARITMÉTICOS. Representación de números con signo. Representación en signo-magnitud. Representación en complemento a uno. Representación en complemento a dos. Aritmética de sumas y restas en las diferentes representaciones. Sumadores y restadores de un bit. Semisumador y sumador completo. Semirrestador y restador completo. Sumadores y restadores de múltiples bits en paralelo. Sumador y restador binario. La propagación del acarreo: generadores de acarreo anticipado. Sumador-restador en signo-magnitud. Sumador BCD. Sumadores y restadores de múltiples bits en serie: el registro acumulador. Unidades aritmético-lógicas. Multiplicación y división binaria. Circuitos Aritméticos El diseño de sistemas digitales involucra el manejo de operaciones aritméticas. En esta lección se implementarán los circuitos de suma y resta de números binarios. 3.3.1 Sumadores. Sumador Medio El circuito combinacional que realiza la suma de dos bits se denomina sumador medio. La figura 3.17 muestra el símbolo lógico de sumador medio. En el circuito las entradas son A y B y la salida S corresponde a la suma y Cout al acarreo de salida (Ver lección 1.4.). figura 3.17 Símbolo lógico del sumador medio La tabla de verdad tabla 3.6 está dada por las reglas de la suma binaria. X Y Cout S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 Tabla 3.6 De verdad del sumador medio La salida obtenida a partir de la tabla de verdad es: X + Y = Cout S El bit de acarreo Cout es 1, sólo cuando A y B tienen el valor de 1; por tanto entre A y B se puede establecer una operación AND: Cout = A·B El bit de suma S es 1, sólo si las variables A y B son distintas. El bit de acarreo es 0 a no ser que ambas entradas sean 1. Por consiguiente, la salida S puede expresarse en términos de la operación OR – Exclusiva: S = A’·B + A·B = A El circuito se muestra en la figura 3.18 B 3.18 Circuito Lógico del Sumador Medio. Sumador Completo El sumador completo acepta dos bits y un acarreo de entrada y genera una suma de salida junto con el acarreo de salida. La tabla 3.9.2. muestra la tabla de verdad del sumador completo. Las entradas A, B y Cin denotan al primer sumando, el segundo sumando y el acarreo de entrada. Las salidas S y Cout representan a la suma y el acarreo de salida. A B Cin Cout S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 Tabla3.7 De verdad del sumador completo La salida S en la tabla de verdad corresponde a la operación OR- Exclusiva: S = A·B’·Cin’ + A’·B·Cin’ + A·B·Cin + A’·B’·Cin S = Cin’·(A·B’ + A’·B) + Cin ·(A·B + A’·B’) S = Cin’·(A·B’ + A’·B) + Cin ·(A’·A + A’·B’ + A·B + B·B’) S = Cin’·(A·B’ + A’·B) + Cin ·((A’ + B)·(A + B’)) S = Cin’·(A·B’ + A’·B) + Cin ·((A·B’)’·(A’·B)’) S = Cin’·(A·B’ + A’·B) + Cin ·(A·B’ + A’·B)’ S = (A B) Cin El mapa de karnaugh de la salida Cout se muestra en la figura 3.19 figura 3.19Mapa para la salida Cout de un Sumador Completo. La salida Cout está dada por: Cout = A·B + A·Cin + B·Cin El circuito se muestra en la figura 3.20. 3.20 Circuito Lógico del Sumador Completo. 3.3.2. Restador. Restador En la diferencia, cada bit del sustraendo se resta de su correspondiente bit del minuendo para formar el bit de la diferencia. El préstamo ocurre cuando el bit del minuendo es menor al bit del sustraendo, de tal forma que se presta un 1 de la siguiente posición significativa. La resta se implementa mediante un sumador. El método consiste en llevar al minuendo a una de las entradas y el sustraendo en complemento 2 a la otra entrada. Restador Medio El circuito combinacional que realiza la resta de dos bits se denomina Restador medio. El circuito tiene dos entrada binarias y dos salidas. La figura 3.21 muestra el símbolo lógico de Restador medio. En el circuito las entradas son A(minuendo) y B(sustraendo) y la salida D corresponde a la diferencia y P al préstamo de salida. figura 3.21 Símbolo Lógico del Restador Medio. 0-0=0, 1-0=0 y 1—1=1. El resultado es el bit de diferencia D. Si A<B se tiene 0-1 y es necesario prestar un 1 de la siguiente posición significativa de la izquierda. El préstamo agrega 2 al bit del minuendo de manera similar cuando en el sistema decimal se agrega 10 al dígito del minuendo. La tabla de verdad 3.8 está dada por las reglas de la resta binaria. A B P D 0 0 0 0 0 1 1 1 1 0 0 1 1 1 0 0 Tabla 3.9 De verdad del Restador medio. La salida D coincide con la operación OR- Exclusiva y se puede expresar de la siguiente forma: D = A’·B + A·B’ La salida P está dada por la suma de productos de los términos presentes en el renglón 2 de la tabla de verdad: P = A’·B El circuito se muestra en la figura 3.22 figura 3.22 Circuito Lógico del restador medio. Restador Completo El Restador completo realiza la resta entre dos bits, considerando que se ha prestado un 1 de un estado menos significativo. En la tabla 3.9. las entradas A, B y C denotan el minuendo, el sustraendo y el bit prestado. Las salidas D y P representan a la diferencia y el préstamo. A B C P D 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 Tabla 3.9 De verdad del Restador Completo. En las combinaciones del mapa donde C=0, se tienen las mismas condiciones para el sumador medio. El resto de condiciones se vieron en la lección 4 del capítulo 1. La función de la salida D de un restador es la misma que la salida de un sumador completo: D = A’·B’·C + A’·B·C’ + A·B’·C’ + A·B·C = (A B) Cin El mapa de karnaugh de la salida P se muestra en la figura 3.23 Figura 3.23. Mapa para la salida P de un restador completo La salida P está dada por: P = A’·B + A’·C + B·C El circuito se muestra en la figura 3.20 figura 3.20 Diagrama lógico de un restador completo 3.3.3 UAL, Unidad Aritmética Lógica. Unidad Aritmética y Lógica (ALU) Una unidad aritmética lógica puede realizar un conjunto de operaciones aritméticas básicas y un conjunto de operaciones lógicas, a través de líneas de selección. En inglés ALU significa Arithmetic Logic Unit (Unidad Aritmética Lógica). La figura 3.24. muestra el diagrama de bloques de una ALU. figura 3.24 Diagrama de bloques de una ALU Las cuatro entradas de A se combinan con las de B generando una operación de salida de cuatro bits en F. La entrada de selección de modo S2 distingue entre las operaciones aritméticas y lógicas. Las entradas de selección S0 y S1 determinan la operación aritmética o lógica. Con las entradas S0 y S1 se pueden elegir cuatro operaciones aritméticas (con S2 en un estado) y cuatro logicas (con S2 en otro estado). Los acarreos de entrada y salida tienen sentido únicamente en las operaciones aritméticas. El diseño de una ALU implica el diseño de la sección aritmética, la sección lógica y la modificación de la sección aritmética para realizar las operaciones aritméticas y lógicas. Sección Lógica Los datos de entrada en una operación lógica son manipulados en forma separada y los bits son tratados como variables binarias. En la tabla tabla 3.10. se listan cuatro operaciones lógicas OR, OR - Exclusiva, AND y NOT. En el circuito, las dos líneas de selección (S1, S0) permiten seleccionar una de las compuertas de entrada, correspondientes a la función Fi . S1 S0 Salida Función Fi 0 0 F=Ai+Bi 0 1 F=Ai OR i XOR 1 0 F=Ai·Bi AND 1 1 NOT F=A'i Tabla 3.10 Tabla de Función Lógica. El circuito lógico es una etapa de un circuito lógico de n bits. figura 3.25 Diagrama lógico de un circuito lógico de una ALU Sección Aritmética El componente básico de la sección aritmética es un sumador en paralelo Las operaciones aritméticas configuradas en el circuito aritmético se presentan en la tabla 3.12 En una ALU, la suma aritmética se puede implementar con un número binario en A, otro número en la entrada B y el acarreo de entrada Cin en un valor lógico 0. El resto de las funciones se enuncian en la columna descripción. Selección de Función Salida N Función S1 S0 Cin N F 0 0 0 0 A Descripción Transferir A 0 0 1 0 A+1 Incrementar A 0 1 0 B A+B Suma ó agregar B a A 0 1 1 B A+B+1 Suma con accarreo ó agregar B a A más 1 1 0 0 B’ A+B’ Agregar el complemento de 1 de B a A 1 0 1 B’ 1 1 0 Todos unos A-1 Decrementar A 1 1 1 Todos unos A Trasferir A A+B’+1 Agregar el complemento de 2 de B a A Tabla 3.12 De la funciones de un Circuito Aritmético La implementación de las funciones anteriores por medio de un circuito lógico sencillo se describe a continuación. El circuito se diseña bajo el precepto de intervenir cada entrada Bi para obtener las siguientes funciones: S1 S0 Ni 0 0 0 0 1 Bi 1 0 B i' 1 1 1 Tabla 3.13 Tabla del circuito para la entrada Bi La figura muestra el circuito. figura 3.26 Circuito para la tabla 3.13 Por medio de estas funciones se pueden lograr las funciones de la tabla 3.12 al agregar el número Ni (tabla 3.13) a la entrada A a través de un sumador en paralelo para cada etapa, teniendo en cuenta el valor de la entrada C in. El circuito combinacional aritmético se muestra en la figura 3.14. En la figura 3.26a., la entrada A se denomina Mi en el sumador completo. figura 3.26a Circuito aritmético Diseño de una Unidad Aritmética Lógica En el diseño de una ALU se deben seguir los siguientes pasos: 1. Diseñar la sección aritmética independientemente de la sección lógica. 2. Determinar las operaciones lógicas del circuito aritmético, asumiendo que los acarreos de salida de todas las etapas son 0. 3. Modificar el circuito aritmético para obtener las operaciones lógica requeridas. El diseño simple de una ALU se hace utilizando el sumador completo para generar las operaciones lógicas de la unidad. Por lo tanto es necesario introducir una variable de control adicional (S2), con el fin de seleccionar entre las operaciones lógicas y aritméticas. En este diseño, un valor S2 = 1 hace que el circuito efectúe operaciones lógicas. Recordando la salida de un sumador completo: F = (Ai Bi Cin A partir de esta ecuación, es posible obtener la función lógica requerida, utilizando la debida manipulación lógica. La función requerida se expone en la tabla S2 S1 S0 Ai Bi Cin 1 0 0 Ai 0 Función requerida Fi Ai OR 0 1 0 1 Ai Bi 0 1 1 0 A i B i' 0 1 1 1 Ai 1 Operación Sumador Completo 0 Ai i Manipulación Aplicar una función Ai+Bi OR Ai + Bi XOR Ai·Bi AND A'i NOT Salida Ninguna Ai Aplicar una función Ai·Bi OR Ai + Bi' Ninguna A'i Tabla 3.14 Tabla de obtención de las funciones lógicas con un sumador completo Partiendo de la tabla 3.12.4., las entradas Mi, Ni y Cini en un sumador completo, son equivalentes a las siguientes expresiones: Mi = Ai + S2·S1'·S0'·Bi + S2·S1·S0'·Bi' Ni = S0·Bi + S1·Bi' Cini = S2'·Ci La figura 3.27 muestra el diagrama de la unidad aritmética lógica de dos etapas. i figura 3.27 Diagrama lógico de una ALU Las doce operaciones generadas en el ALU se resumen en la tabla 3.15 la función en particular se selecciona a través de S2, S1, S0 y Cin. Las operaciones aritméticas son las mismas del circuito aritmético. Selección Salida F Descripción S2 S1 S0 Cin F 0 0 0 0 A Trasferir A 0 0 0 1 A+1 Incrementar A 0 0 1 0 A+B Suma 0 0 1 1 A+B+1 Suma con accarreo 0 1 0 0 A-B-1 Resta con préstamo 0 1 0 1 A-B Sustracción 0 1 1 0 A-1 Decrementar A 0 1 1 1 A Transferir A A+B OR 1 0 0 X B 1 0 1 X OR-Exclusiva 1 1 0 X A·B AND 1 1 1 X A’ Complementar A Tabla 3.16 Tabla de verdad de una ALU Ejemplo 42 Se deja al estudiante trabajo de investigación documental acerca del desarrollo histórico de las ALU .